【Verilog】一、Verilog的always使用 |

您所在的位置:网站首页 › verilog括号内输入输出顺序有要求吗 › 【Verilog】一、Verilog的always使用 |

【Verilog】一、Verilog的always使用

|

【Verilog】一、always使用 有不足请各位观众老爷批评指正~ 零、背景知识 组合逻辑:输出仅与当前输入有关(没有记忆) 时序逻辑:输出与当前输入、之前输入有关(有记忆) 一、Verilog HDL 模块的模板(仅考虑用于逻辑综合的程序) module(); output 输出端口列表; input 输入端口列表; //(1)使用assign语句定义逻辑功能 wire; assign=表达式; //(2)使用always块定义逻辑功能 always@() begin //过程赋值语句 //if语句 //case语句 //while,repeat,for循环语句 //task,function调用 end endmodule //(3)元件例化二、always使用 always时间控制:沿触发或电平触发 单个信号或多个信号(中间用关键词or连接) 1、沿触发 功能:常用于描述时序行为。e.g.有限状态机 always @(posedge a, negedge b)/*posedge:上升沿;negedge:下降沿。 Verilog1364-2001版本,关键词or可用,代替 */ begin …… end说明:两个沿触发的always块只要其中一个沿出现,就立即执行一次过程块 2、电平触发 功能:常用于描述组合逻辑行为 (1) always @( a or b or c) begin …… end说明:多电平触发时,只要a、b、c中任何一个出现从高到低或从低到高的变化,就执行一次过程块 (2) always @*//或写成always @(*) begin …… end说明:对其后面的语句块内所有输入变量都敏感,任何输入变量的变化都会触发条件 】来个练习 3、 always #5 b = ~b;//每隔5个单位时间触发一次条件产生周期为10的无限延续的信号波形 功能:描述时钟信号,并作为激励信号来测试所设计的电路 注:always period = ~period;此时无时序控制,会使仿真器产生死锁 三、关于always的一些说明 1、一个模块中可有多个always块,并行运作 2、若always块可综合,则表示的是某种结构;若always块不可综合,则表示的电路结构的行为 四、需要注意的地方 1、assign不能再always中使用 2、assign和实例应用可独立于过程块存在 //部分资料来自网络(CSDN的一篇文章,找到了会补上~)、《verilog数字系统设计教程》夏宇闻 |

【本文地址】

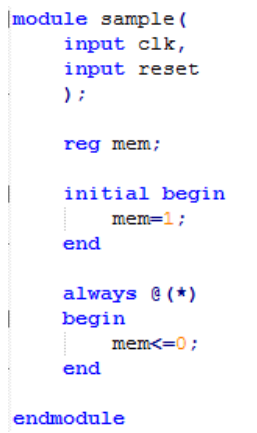

当clk和reset信号都处于下降沿时,mem会被清0吗? 答案是不会。 “always@()表示对其后面的语句块中出现的所有输入变量的变化是敏感的。”也就是对语句块中赋值符号右边的变量值的变化敏感,此题中always@()语句块中右值并不是变量,也就不会发生变化。

当clk和reset信号都处于下降沿时,mem会被清0吗? 答案是不会。 “always@()表示对其后面的语句块中出现的所有输入变量的变化是敏感的。”也就是对语句块中赋值符号右边的变量值的变化敏感,此题中always@()语句块中右值并不是变量,也就不会发生变化。