Verilog学习(SPI协议的Flash驱动控制) |

您所在的位置:网站首页 › verilog实现除以3 › Verilog学习(SPI协议的Flash驱动控制) |

Verilog学习(SPI协议的Flash驱动控制)

|

目录 一、SPI通信协议 1.1 SPI物理层 1.2 SPI协议层 二、实战 2.1 SPI控制FLASH实现全擦除代码编写 2.2 上板验证 一、SPI通信协议

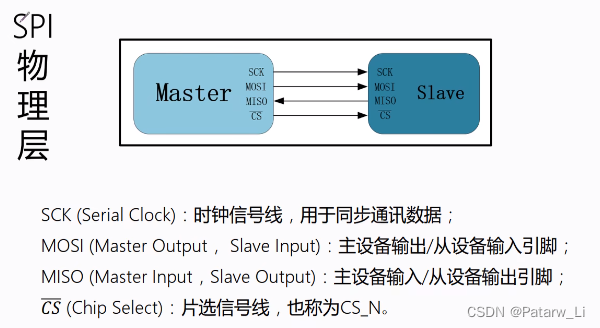

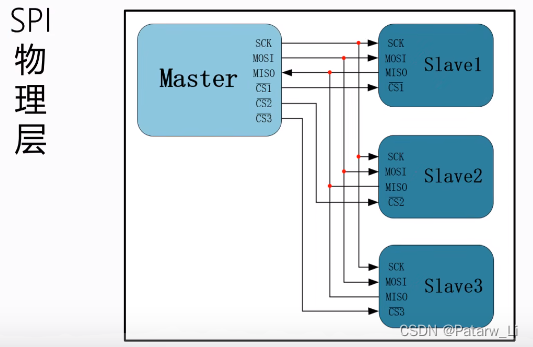

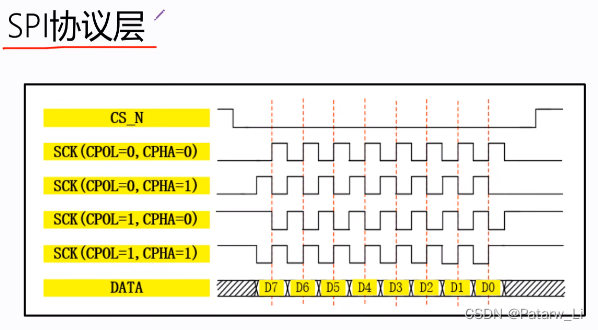

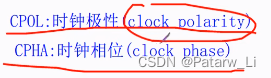

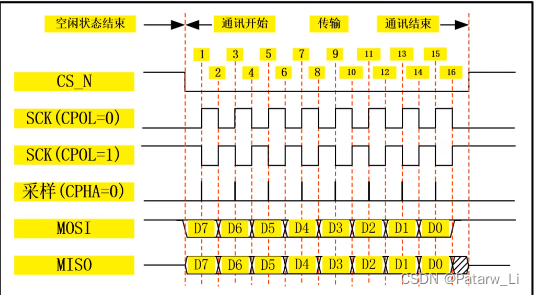

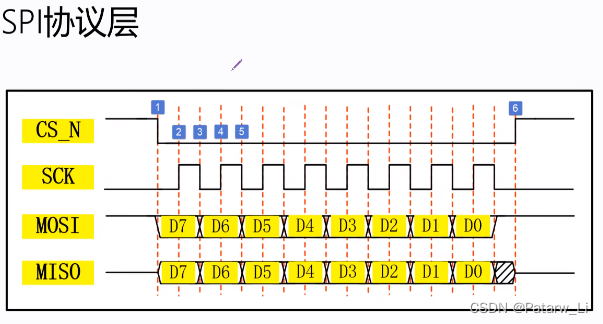

SPI通信模式为主-从模式 ,分为一主一从、一主多从: 片选线CS用于主机选择对应的从机进行通信,片选线置低电平为通信开始信号,被拉高则为开始信号。 1.2 SPI协议层SPI协议有四种通信模式(通过CPOL和CPHA控制), 其中CPOL控制当没有数据传输的时候SCK的电平状态;CPHA控制数据采样位置,为0的时候位置为奇数边沿,为1的时候为偶数边沿。 下图传输为高位在前,先传输高位,每次传输数据的个数没有限制。 程序的固化流程: 生成jic文件:

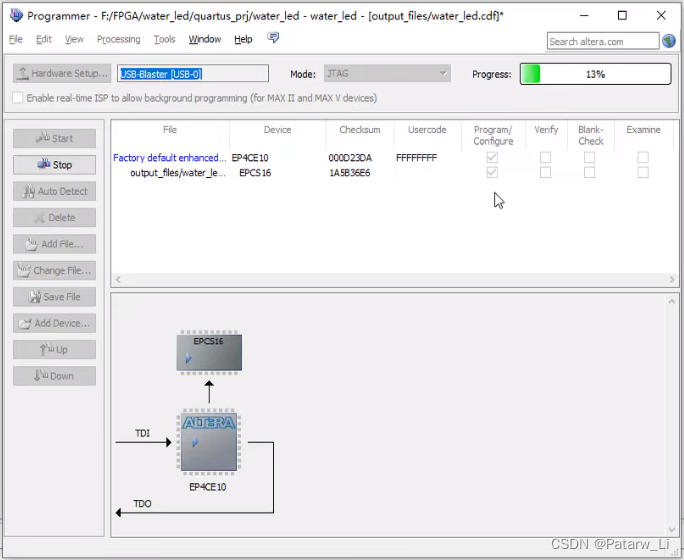

选择生成好的jic文件烧录:

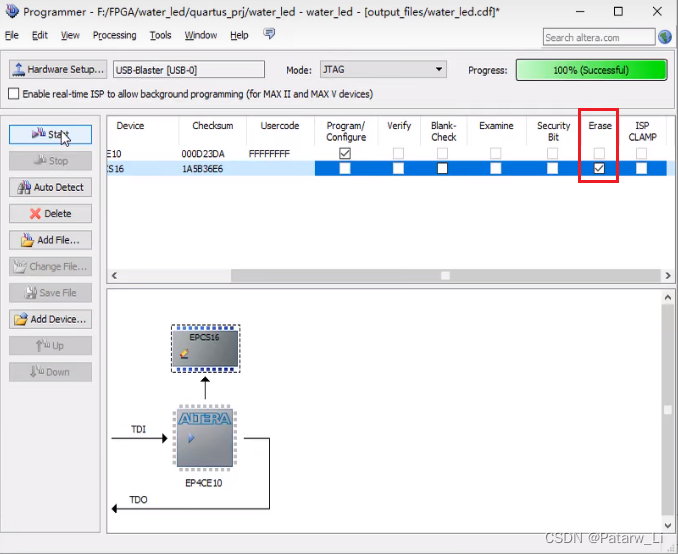

固化后的程序即使断电也不会丢失,如果想去除flash中的固化程序,可以进行全擦除操作。 第一种方法可以到下载器中进行全擦除:

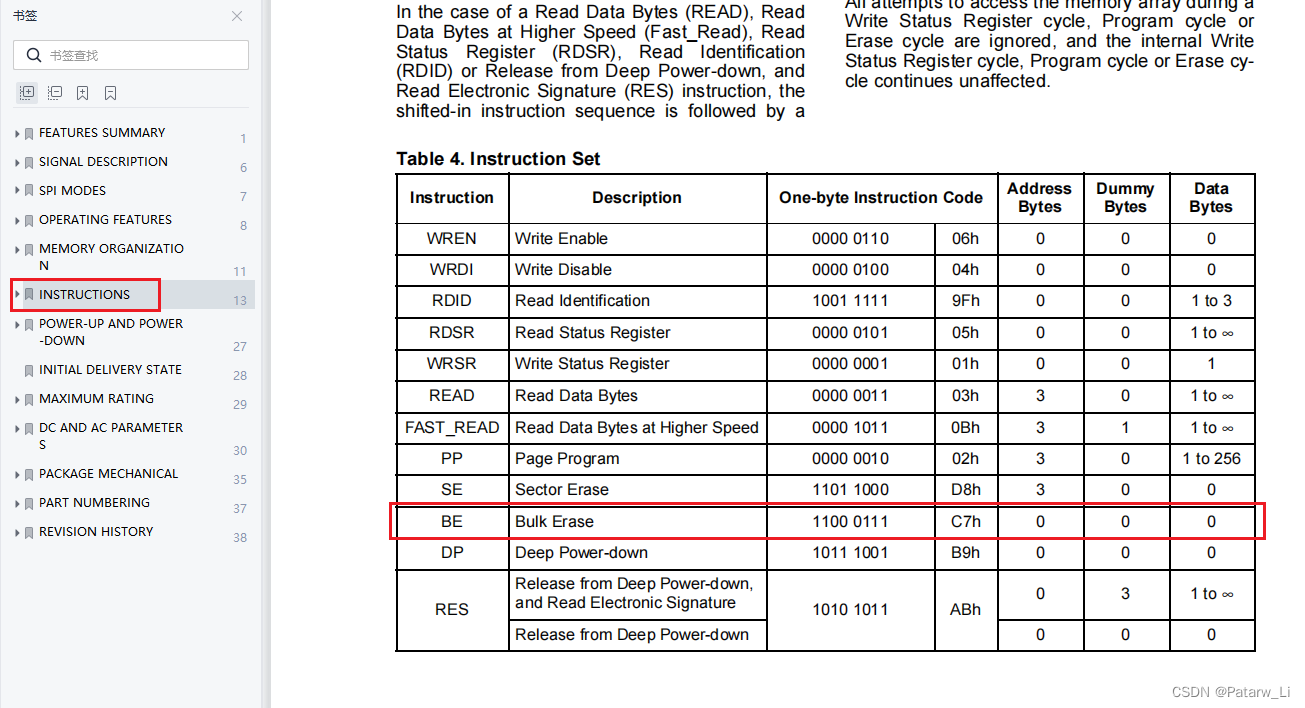

第二种方法就是我们要讲的,自己编写程序对flash芯片进行全擦除。 首先打开flash芯片的手册: 找到全擦除对应的指令BE(Bulk Erase):

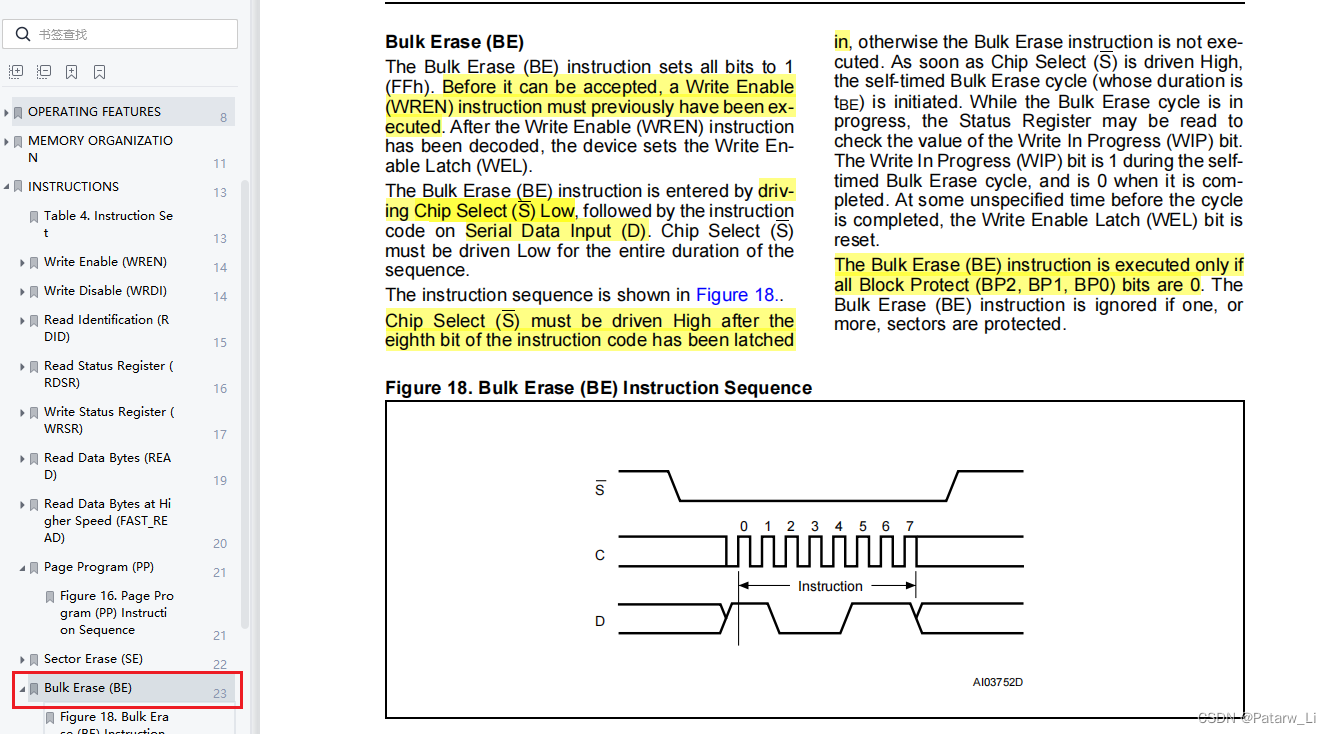

然后找到BE指令的介绍:

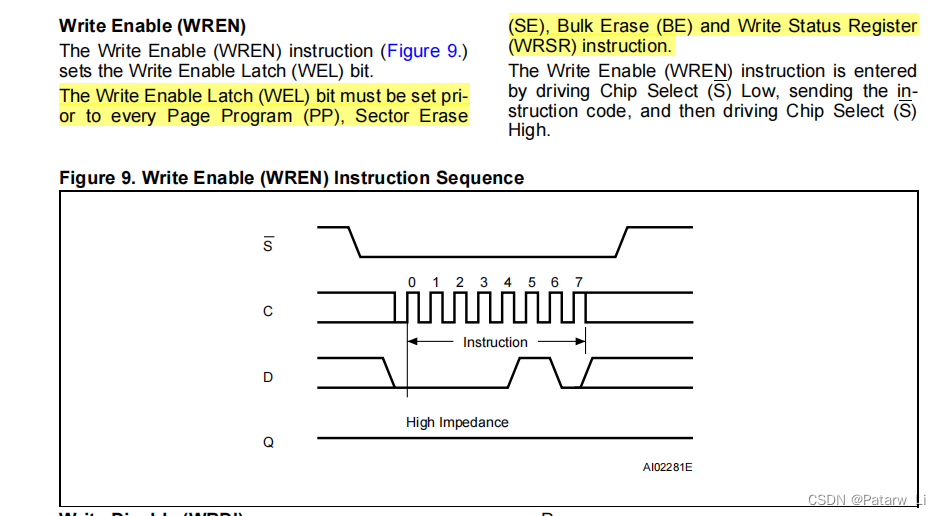

从介绍里面可以知道: BE指令会把flash芯片中的所有位设置为1。在执行全擦除指令之前,需要先执行一个写使能指令WREN。在BE指令发送的时候需要将片选信号然后查看一下写使能指令的信息:

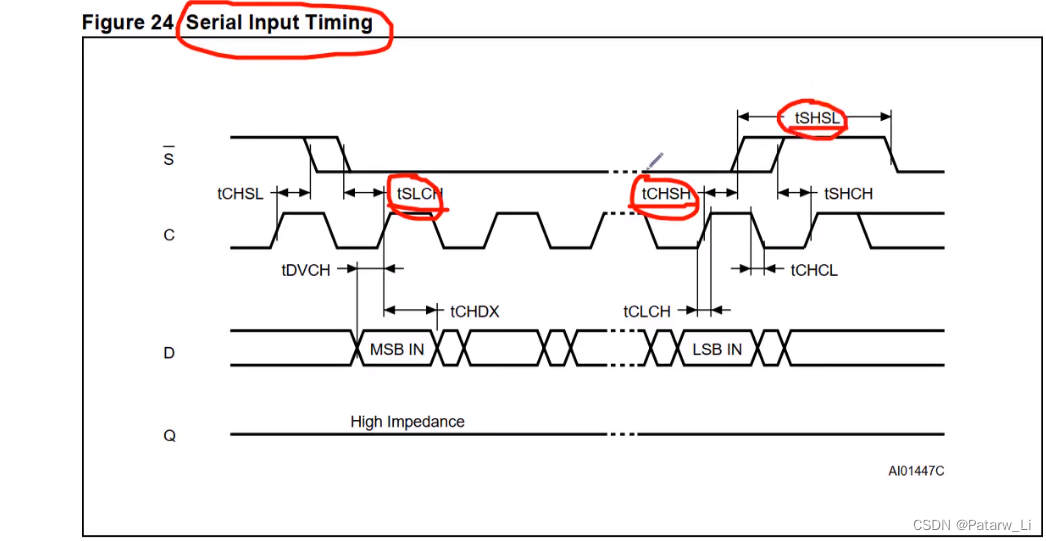

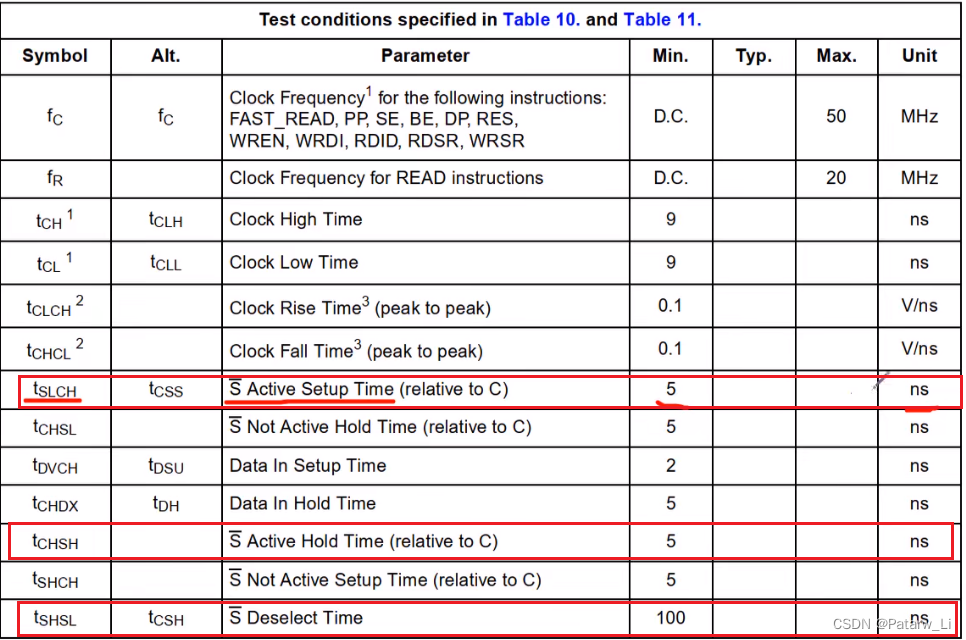

还有一个要注意的地方就是输入时序的问题,tSLCH、tCHSH、tSHSL这三个时间要注意:

tSLCH为从片选信号 tCHSH为从最后一个bit写入完成到片选信号 tSHSL为两个指令之间需要等待的时间,最小值为100ns。

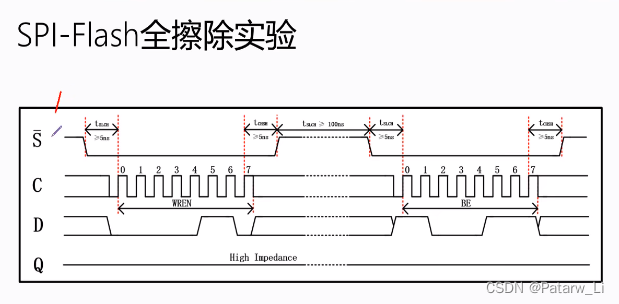

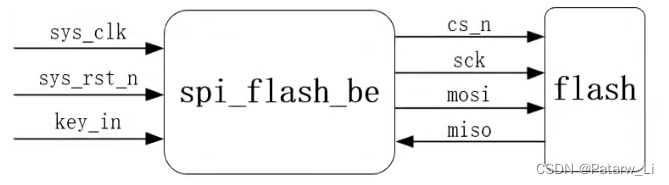

基于上面的内容我们可以得到我们实验的时序图: 实验顶层模块框图:

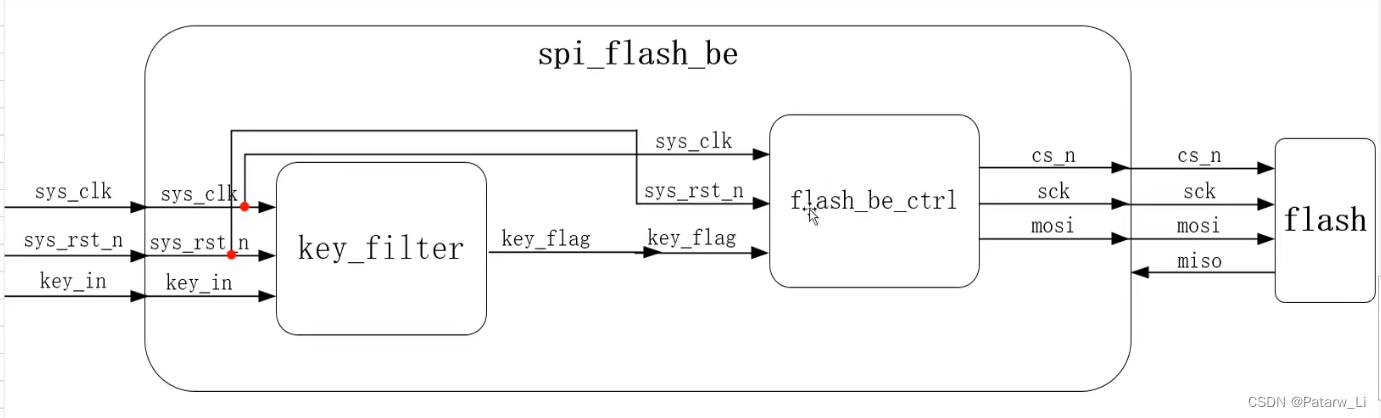

内部结构:

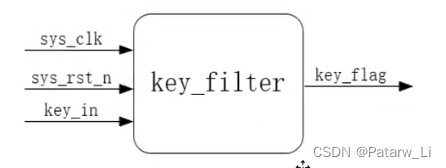

按键消抖子模块(为了简单这个按键消抖模块我就不做了,直接使用key_in控制):

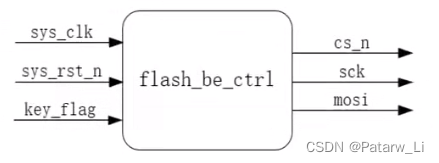

全擦除控制子模块:

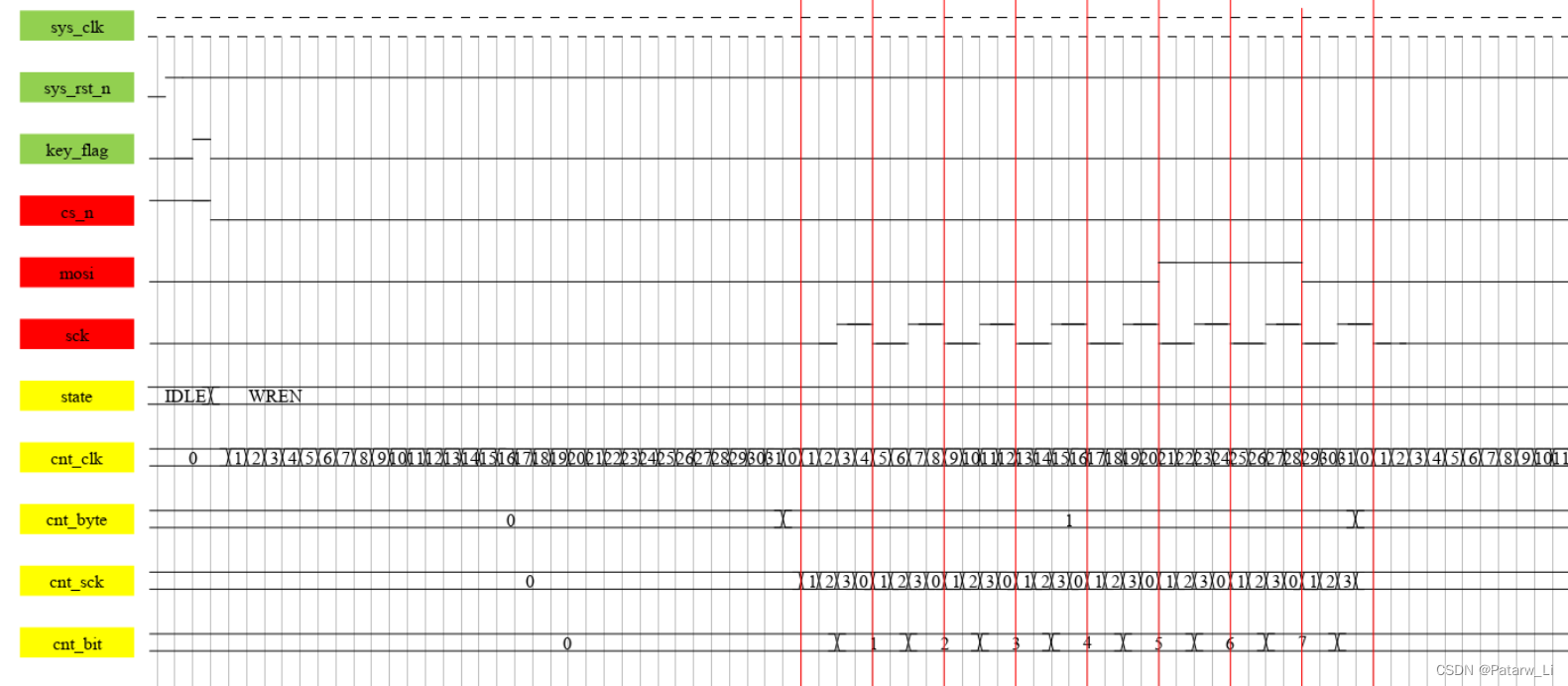

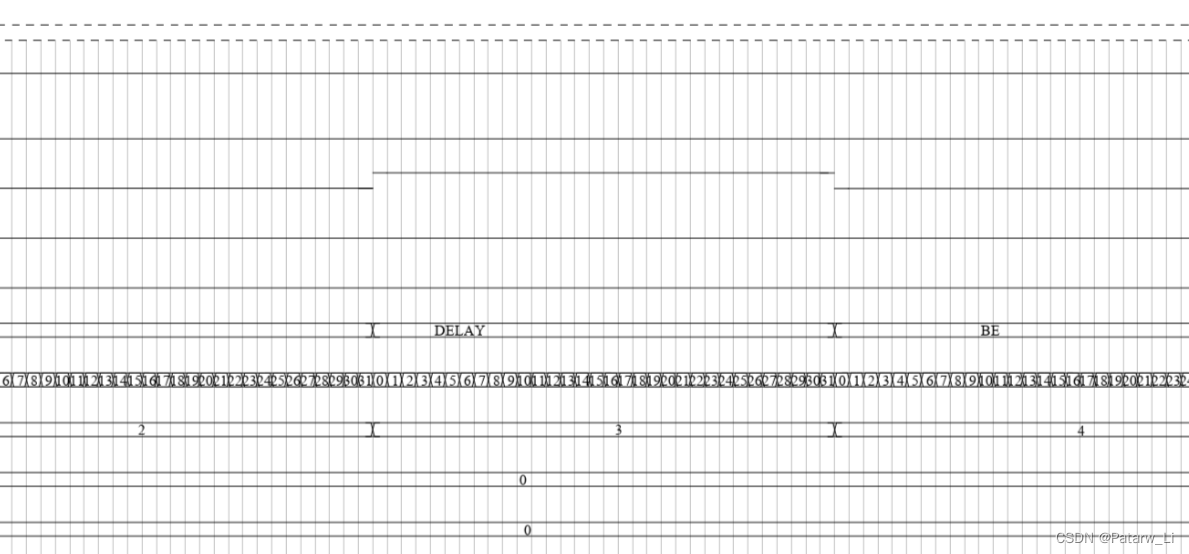

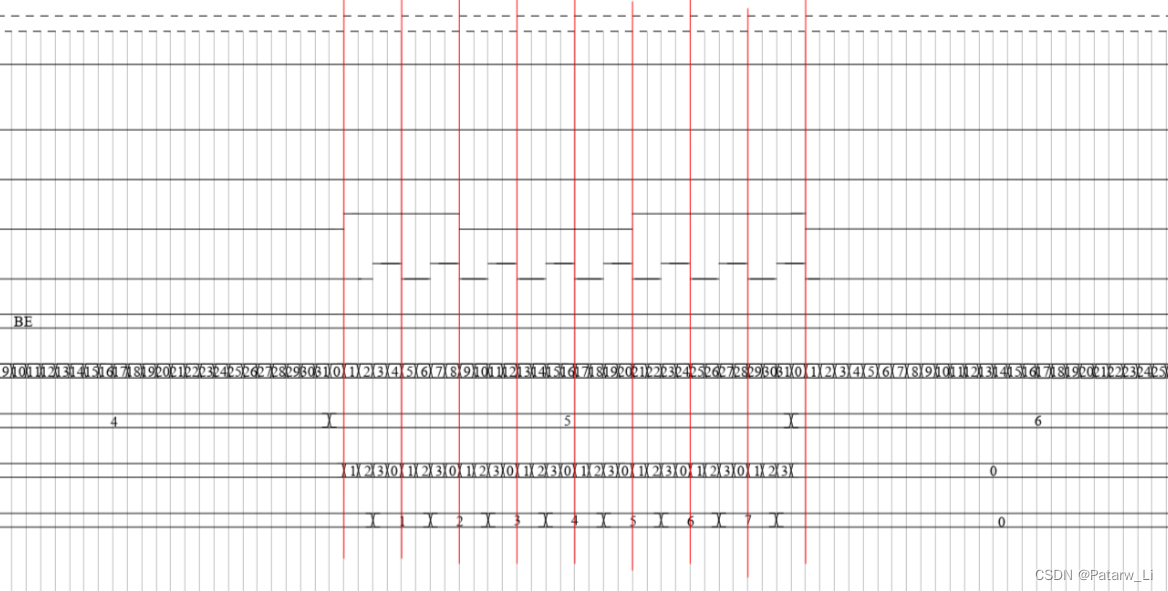

全擦除控制模块波形:

flash_be_ctrl模块verilog代码: module flash_be_ctrl( input wire sys_clk , input wire sys_rst_n , input wire key_in , //按键信号 output reg cs_n , //片选信号,低电平有效 output reg sck , //spi通信时钟信号,采用的是12.5Hz output reg mosi //主机输出的数据 ); parameter WREN_INS = 8'b0000_0110; parameter BE_INS = 8'b1100_0111; reg key_en; reg key_flag; reg [2:0] state; //状态机,0为闲置状态 reg [4:0] cnt_clk; reg [2:0] cnt_byte; reg [1:0] cnt_sck; reg [2:0] cnt_bit; //检测按键是否按下,生成key_flag信号,并且只检测一次 always@(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) begin key_en |

【本文地址】

今日新闻 |

推荐新闻 |