05 |

您所在的位置:网站首页 › verilog仿真时间调度 › 05 |

05

|

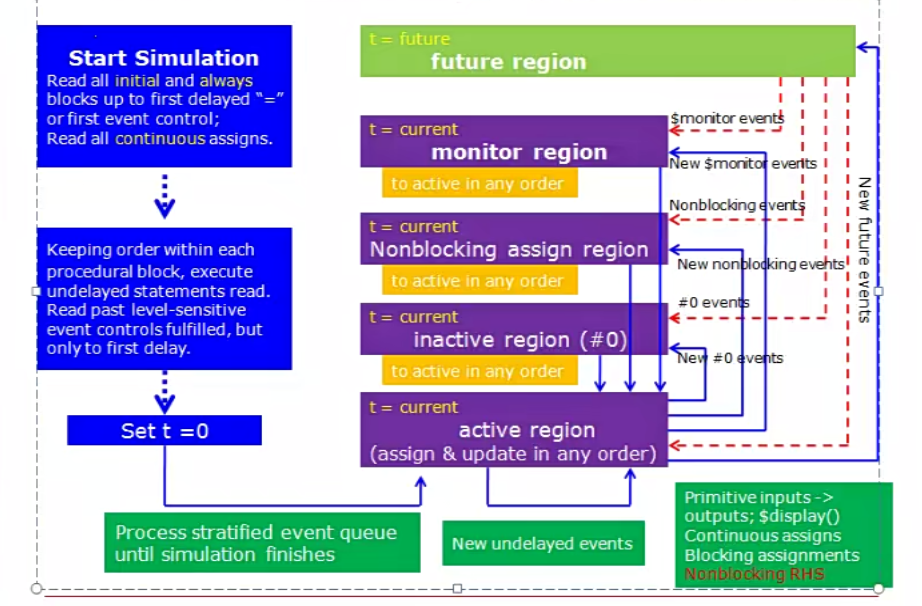

Verilog Simulation Event Queue

主要了解VCS是如何处理交给它的代码的 Verilog的仿真事件队列,介绍VCS如何处理交给它的代码。VCS是Synopsys公司的,支持多种语言。 1.Verilog 仿真事件队列Verilog内建仿真规范 IEEE1364,Verilog语言的仿真基于分层的事件队列 执行事件的队列 仿真时间的计算 Verilog仿真器先从没有延迟的事件开始,执行他们,然后把时间设为0,然后按照时间顺序依次执行各个事件。 Verilog语言规范没有规定当多个事件被安排在同一时刻来调度时,因该执行哪个。 只要在同一层次的事件,什么执行顺序都是可以的 在CPU的环境下,或者是说在软件的环境下,指令的执行是串行的。单核CPU是串行的,多核CPU是并行的。硬件电路与软件的区别就是并发的执行性。如何通过软件模拟硬件的并发性非常重要,仿真器仿真的时候,相同的代码交给不同厂商生产的厂商出品的仿真器,结果可能不同。 仿真器设计出来有一定的算法,首先按照一定的标准去做,有自己的内建实现标准。 设计师必须理解Verilog的分层仿真事件队列 2.VCS处理代码的流程

|

【本文地址】

VCS如何处理交给它的代码

VCS如何处理交给它的代码