CH340电路设计电压匹配和防止电流倒灌问题 |

您所在的位置:网站首页 › usb口供电最大电流 › CH340电路设计电压匹配和防止电流倒灌问题 |

CH340电路设计电压匹配和防止电流倒灌问题

|

CH340电路设计注意事项

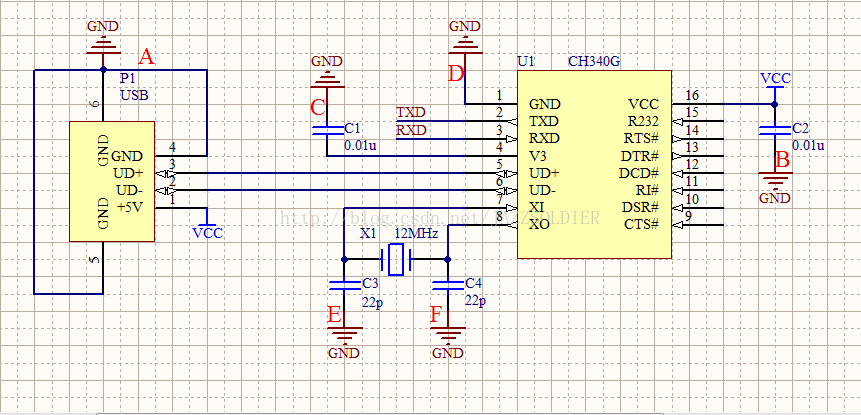

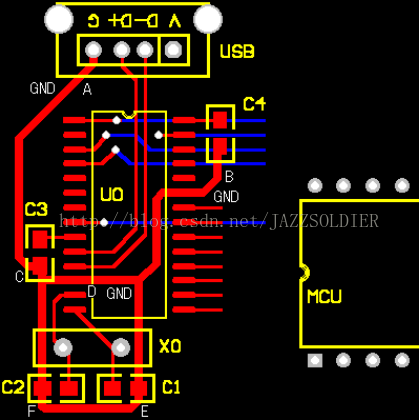

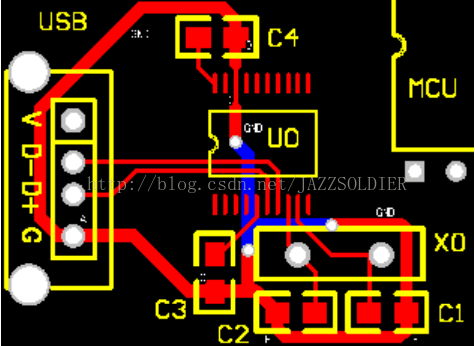

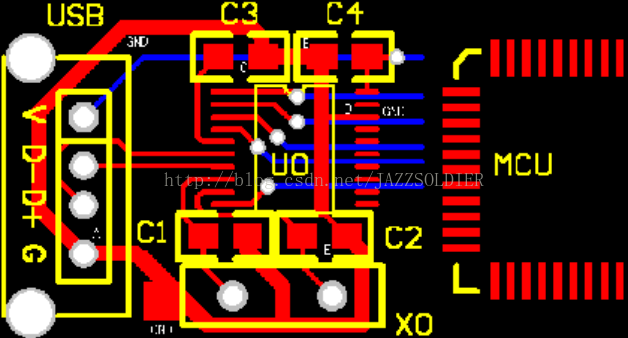

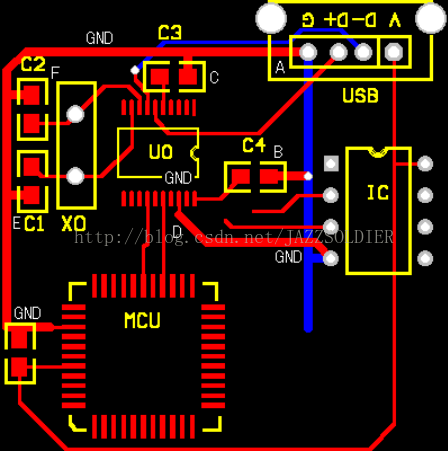

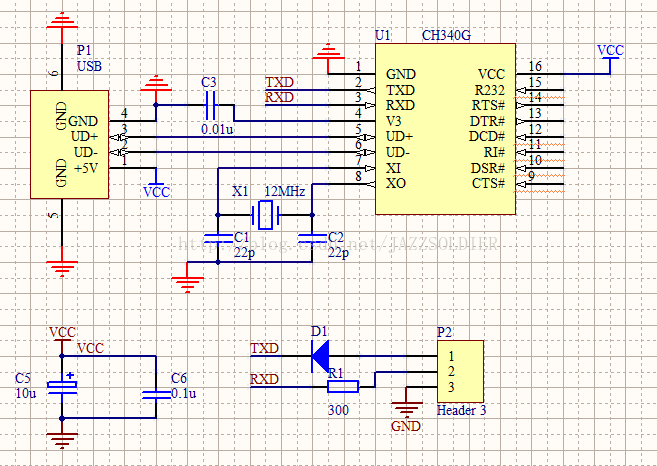

在前面两篇博客提到了CH340的电路设计以及芯片选型,本文将重点放在使用CH340芯片进行电路设计的一些细节与注意事项。 电压匹配问题CH340 芯片通过 USB 转换出来的 TTL 串口输出和输入电压是根据芯片供电电压是自适应的。也即,如果芯片是 5V 供电,那么串口输出和采样都是 5V;如果是 3.3V 供电,那么标准就成了 3.3V,因此在实际使用的时候,串口连接到的对端设备需要注意电压匹配的问题。其中在 5V 供电模式下,是可以与 3.3V 系统兼容的,反过来则不可以,如果 CH340 是 3.3V 供电,那么不可以接 5V 系统,会损坏芯片。另外如果对端是 1.8V 系统,那么是不能与 CH340 的 3.3V 模式兼容的,此时输出和采样会出错。最好加一些器件来升降压来进行电压匹配。因此设计时确认好对端串口电平范围,然后决定 CH340 工作在 3.3V 或者 5V 工作模式。在前面文章中也有提及,在电路设计原理上,5V 供电时芯片 V3 引脚需要接一个 104 电容到地,3.3V 供电时直接将 V3 脚与 3.3V 电源引脚短接就可以了。 防止电流倒灌问题在实际应用中,当 CH340 与其他 IC 譬如 MCU 等器件一同使用时,如果串口直连的双方器件有一方不需要供电工作时,要注意电流倒灌导致未供电的芯片继续工作的情况,或者是在串口下载场景中,当 MCU 需要复位以实现下载时,发现复位不成功,可能也是由于该原因造成的。因此,在电路设计中可以做如下改动来防止 CH340 与对端 IC 出现任何一方被倒灌电的情况。原理图如下: 也就是在 CH340 芯片的 发送引脚 TXD 上接一个反向二极管,如IN4148,然后再连接到对端 IC。在接收引脚上加一个限流电阻来防止对端 IC 对CH340 倒灌电。 通过反向二极管的原理是:在 CH340 发送数据时,发送高电平时二极管截止,但是由于对端 RXD 默认上拉也是高电平不会有采样问题,而发送低电平时二极管导通,对端 RXD 接收到低电平,因此可以正常通讯。并防止了 CH340 的 TXD 发送引脚将电流倒灌到对端 IC。 通过限流电阻的原理是:倒灌电流导致芯片工作甚至闩锁效应,是由于引脚电流过大超过了芯片设计时容忍的上限,导致芯片内部电路出现异常。因此加一个限流电阻就可以了,其他通讯场景也可以仿照此方法进行尝试。 CH340电流倒灌问题分析解决最近使用51单片机连接CH340G的板子来输出调试信息,出现了一个问题,经过一番折腾,最终解决了。 项目场景:

分析: 咨询了WCH官方,这才知道如果电路的一部分上电,而另一部分未上电,就会出现由于电平不匹配而产生的电流倒灌问题,而导致了后上电的单片机的初始状态出错,因此单片机程序无法运行。 解决方法:方法1:让CH340和单片机使用同一个电源,要么都用USB供电,要么都用其他电源供电。 方法2:在CH340芯片的引脚TXD上借一个反向二极管,然后再连接到对端IC。在接收端引脚上加一个限流电阻来防止对端IC对CH340的倒灌电。 方法3:换用CH343、CH9102等支持IO独立供电的芯片。 自带防电流倒灌USB转串口芯片CH340K发布啦http://club.szlcsc.com/article/details_39965_1_5.html#floor_5 为什么电脑端USB-B升级线 插入带电的开发板USB口导致电脑主机烧坏无法开机?电脑的USB vcc(5V)与CH340G的VCC(3.3v) 不一样 ,二者供电不同。 求解答:? 请问谁熟悉USB转串口芯片CH340T,单独供电为何无法工作?https://ask.csdn.net/questions/7396602 P2 是 USB 端口,USB 总线包括一对 5V 电源线和一对数据信号线,通常,+5V 电源线是红色,接 地线是黑色,D+信号线是绿色,D-信号线是白色。USB 总线提供的电源电流最大可以达到 500mA,一 般情况下,CH340 芯片和低功耗的 USB 产品可以直接使用 USB 总线提供的 5V 电源。如果 USB 产品通 过其它供电方式提供常备电源,那么 CH340 也应该使用该常备电源,这样可以避免与 USB 电源之间的 I/O 电流倒灌。如果需要同时使用 USB 总线的电源,那么可以通过阻值约为 1Ω 的电阻连接 USB 总线 的 5V 电源线与 USB 产品的 5V 常备电源,并且两者的接地线直接相连接。 晶体以及电容的选用对于 CH340 系列需要外部晶振的芯片,在选用晶振时如果选择 12MHz 的石英晶体,那么旁路电容选择 22pF 的独石或高频瓷片电容。如果选用的低成本陶瓷晶体,那么旁路电路的容量必须用该晶体厂家的推荐值,一般情况下是 47pF。对起振困难的晶体,建议电容数值减半。如果仍然无法起振,最好参考一下选用晶振的官方推荐电容值。 芯片CH340的V3引脚作用V3 的引脚除了在不同电压供电模式下接法不同,对于电容数值选用也是需要注意的。V3 引脚的电容用于内部电源节点退耦,来改善 USB 传输过程中的 EMI,通常容量在 4700pF 到 0.1uF 范围,建议容量为 0.01uF,即 103 电容。 提高工作稳定性和抗干扰在这里参考了沁恒官网提供的文章《USB芯片的电路及PCB设计的重要注意事项》。需要设计 USB 电路的工程师可以下载下来参考学习。 因为 USB 信号属于模拟信号,所以在 CH340 等 USB 芯片内部包含数字电路和一些模拟电路,另外,USB 芯片中还包含时钟震荡及 PLL 倍频电路,电路的公共地端在芯片内部已经连接在一起并连接到芯片的 GND 引脚。 如果 USB 芯片有时工作不正常、或者 USB 数据传输随机性失败、或者抗干扰能力差,那么就应该考虑 USB 芯片是否稳定工作。影响 USB 芯片工作稳定性的几大因素有: 时钟信号不稳定 - 这是主要原因,下面将详细分析。时钟信号受干扰 - 解决方法:PCB 设计时尽量不再晶体及震荡电容附近走线,尤其是不要走继电器、电动机等带有瞬时冲击电流的电源线和强信号线;在晶体及震荡电容周边布置 GND 铺铜屏蔽干扰;将晶体外壳接地(任何需要晶体工作的电流都可以这样设计);或者使用有源晶振等。USB信号受干扰 - 解决办法:PCB 设计时使 USB 信号线 D+ 与 D- 平行布线,最好在两侧布置 GND 铺铜,减少干扰。使用符合 USB 规范的带屏蔽层的传输线,不能使用普通排线或者非 USB 线缆。 时钟信号不稳定解决时钟信号不稳定通常是 PCB 布线中 GND 走线不佳。参考下图,该图适用于 USB 类芯片,图中有 6个接地点,分别是 A、B、C、D、E、F,设计电路及 PCB 时应该尽量避免这 6 个 GND 点之间存在电压差(主要是指数字电路中的高频毛刺电压,也就是数字噪声)。 解决方法是: 1.尽量缩短这 6 个点之间的距离; 2.类似模拟电路设计中的单点接地; 3.大面积 GND 铺铜及 GND 多点过孔 VIA 降低高频信号阻抗。图中最关键的是 E 点、F 点与 D 点之间不能存在高频毛刺电压差,可以用示波器探头接 D 点测量时钟输入端 XI 引脚的 12MHz 时钟波形是否有抖动。 参考PCB设计下图适用于 CH375 或 CH374 或者 CH341 等 GND 引脚紧靠 XI 引脚和 XO 引脚的 USB 芯片,比较容易走线。 下图适用于 CH372/CH374 等 GND 在时钟脚对侧的 USB 系列芯片,此时 GND 引脚借助过孔 VIA 及冗余 GND 线连接时钟振荡电路等。 下图适用于 CH372/CH374 等 GND 远离 XI 引脚和 XO 引脚的 USB 芯片,GND 走线和时钟信号线都比较短,时钟信号受到 GND 屏蔽保护。 下图中 USB 芯片 CH372 的引脚 D 点远离电容 C1 和 C2 的 GND 端 E 点 和 F 点,并且 C1 和 C2 的 GND 端与单片机 MCU 的 GND 连接,所以 MCU 的数字噪声将被引入 CH372 的 XI 引脚和 XO 引脚。建议改为:在 C1 和 C2 的 GND 端与 CH372 的 GND 引脚之间连接短线甚至断开 MCU 的GND(实际上这几个 GND 之间仍然是物理相通的)。 客观地讲,CH372、CH375、CH341 等 USB 芯片时钟的稳定性要求较高,稍有不稳定就会影响 USB 传输甚至不工作。因此,类似于下图的设计,强烈建议改进 PCB 布线以提高稳定性。 以上就是在 CH340 或者 USB 芯片电路设计时经常遇到的问题了,实际应用中还会有很多未提及的问题出现,当然也有相应的解决方案,譬如进行对电路进行电气隔离和增加电流保护,提升 ESD 性能等。 |

【本文地址】

今日新闻 |

推荐新闻 |

问题描述: 当我把CH340G的USB端接在电脑上用USB供电时,然后给单片机上电,单片机程序就无法启动了。

问题描述: 当我把CH340G的USB端接在电脑上用USB供电时,然后给单片机上电,单片机程序就无法启动了。