System Verilog 语法1 |

您所在的位置:网站首页 › ufc比赛日程表 › System Verilog 语法1 |

System Verilog 语法1

|

$display:

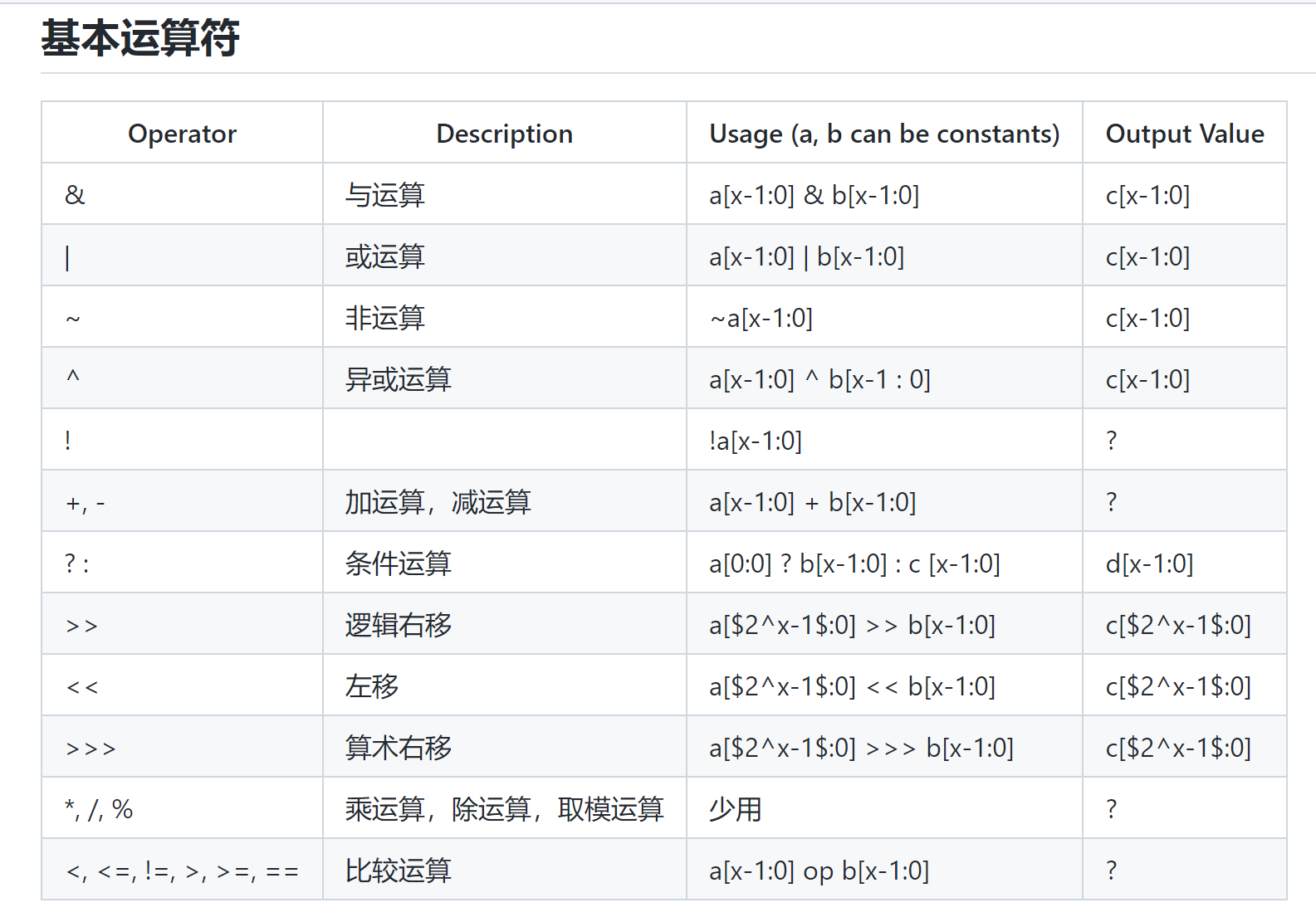

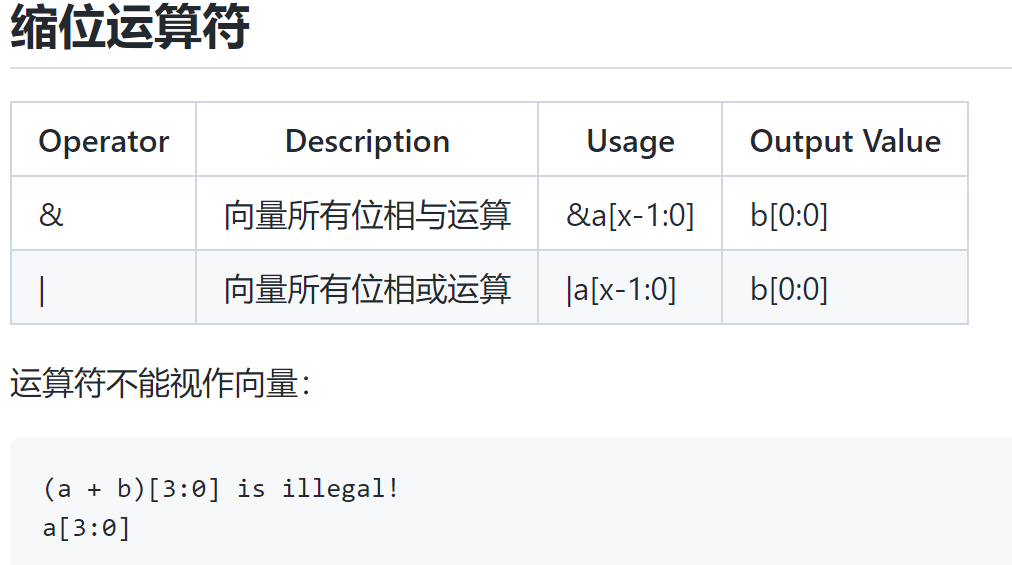

作用是控制台输出信息 $display("Start simulation") //显示字符串 $display("data_play = %h hex", 100) //显示data_play的16进制数(或者其他进制) $display("Simulation time is %t", $time) //显示仿真的时间 常数 变量:SV 中的 logic 数据类型和 Verilog 中的 reg 类型是一样的,可以互换使用,更多的是兼容 wire 类型。 // 常数 16'habcd // 16位二进制位宽,---- ---- ---- ----,代表的数是十六进制abcd // 变量 logic a; // 1bit logic [3:0]b; // 4bit logic [31:0][31:0]c; // 32x32bit // logic 不分wire reg logic [31:0] a, b, c; assign c = a & b; 数组声明 初始化 '{ } //一维数组 int a[0:15]; //16个整数 【0】...【15】 int b[16]; //16个整数 【0】...【15】 只给出数组宽度就是大端模式 int c[15:0]; //16个整数, a和b是一样的,c与其相反 //多维数组 int a[0:7][0:3]; int a[8][4]; a[7][3] = 1; // '{ } int a[4] = '{0,1,2,3}; //对4个元素分别赋值0-3。 a[0]=0; a[1]=1; a[2]=2; a[3]=3; int a[4:0] = '{0,1,2,3}; //a[3]=0; a[2]=1; a[1]=2; a[0]=3; int b[4]; b = '{0,1,2,3}; //先声明,后赋值 b[0:2] = '{0,1,2}; //部分赋值 int c[5] = '{5{8}}; //5个值全赋值为8 int d[5] = '{6,7,default:1}; //{6,7,1,1,1} 动态数组 int dyn[]; //声明动态数组 dyn = new[5]; //分配5个元素,此时动态数组的宽度为5 dyn = new[20](dyn); //重新分配20个元素,并将原dyn的值赋给新的dyn dyn = new[100]; //分配100个元素,原先的值已丢弃(释放) int dyn[] = '{0,1,2,3}; //声明动态数组,宽度为4,并赋值如下:dyn[0]=0;dyn[1]=1;dyn[2]=2;dyn[3]=3; 队列{ } // 队列的初始化不需要 '{ },而是 { } int q[$]; int qq[$] = {1,2,3,3,2,1};队列函数 push_front、push_back、pop_front、pop_back // push_front、push_back、pop_front、pop_back这四个函数只实用于队列,不能用于其他数组 int q2[$] = {1,2}; int q1[$] = {7,8,9}; q1.insert(1, q2); //q1为{7,1,2,8,9}。在q1的第1位上插入q2 算术左移-逻辑左移、算术右移、逻辑右移:算术左移和逻辑左移一样都是右边补0, 逻辑右移很简单,只要将二进制数整体右移,左边补0即可, 算术右移符号位要一起移动,并且在左边补上符号位,也就是如果符号位是1就补1符号位是0就补0。 逻辑右移 // 整体右移,左边补0 >>> 算术右移 运算符:

always_comb内部每条语句都是阻塞赋值语句。不能出现电路语句(assign) always_comb有以下性质: 内部覆盖性 对外原子性 always_comb begin a = 1'b1; b = a; a =1'b0; c = a; end // 电路输入:1'b1;1'b0; // 右边(1'b1;1'b0; a)除去左边(a,b,c) // 电路输出:(a,b,c)//左边 // 运行结果 a=1'b0, b=1'b1, c=1'b0, assign a = b; always_comb begin b = 1'b1; c = a; b = 1'b0; end // 先 always_comb 得: c = a, b = 1'b0; 再assign得:a = b = 1'b0; c = a = 1'b0 // 于是 a=1'b0, b=1'b0, c=1'b0, assign a = b; always_comb begin b = 1'b1; c = b; b = 1'b0; end // 先 always_comb 得: c = b = 1'b1; b = 1'b0 再assign得:a = b = 1'b0; // 于是 a=1'b0, b=1'b0, c=1'b1, always_comb case unique casecase块内没有优先级,并行比较 // unique case always_comb begin b = 1'b0; unique case (a[3:0]) 4'd1: begin b = 1'b1; end 4'd0: begin b = 1'b0; end default: begin end endcase end priority casecase块内有优先级,串行比较 (依次比较) always_comb begin priority case (1'b1) a[3]: begin end a[2]: begin end default: begin end endcase end // 相当于: /* always_comb begin if(a[3]) begin end else if(a[2]) begin end else if() begin end end */ always_comb if 和 forif if和else用于条件判断 always_comb begin b = 1'b0; if (a[3]) begin b = 1'b1; end else if (a[2]) begin b = 1'b0; end else begin end endfor for在always_comb中,会被解释为循环展开。 logic [15:0]a; logic [3:0] b; always_comb begin b = '0; for (int i = 15; i >= 0; i--) begin if (a[i]) begin b = i[3:0]; break; end end end always_comb begin for (int i = 0 ; i = n) break; end end always_comb begin for (int i = 0; i a_nxt, b_nxt}; end end always_comb begin a_nxt = a; // 不属于触发器的逻辑,写在always_comb 阻塞赋值 unique case(a) 4'd3: begin a_nxt = 4'd2; end default: begin end endcase end typedef自定义类型 // typedef 已有类型 新类型; typedef logic[31:0] word_t; // 新类型为word_t, 32位的logic组成一个word_t typedef logic[5:0] entry_t; // 新类型为entry_t, 6位的logic组成一个entry_t typedef entry_t[31:0] table_t; // 新类型为table_t, 32个的entry_t组成一个table_t word_t a, b; assign b = {a[15:0], a[31:16]}; table_t table1; // logic [31:0][5:0] assign table1[1] = '0; assign table1[0][1] = '0; 结构体 struct // type definition 打包 typedef struct packed { logic [3:0] alufunc; // control_t[4] logic mem_read; logic mem_write; logic regwrite; logic [3:0] reg_addr; // control_t[0] } control_t; // control_t是结构体的名字 // variable declaration control_t control; // 结构体声名 // 解包 logic regwrite; assign regwrite = control.regwrite; // 也可以assign regwrite = control[0] 索引 control.regwrite // using structs without typedef 也可以的定义结构体写法 struct packed { logic [3:0] alufunc; logic mem_read; logic mem_write; logic regwrite; } control_without_typedef; typedef struct packed { ..... } pipeline_decode_t; pipeline_decode_t p, p_nxt; always_ff @(posedge clk) begin p // [3:0]可以多,不可以少 ALU_ADD, ALU_AND, ALU_SUB } alufunc_t; // 使用 alufunc_t alufunc; // 变量声名 // 定义2 enum logic [3:0] { ALU_ADD, ALU_AND, ALU_SUB } alufunc_without_typedef; // 定义 typedef enum logic [1:0] { STATE_0, STATE_1, STATE_2 } state_t; // 使用 state_t state, state_nxt; // 变量声名 always_ff @(posedge clk) begin if (~resetn) begin state |

【本文地址】