Systemverilog |

您所在的位置:网站首页 › systemverilog可以做设计吗 › Systemverilog |

Systemverilog

|

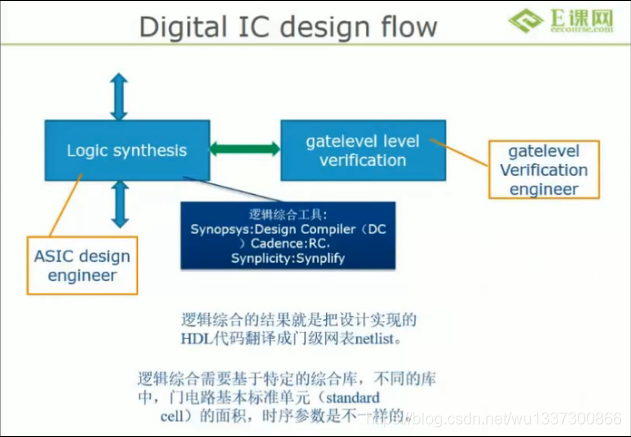

数字IC设计流程

1.确定芯片的具体指标 2.系统级设计:系统建模语言对各模块描述 3.前端设计:RTL,RTL仿真,硬件原型验证,电路综合 4.后端设计:版图设计,物理验证,后仿真 具体指标: 物理指标:制造工艺、裸片面积、封装 性能指标:速度、功耗 功能指标:功能描述、接口定义 VNC |

【本文地址】

今日新闻 |

推荐新闻 |

RTL——netlist(网表):逻辑综合 synsoy:design compiler PR:布局布线place complay synopsys: ic compiler(AP:auto place and r)

RTL——netlist(网表):逻辑综合 synsoy:design compiler PR:布局布线place complay synopsys: ic compiler(AP:auto place and r)

2.asic设计流程

2.asic设计流程  RTL:寄存器:时序器件、统一受时钟控制 半工艺流程:调用工艺厂商的门级网表 逻辑综合:时序约束文件(SDC文件);库文件;RTL Coding; 网表——版图:Auto P&R

RTL:寄存器:时序器件、统一受时钟控制 半工艺流程:调用工艺厂商的门级网表 逻辑综合:时序约束文件(SDC文件);库文件;RTL Coding; 网表——版图:Auto P&R