静态时序分析(STA) |

您所在的位置:网站首页 › sta分析困难 › 静态时序分析(STA) |

静态时序分析(STA)

|

一 OCV for Setup Checks

由于时钟和数据路径可能受到OCV的不同影响,因此定时验证可以通过使发射和捕获路径的PVT条件略有不同来建模OCV效应。 STA可以通过降低特定路径的延迟(derating the delays of specific paths)来包括OCV效应,也就是说,通过使这些路径更快或更慢,然后用这些变化来验证设计的行为。 单元延迟(cell)或导线延迟(wire)或两者都可以降低,以模拟OCV的影响。

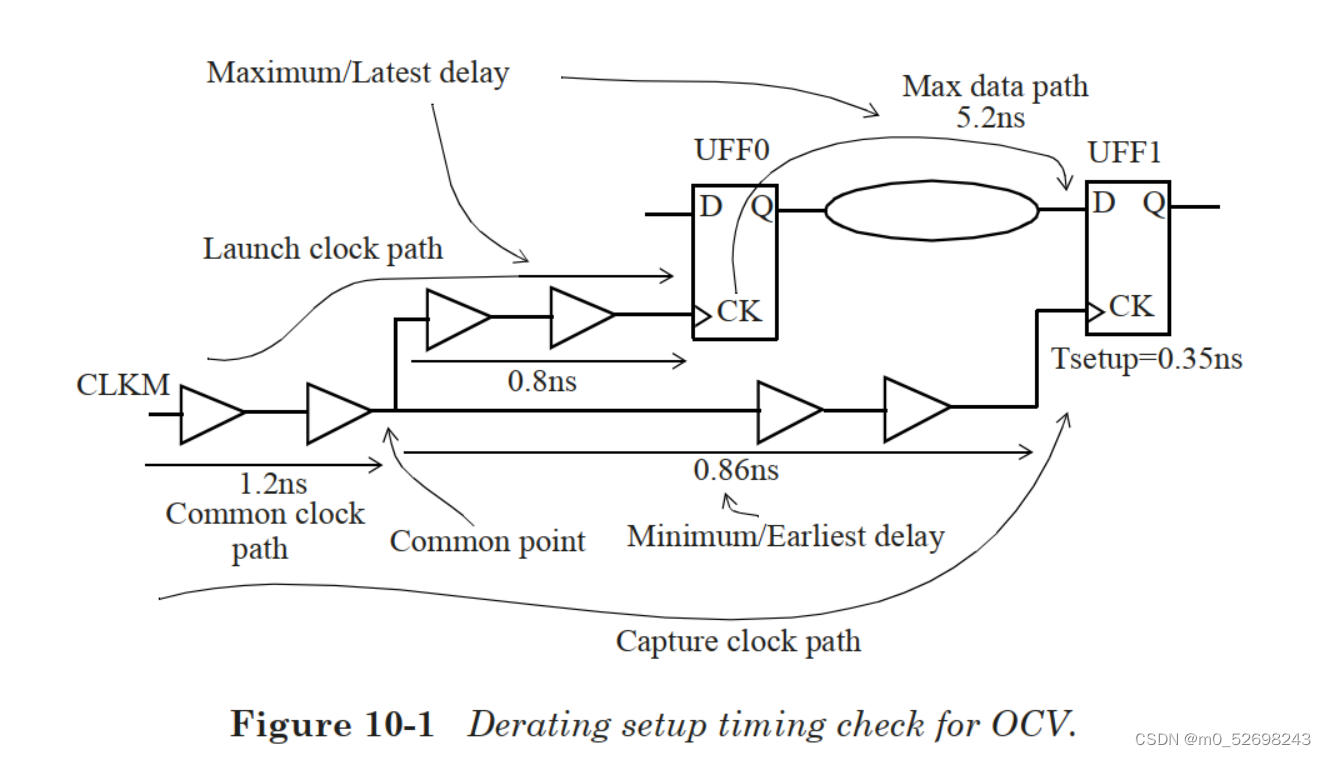

The worst condition for setup check occurs when the launch clock path and the data path have the OCV conditions which result in the largest delays, while the capture clock path has the OCV conditions which result in the smallest delays. setup timing check

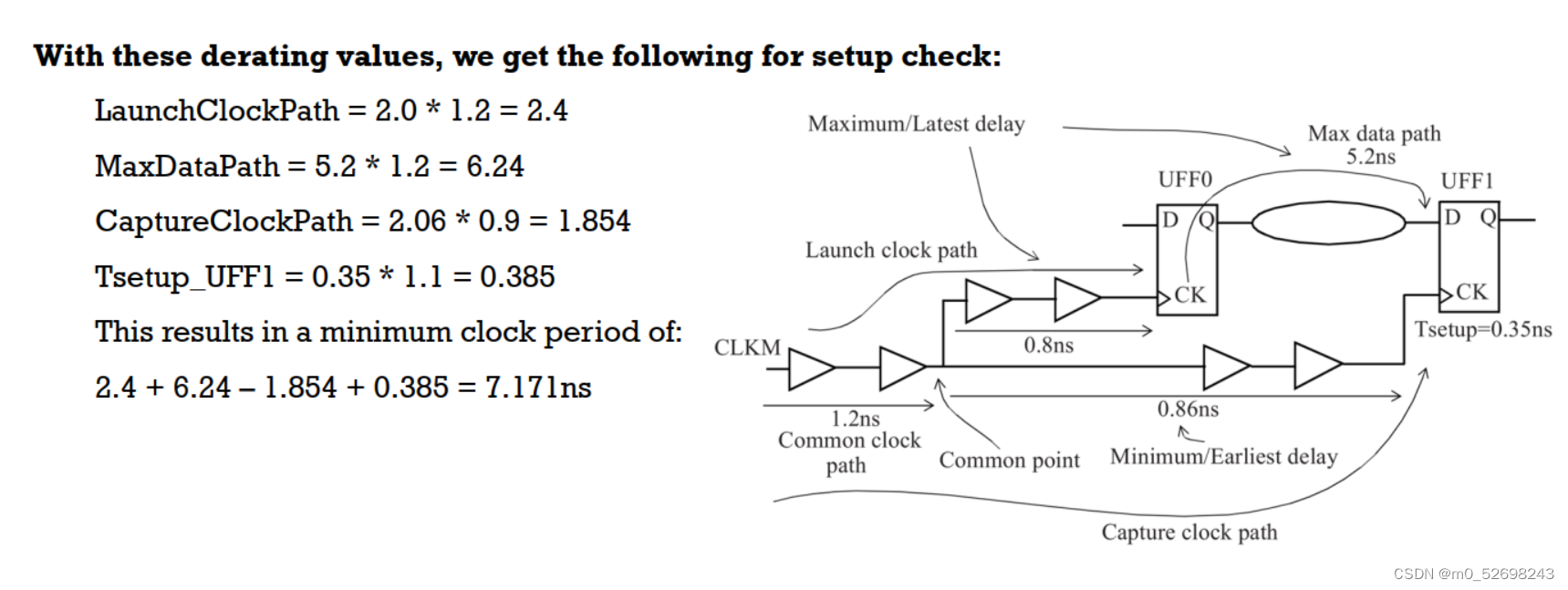

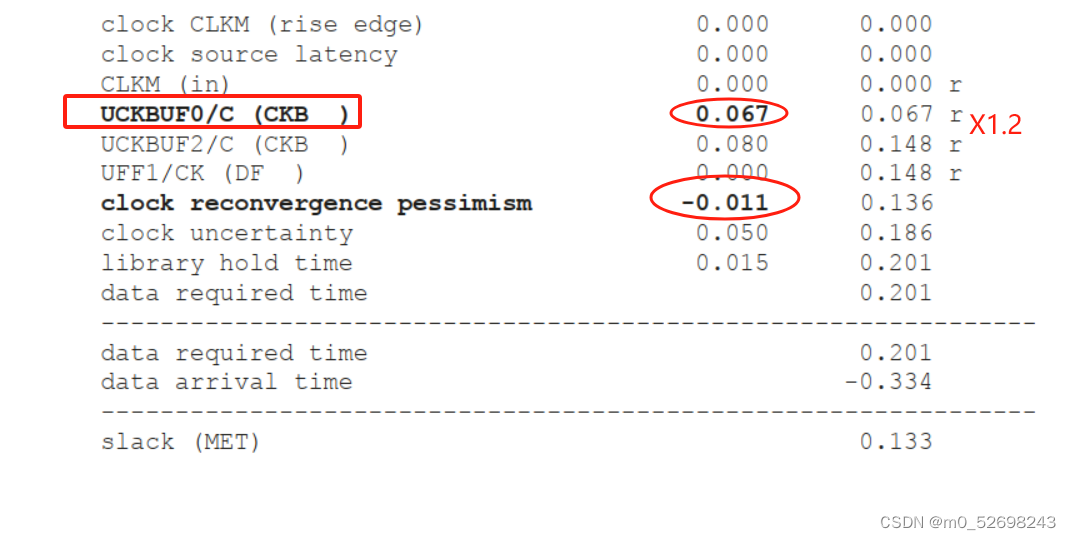

set_timing_derate -early 0.8 #Derate the minimum/shortest/early paths by -20%(提速20%) set_timing_derate -late 1.1 #derate the maximum/longest/latest paths by +10%. 1.Long path delays (for example, data paths and launch clock path for setup checks or capture clock paths for hold checks) are multiplied by the derate value specified using the -late option. 2. Short path delays (for example, capture clock paths for setup checks or data paths and launch clock paths for hold checks) are multiplied by the derate values specified using the -early option. If no derating factors are specified, a value of 1.0 is assumed. 注意:降额因子(derating)统一适用于所有网络延迟(net)和单元延迟(cell)。 如果应用场景要求单元和网络的降额因子不同,则可以在set_timing_derate规范中使用-cell_delay和-net_delay选项。 set_timing_derate -cell_delay -early 0.9 set_timing_derate -cell_delay -late 1.0 set_timing_derate -net_delay -early 1.0 set_timing_derate -net_delay -late 1.2 现在应用derate例子 set_timing_derate -early 0.9 set_timing_derate -late 1.2 set_timing_derate -late 1.1 -cell_check(建立时间更严苛一点)

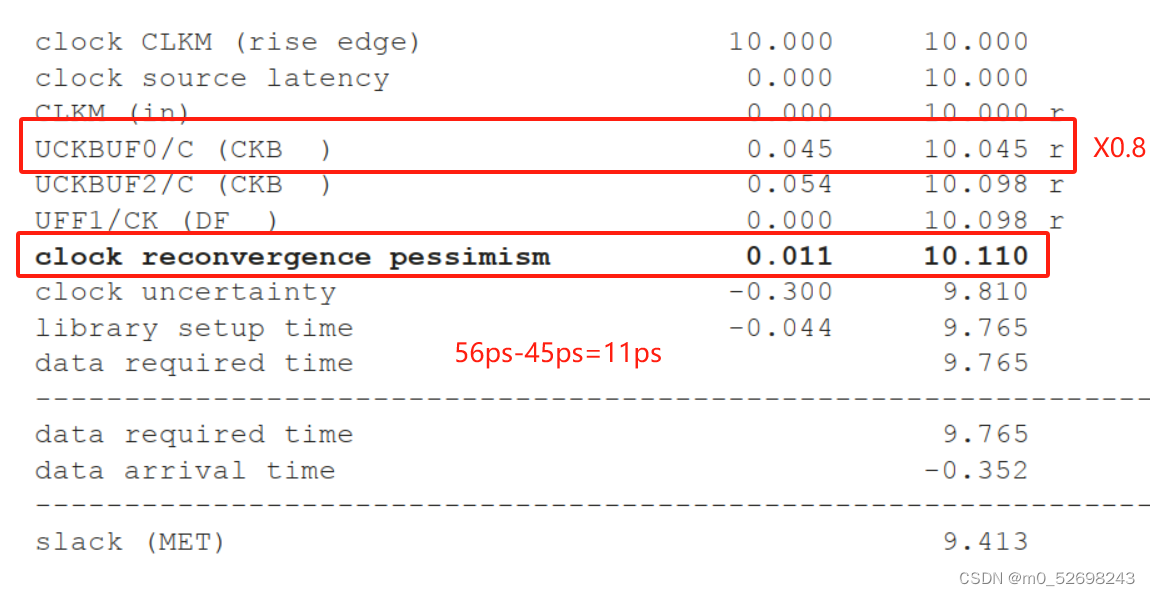

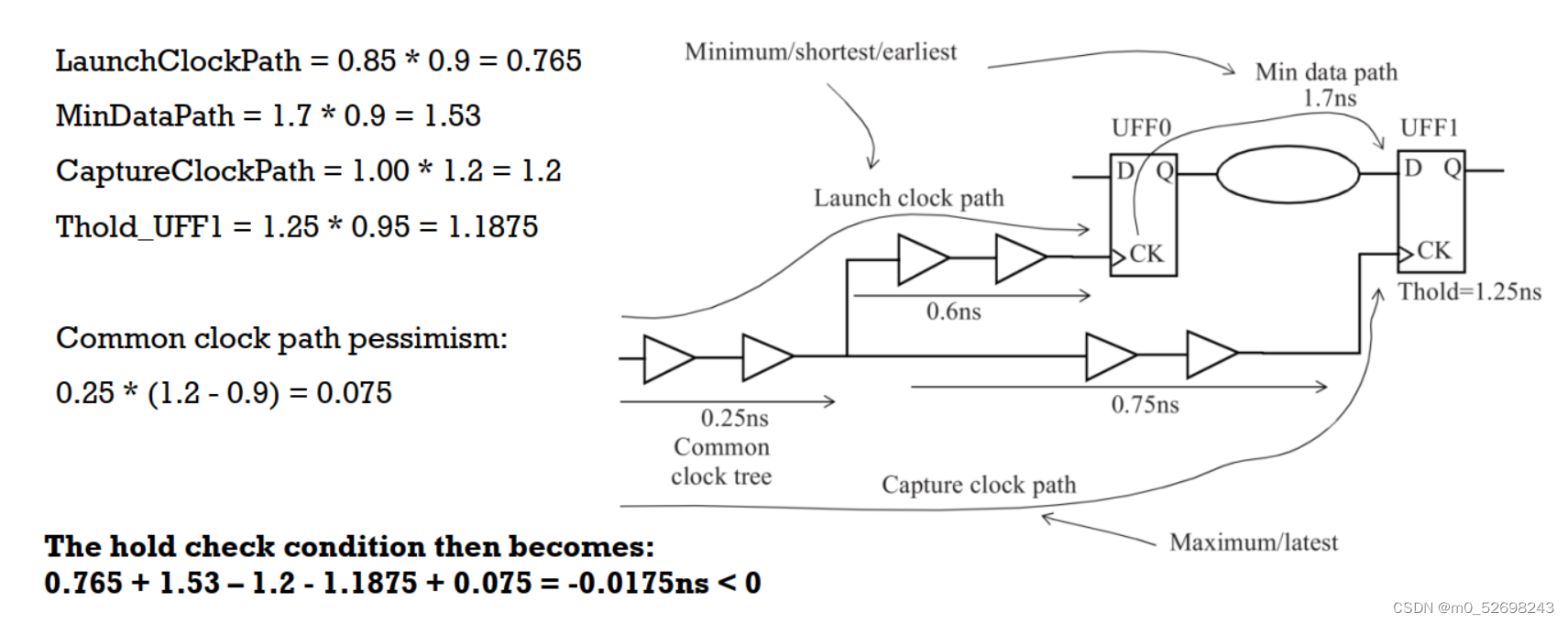

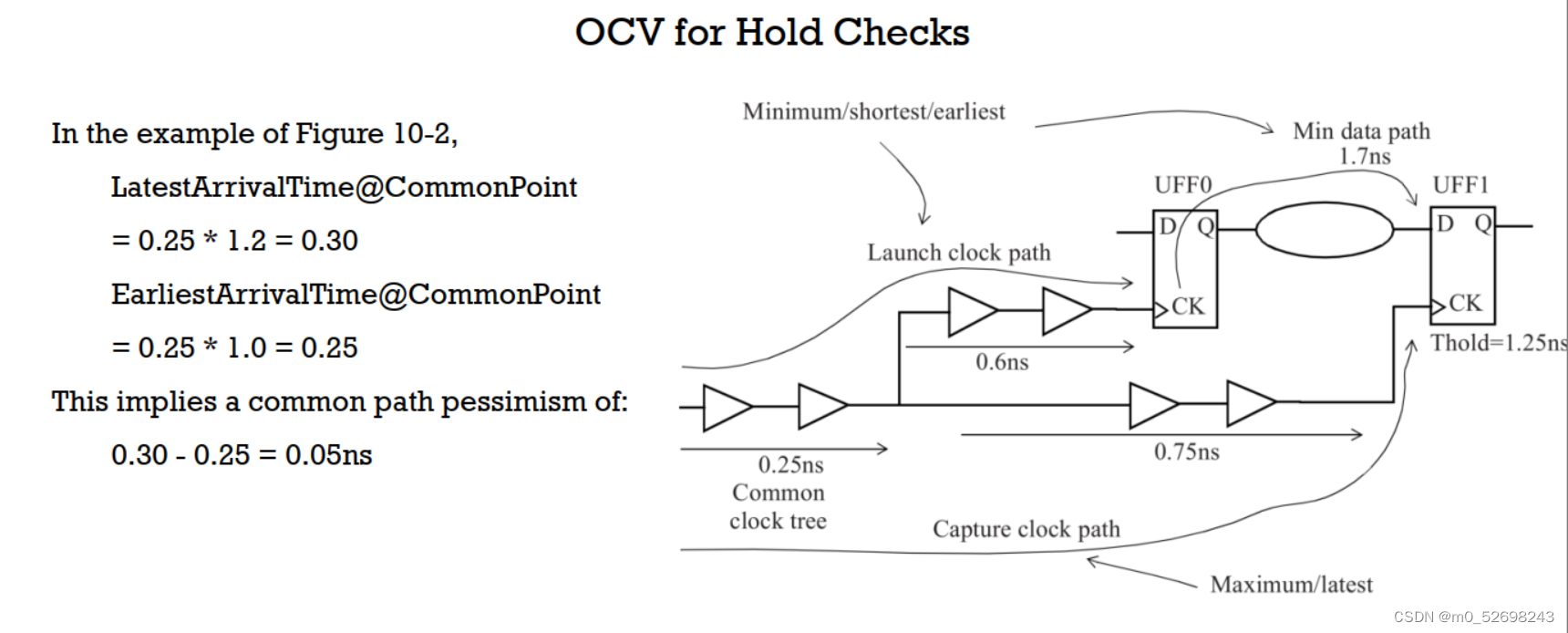

周期从5.49ns->7.171ns,时序变的恶劣了,频率降低了。如果想要变回原来的,data path要更短,要进行优化。 但是在上面的setup checks中,有一个差异,因为时钟树的公共时钟路径(延迟为1.2ns)对启动时钟和捕获时钟的降率不同。 时钟树的这一部分对于启动时钟和捕获时钟都是通用的,不应该有不同的降率。时钟树的这一部分实际上只有一个PVT条件,要么作为最大路径,要么作为最小路径(或介于两者之间),但永远不会同时出现这两种情况。 不同降额因子作用于时钟树的共同部分所产生的悲观情绪称为共同路径悲观情绪(common Path pessimism, CPP),在分析时应予以剔除。 CPPR (Common Path Pessimism Removal的缩写)通常在路径报告中单独列出。 CPP = LatestArrivalTime@CommonPoint – EarliestArrivalTime@CommonPoint

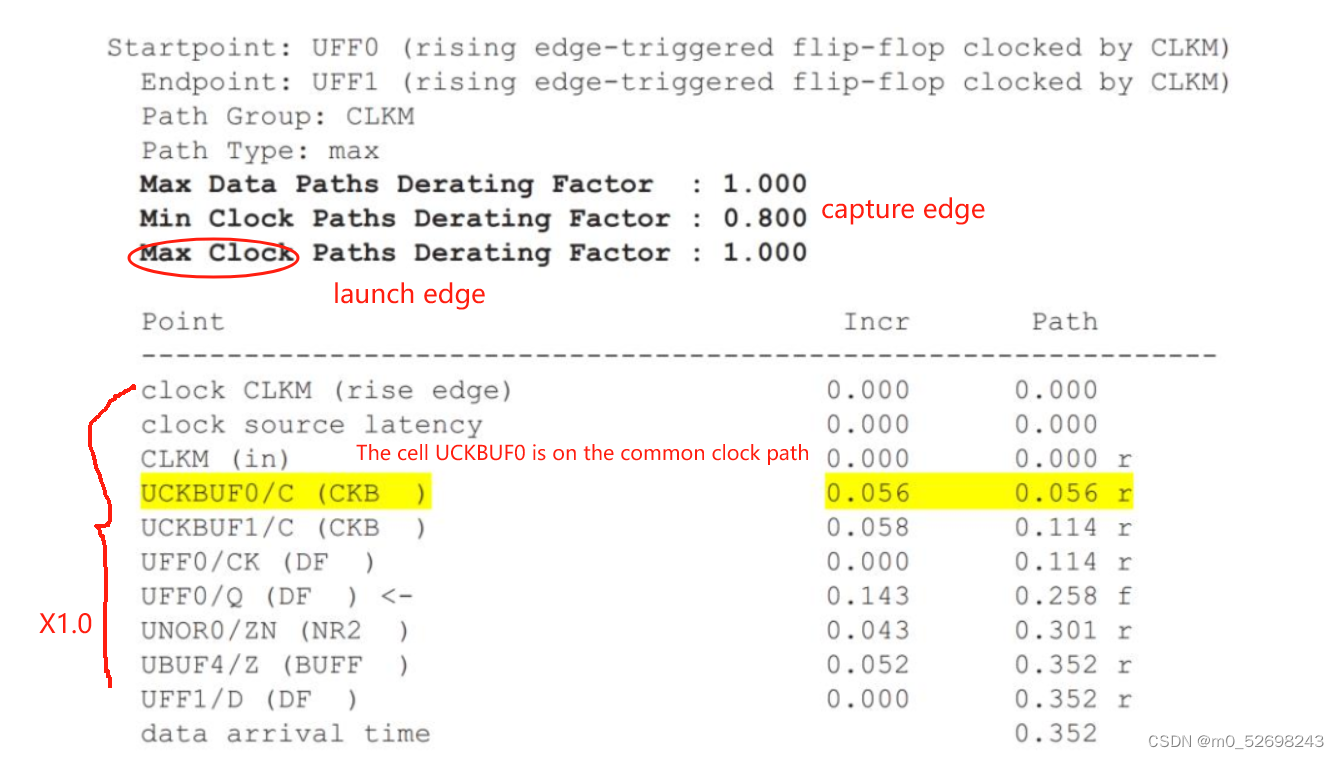

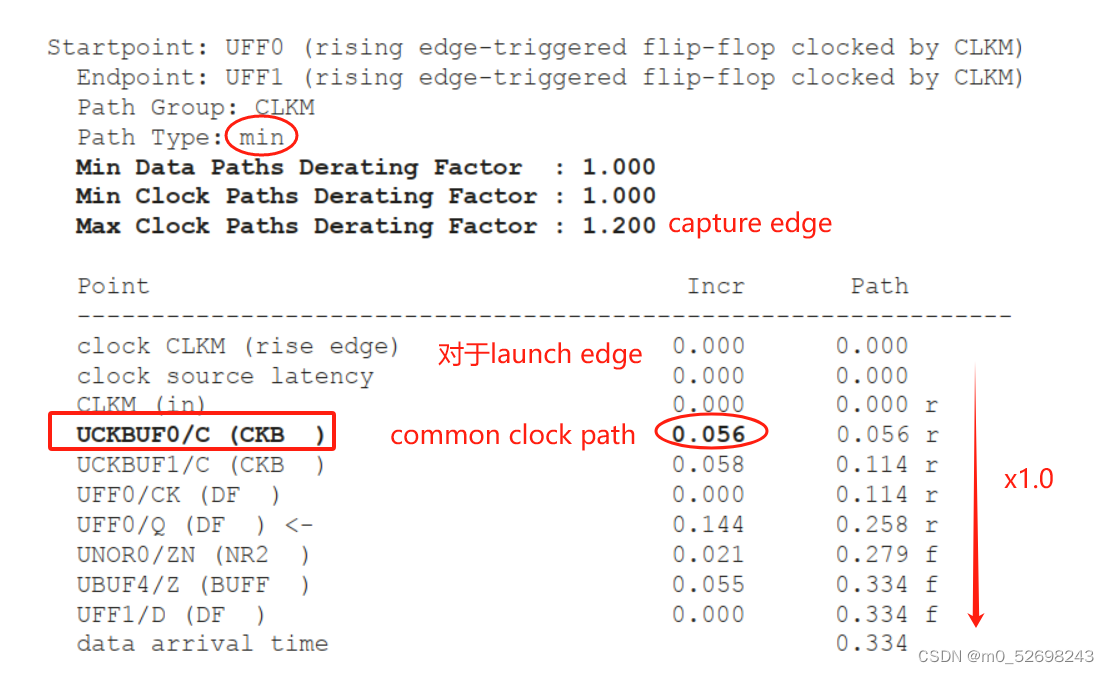

应用OCV降额增加了最小时钟周期(从5.49ns->6.811ns)。 这说明,通过这些降额因子建模的OCV变化可以降低设计的最大工作频率。 最坏PVT状态下的OCV分析如果在最坏的PVT条件下执行Setup Timing Checks,则不需要在late path上进行降额,因为它们已经是最坏的可能。 然而,降额可以应用于early path,通过使用特定的降额使这些路径更快。 分析时序报告

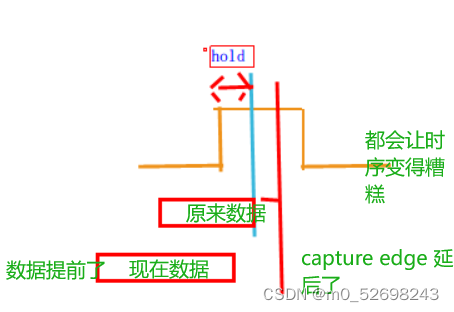

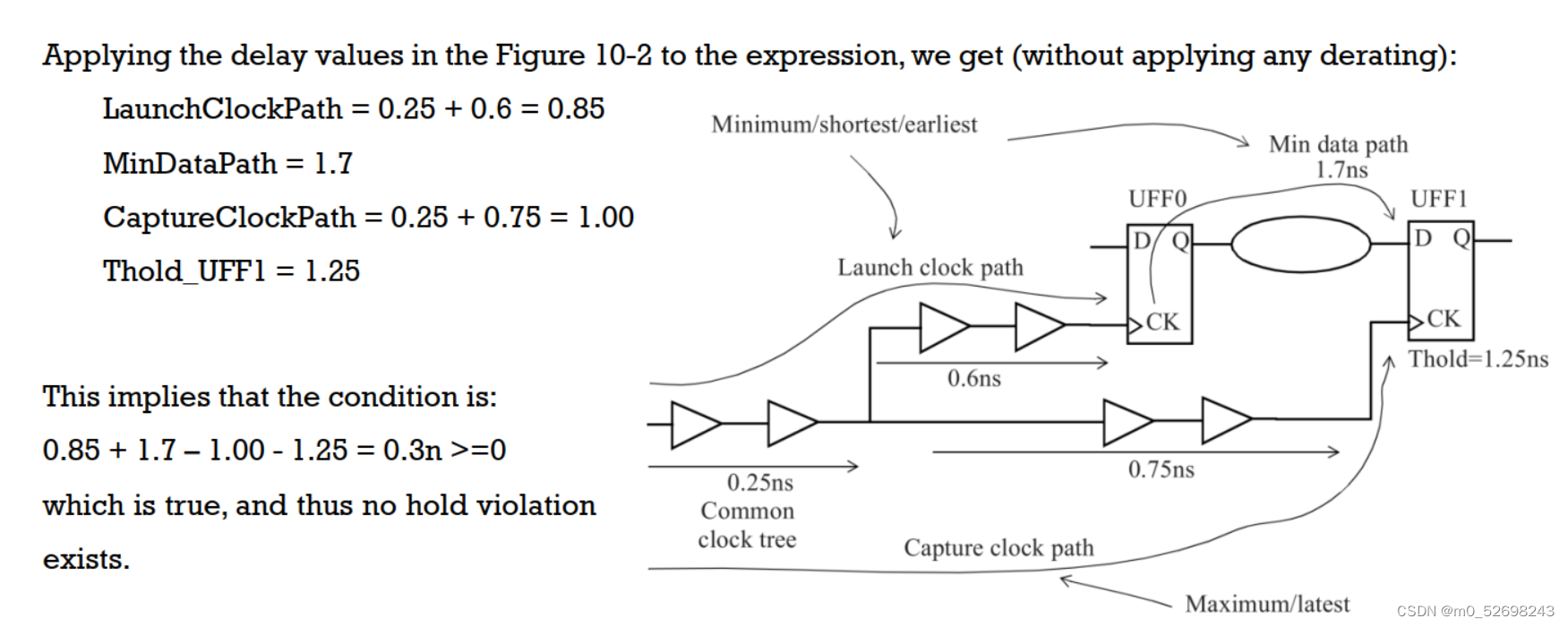

the worst condition for hold check occurs: when the launch clock path and the data path have OCV conditions which result in the smallest delays, that is, when we have the earliest launch clock, and the capture clock path has the OCV conditions which result in the largest delays,that is, has the latest capture clock.

公式如下:

Applying the following derate specification: set_timing_derate -early 0.9 set_timing_derate -late 1.2 set_timing_derate -early 0.95 -cell_check

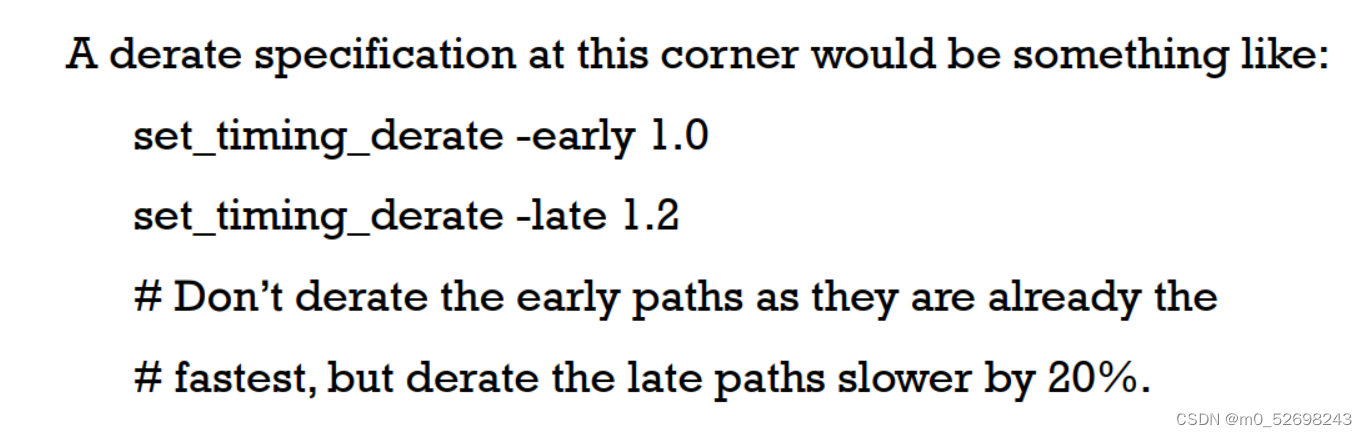

一般来说,保持时间检查在最佳情况下的快速PVT corner。 在这种情况下,early path不需要降额,因为这些路径已经是最早的可能路径。 但是,可以通过特定的降额因子使late path变慢。

时序报告:

一般情况 OCV对setup check的late path(launch edge)进行小的约束(比如0.9), 对hold check的early path(capture edge)进行大的约束(比如1.1)。 |

【本文地址】

上面描述的PVT变化被称为片上变化(OCV),这些变化可以影响芯片不同部分的线延迟和单元延迟。

上面描述的PVT变化被称为片上变化(OCV),这些变化可以影响芯片不同部分的线延迟和单元延迟。

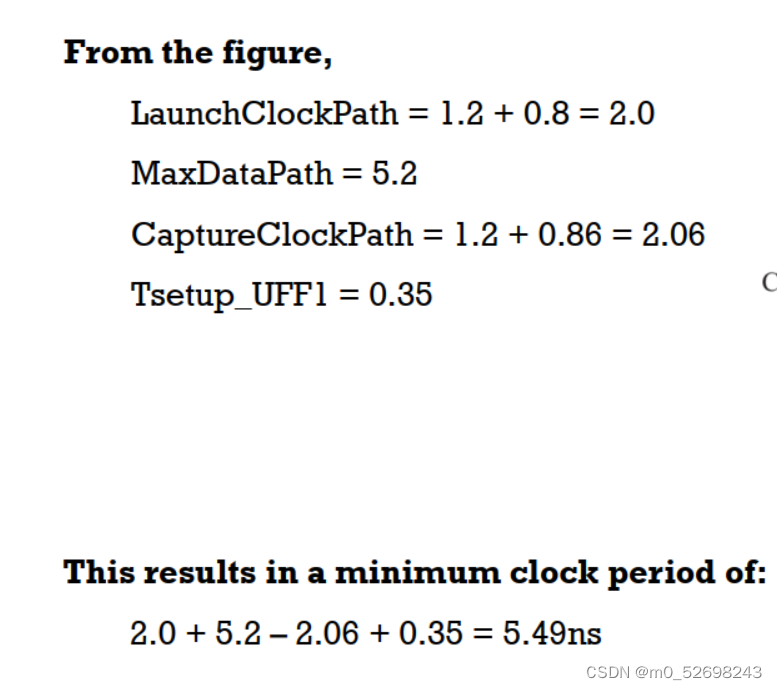

上述路径延迟对应于没有任何OCV降额的延迟值。单元和网络延迟可以set_timing_derate规范降额

上述路径延迟对应于没有任何OCV降额的延迟值。单元和网络延迟可以set_timing_derate规范降额

总结

总结