【硬核】FPGA进阶之路( 二) 如何将Xilinx SRIO控制器自环 |

您所在的位置:网站首页 › srio驱动芯片 › 【硬核】FPGA进阶之路( 二) 如何将Xilinx SRIO控制器自环 |

【硬核】FPGA进阶之路( 二) 如何将Xilinx SRIO控制器自环

|

(二)如何将Xilinx SRIO控制器自环 --小风哥的FPGA进阶之路 最近在解决板内FPGA的SRIO与DSP的SRIO通信问题,在不确定自己的SRIO是否正常时,可以采用自环的方式进行验证。

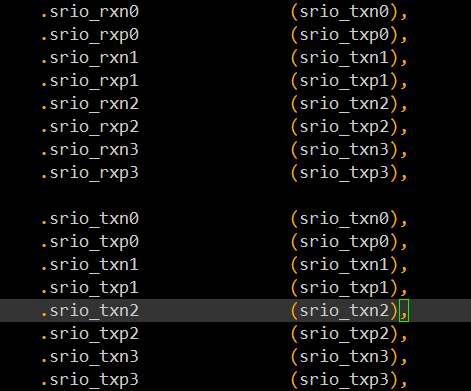

自环有两种,一种是外部打环,一种是内部打环。 外部打环:适用于易于飞线或者TR对接的系统(例如光纤连接的SRIO endpoint); 内部打环:其实首推的外部打环,因为外部打环可以帮忙验证走线和引脚等外围电路是否存在问题,当无法进行外部打环时,可以尝内部打环。 一 简单粗暴的尝试 笔者尝试了直接在example的顶层调用IP的地方,将tx和rx对接,代码如下:

结果可以预见,vivado给出如下布线错误:

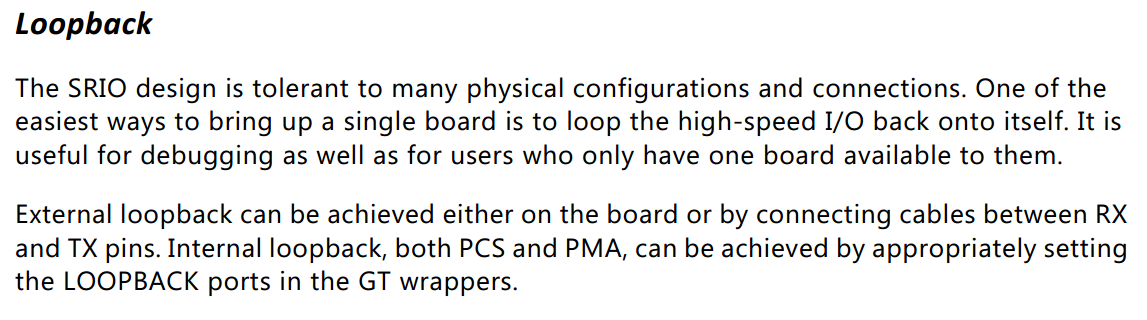

原因分析:因为IP核在实现从单端到差分时,内部封装了OBUFDS/IBUFDS,因为IP核版权保护的原因,我无法删除IP核内部的OBUFDS/IBUFDS,vivado自然无法通过布线。 二 正确的做法网上搜了一下,网友们提到IP核中有关于自环的功能,但是却也对如何使用这个功能模棱两可。 研读了pg007 Serial RapidIO Gen2 Endpoint v4.1,找到了这样的描述

不得不说,PG007关于SRIO loopback模式的描述真的简单,没有说关于loopback在 srio_gen2的哪一级可以配置,也没有loopback模式如何配置的描述。我也算是瞎猫碰到死耗子,我在ug476 7 Series FPGAs GTX/GTH Transceivers,找到了loopback模式的详细描述。

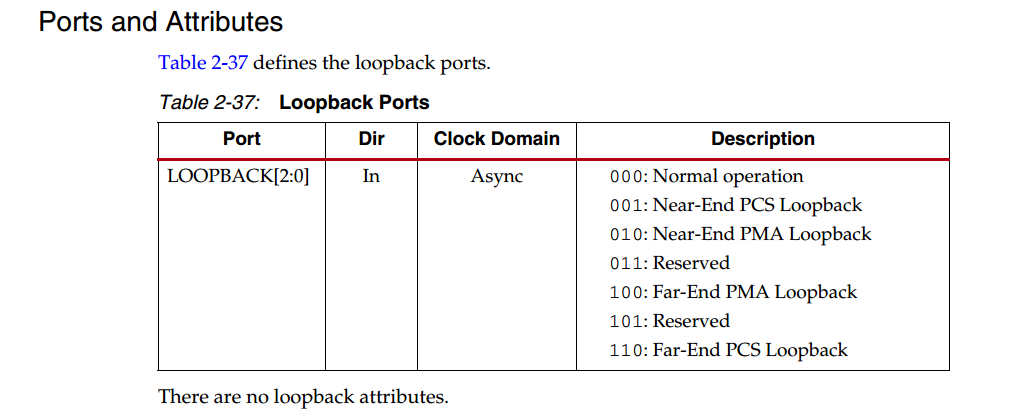

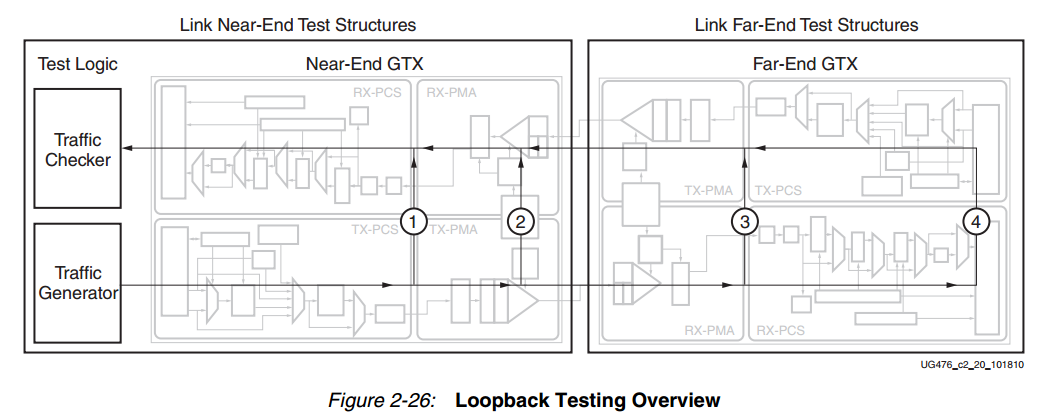

根据上面的表格,我们知道LOOPBACK是一个3 bits寄存器,支持配置:正常模式,近/远端PCS子层回环,近/远端PMA子层回环。关于回环示意图如下:

找到工程srio_gen2 IP所在根目录,打开synth文件夹下的srio_gen2_0_block.v:

找到gt_loopback_in端口的例化,将原来的12'h0(我用的是SRIO 4X)改为你想要配置的模式,如下图所示我这里将配置改成3’b010,即近端PMA子层自环。

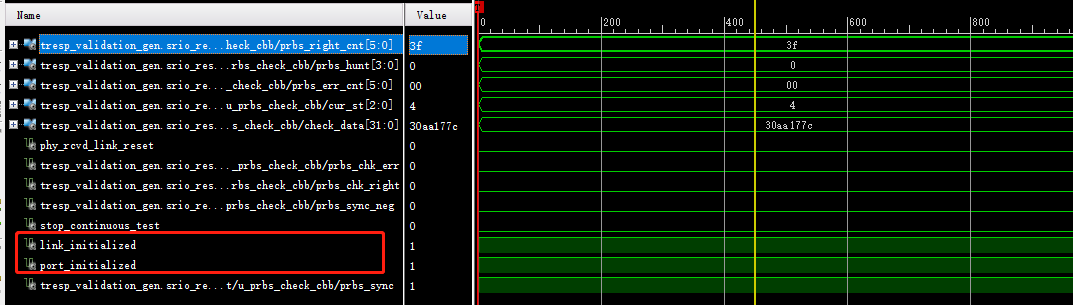

自环的配置搞好了,后面就是编写自环测试的代码了,提醒一下,自环测试,源地址和目的地址要配置成一样的哦。 测试代码修改并仿真完毕,是否需要先将你的 srio_gen2 IP执行reset output products再generate output products,执行更新IP操作呢,答案是不需要。小风哥发现,再怎么修改synth下的.v文件,vivado也不会提示你 synthesis is out of date,这是你需要重新run synthesis和Implementation就可以了。synth文件夹下的文件本来就是执行综合用的。 小风哥使用的是vivado 2015.4官方的example,跑我自己的板子,所以只需要约束一下SRIO的差分时钟和板卡复位就可以了,port_initialized和link_initialized都可以正常拉高,说明我的SRIO自环成功了,效果见下图。 PS:下图中最后一个信号:prbs_sync是我PRBS检查通过的信号,由此可以判断Initiator发起的NWRITE的包,回环后target已经正常接收,并在我的PRBS检查模块通过了比较。

你学会了吗?

|

【本文地址】

今日新闻 |

推荐新闻 |