12G高速SDI信号简介及PCB设计 |

您所在的位置:网站首页 › sdi线的传输距离 › 12G高速SDI信号简介及PCB设计 |

12G高速SDI信号简介及PCB设计

|

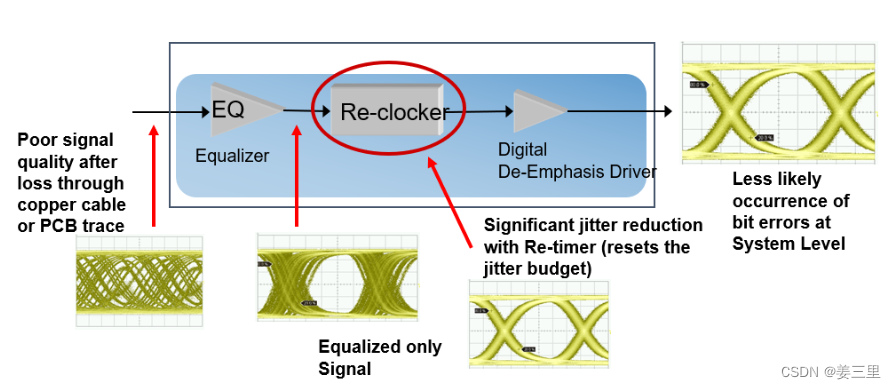

【SDI简介】 SDI的传输技术, 从原本传输480i/60f的SD-SDI, 一直进步到现在, 使用相同的75 Ohm同轴电缆, 最高能传输4K/60f 4:2:2即时非压缩影音的12G UHD-SDI, 搭配Belden 1694A的同轴电缆, 可以传输80M的距离, 保持着SDI传输技术能传输长距离的特性。 【核心技术】 时钟均衡和驱动(Equalizer、 Re-clocker、Cable Driver)在SDI 应用里, 其实占了很大的比例, 因为这些功能都是让SDI讯号传输距离可以拉远的功臣, 因为SDI是高速串列的数位讯号, 采用NRZI的编码方式, 所以在传输讯号时只有0跟1的变化, 但因为经过长距离的传输过后, 高频的讯号会因为距离而比低频讯号更快衰减, 同时也会受到反射的干扰, 造成原本的高速串列数位讯号变差。可以参考下图最左边的示意图, EQ(Equalizer)的主要功能, 就是将这杂乱的讯号, 还原成能判断为0或1的数位讯号, 也就是把眼图给打开来, 如下图左二的示意图, 但这个讯号能正确判断为0或1的区域很窄, 取样点只要有一些偏差, 就会取错值, 而在能正确判断为0或1的区域之外的部分, 就是所谓的jitter抖动, 为了将这些jitter抖动滤除, 就会需要使用Re-clocker(Re-timer), 对讯号重新整理以产生很低jitter抖动的高速串列数位讯号, 如下图右二的示意图, 最后因为SMPTE在SDI讯号的输出是有规定rising time, falling time, overshoot, undershoot及振幅需为800mVpp, 所以Cable Driver就是使用De-Emphasis或Pre-Emphasis技术, 让SDI的输出可以符合SMPTE的规范, 可以参考下图最右边的示意图, 以上就是简单的介绍Equalizer, Re-clocker(Re-timer)及Cable Driver在SDI 应用里的功能

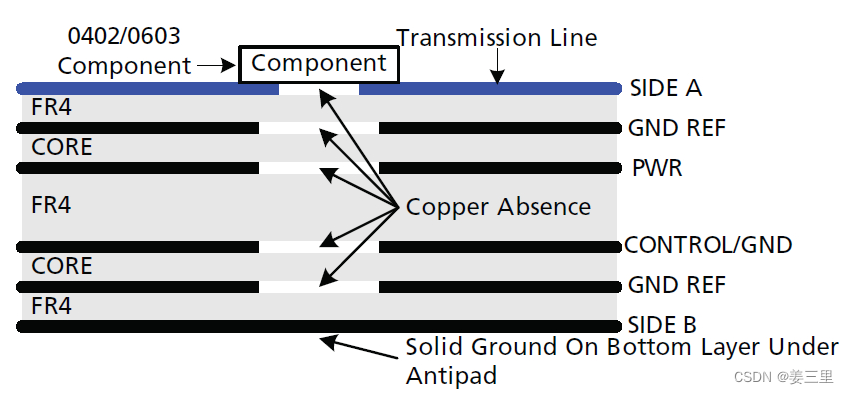

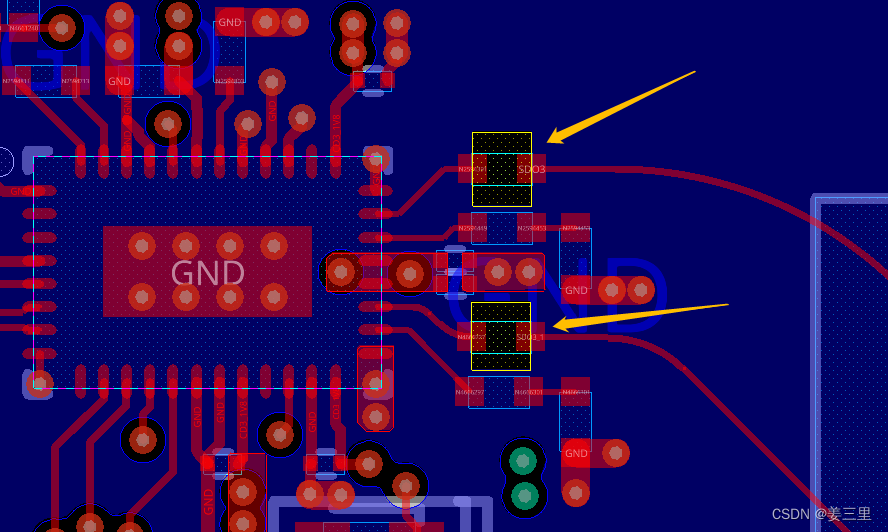

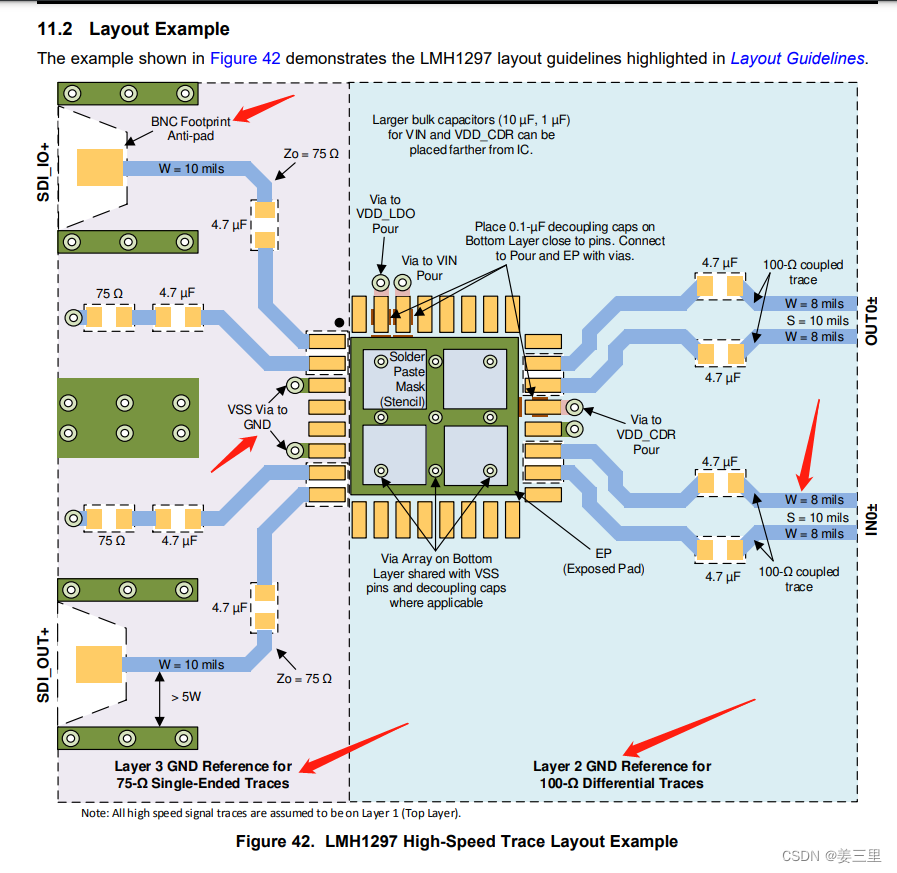

【PCB设计要点】 1、SDI驱动或接受芯片到连接器的路径越短越好; 2、即使12G UHD-SDI信号,PCB材质仍然可以使用FR4; 3、单端信号75Ω的阻抗匹配、差分信号100Ω阻抗匹配; 通常使用Layer2_GND作为100Ω差分信号的参考平面,使用Layer3_GND(或更靠底层)作为75Ω的特征阻抗参考平面,以减小寄生参数对特征阻抗的影响。参考地平面对于整条信号线需要保持连续,不连续会导致寄生阻抗不匹配。4、SDI trace的宽度最好在10 ~ 12 mil, 因为在SDI的应用在input/output return loss部分需要符合SMPTE规范, 而SDI trace的宽度太细比较难通过规范; 注意如果信号线和参考地在PCB同一层,至少保持5倍线宽,可以减小寄生阻抗。5、AntiPad处理:75 Ohm与BNC连接的单端讯号, 通常会有AC coupling电容, 而在这些电容的下方, 则需要加入Anti-PAD来降低寄生电容所造成的损失, 这个Anti-PAD最简单的做法, 就是在PCBA的内层, 挖开一个跟AC coupling电容相同大小的keep out, 在所有内层都需要摆放, 主要是让SDI trace上的AC coupling电容的参考层, 从第二层改到底层, 利用这个方法来降低寄生电容所造成的损失;

6、 根据芯片和BNC连接器,谨慎设计PCB和连接器处的信号和AntiPad处理 附:Ti设计参考

|

【本文地址】

今日新闻 |

推荐新闻 |