XILINX关于DDR2的IP的读写控制仿真 |

您所在的位置:网站首页 › ras怎么念 › XILINX关于DDR2的IP的读写控制仿真 |

XILINX关于DDR2的IP的读写控制仿真

|

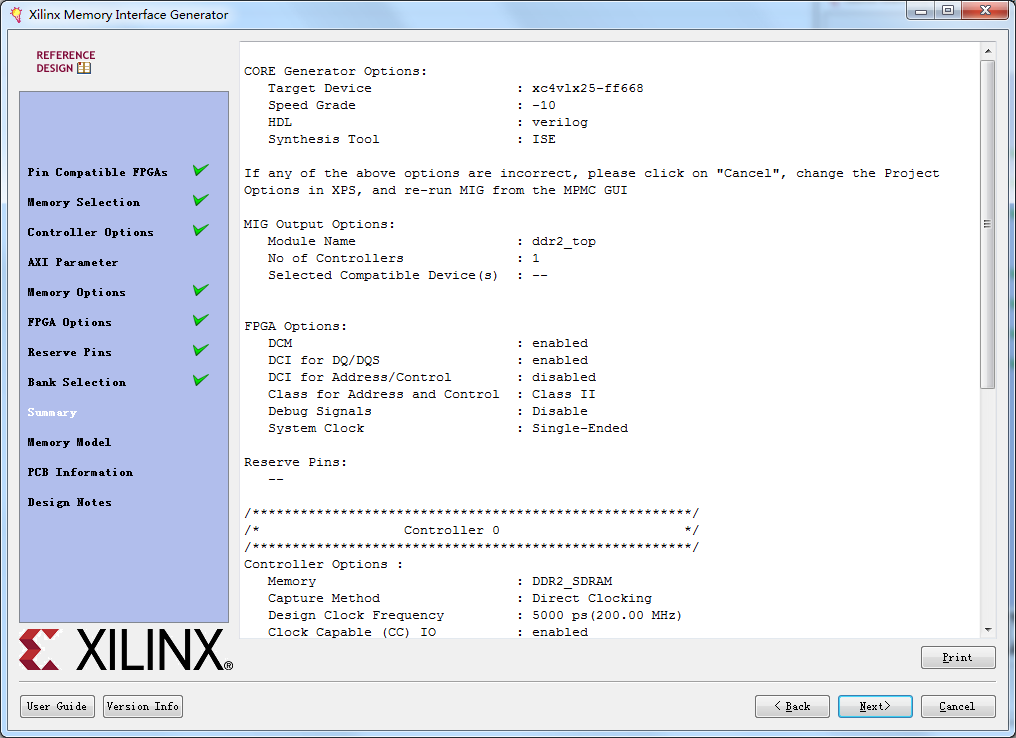

最近没事。看了一下ddr2的读写访问。 平台:ISE 芯片:V4,XC4VLX25,ff668,-10 语言:VerilogHDL 参考文件:ug086.ug086.pdf • 查看器 • 文档门户 (xilinx.com) 关于DDR2的MIG核的新建新建IP:参见UG086的using mig。输入频率200mhz,突发长度BL=4。

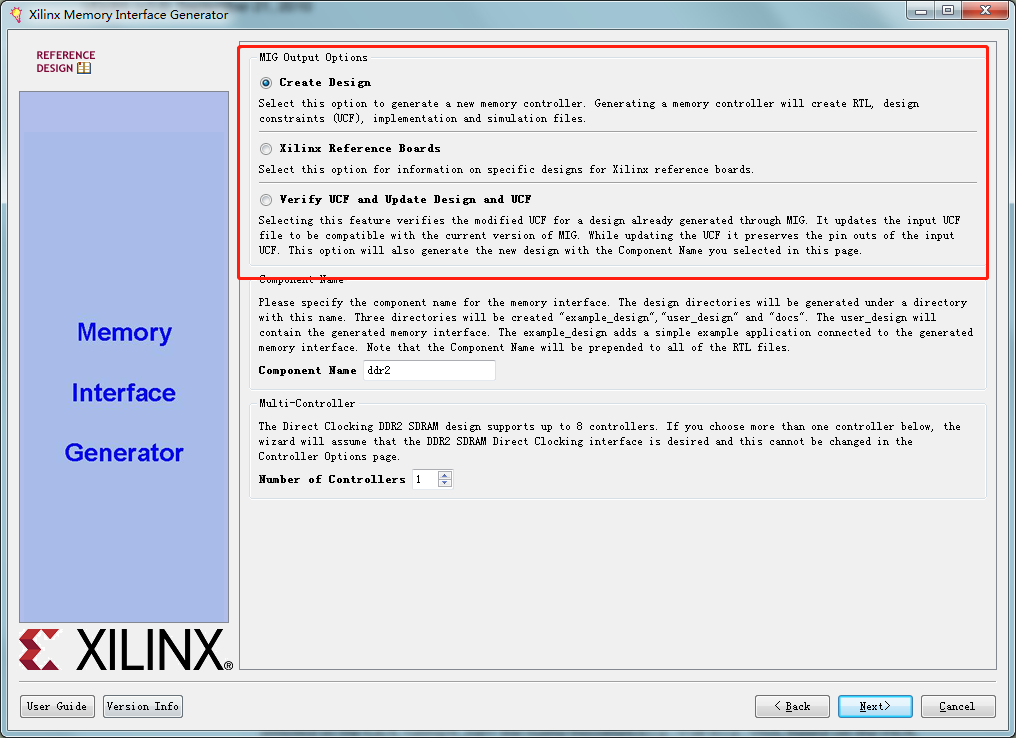

新建MIG IP核,此页面为IP的版本信息与FPGA器件。右下角可以下载IP的说明书。

MIG IP有几种不同的输出选项,这里我们选择create design。对于多控制器的应用,可以下下面munber of controllers中选择,这里我们使用一个。

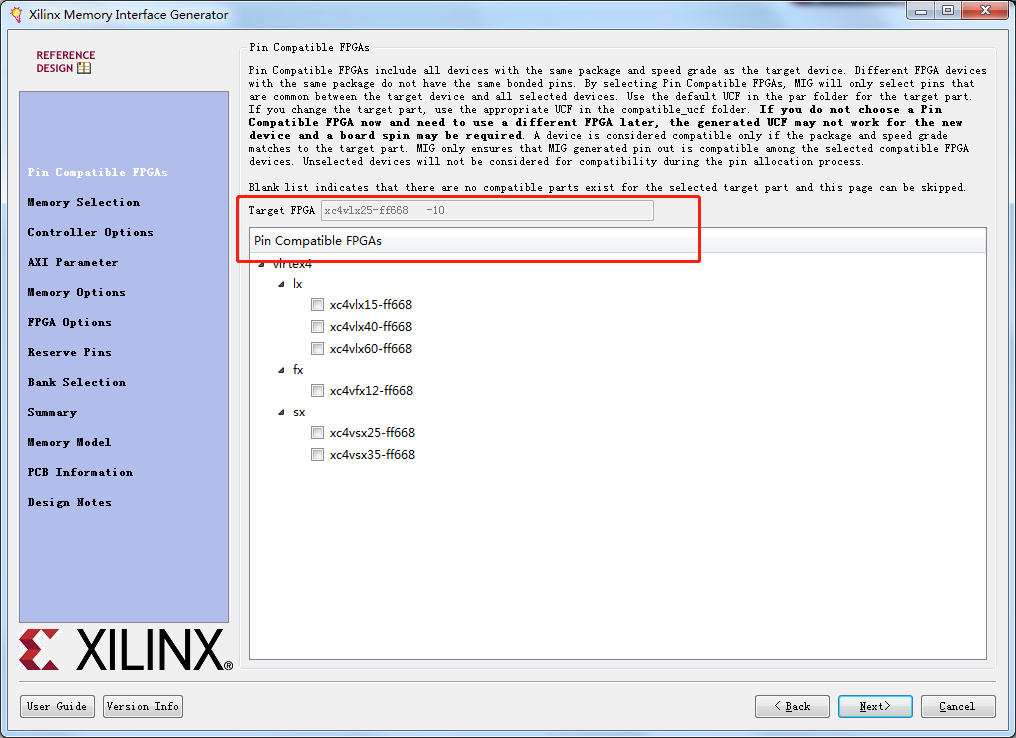

这里可以选择PIN兼容的FPGA,这里只需要支持我们的FPGA就行了。不用选择。

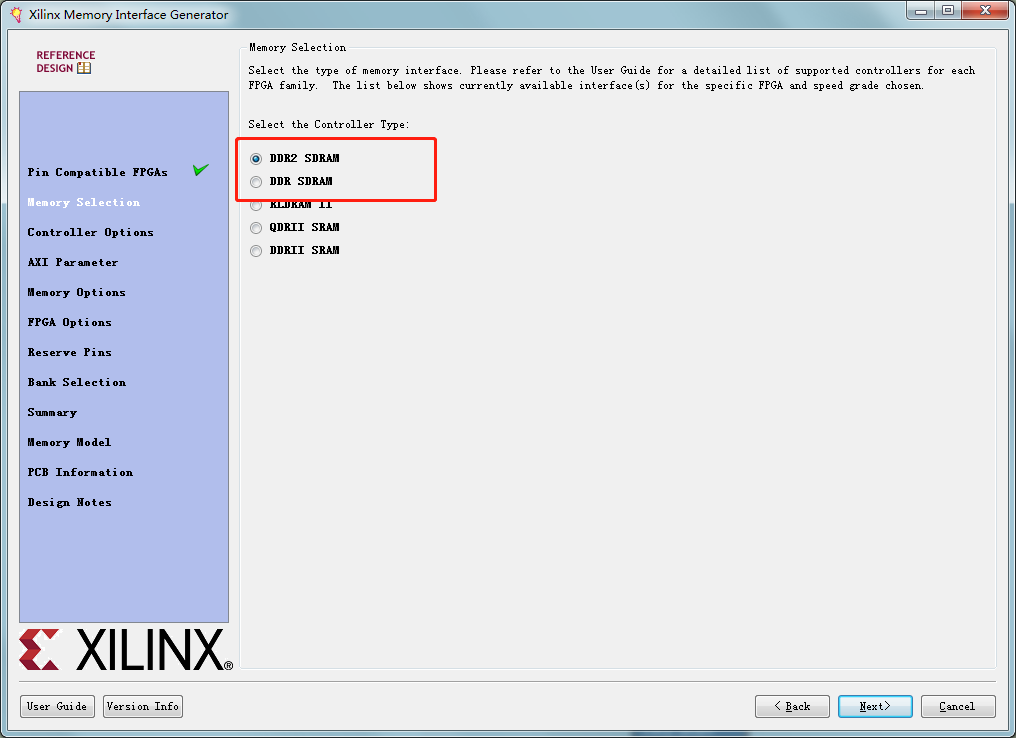

内存选择界面。界面显示了FPGA支持的内存,可以看到支持ddr2和ddr。我们这里选择为ddr2。

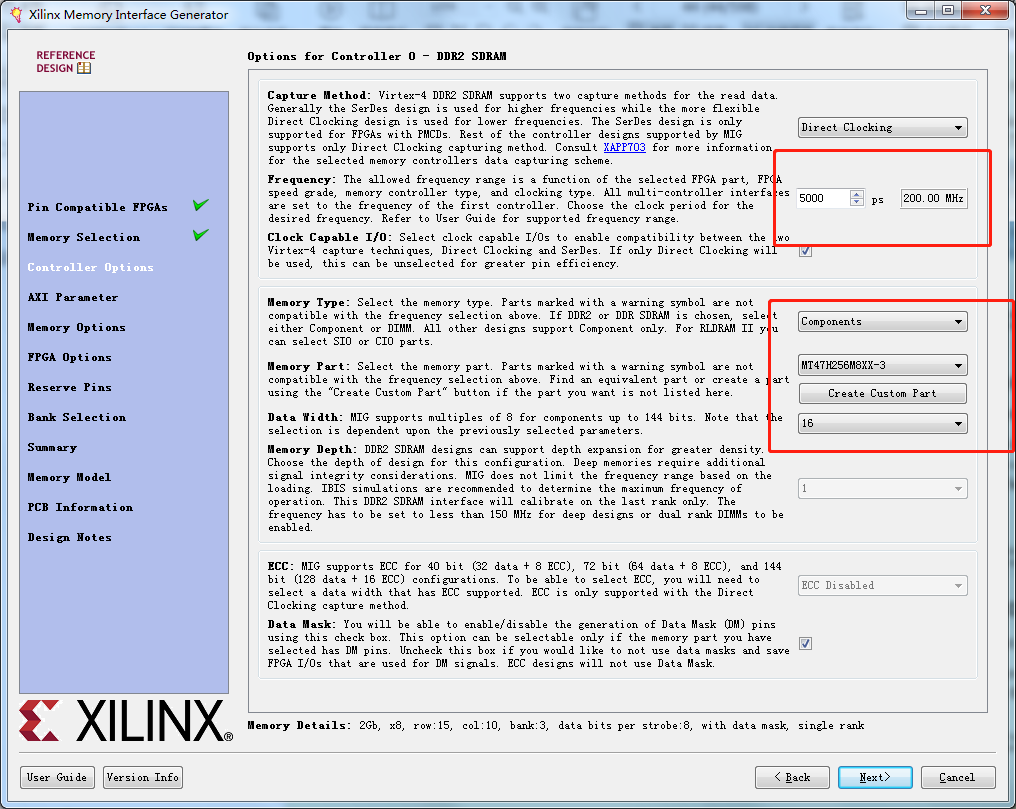

capture method捕获方式,一般对于高频采样serdes时钟,而我们这里使用direct clocking时钟。frequency选择控制器输入的时钟。我们外部晶振提供了200MHZ时钟,这里输入200mhz。 Memory Type,Memory Part选择内存类型,和内存型号,我们这里选择的内存型号为MT47H256M8XX-3,也就是默认随便选择的。容量大小256Mbit*8=2Gbit=256MB。 create custom part创建自定义部件这里默认就好了。 data width选择为16位。后面部分保持默认就好。 data mask关于数据掩码,ddr2的访问都是以突发的形式连续访问同一行的相邻几个单元,数据掩码屏蔽了不需要的数据。

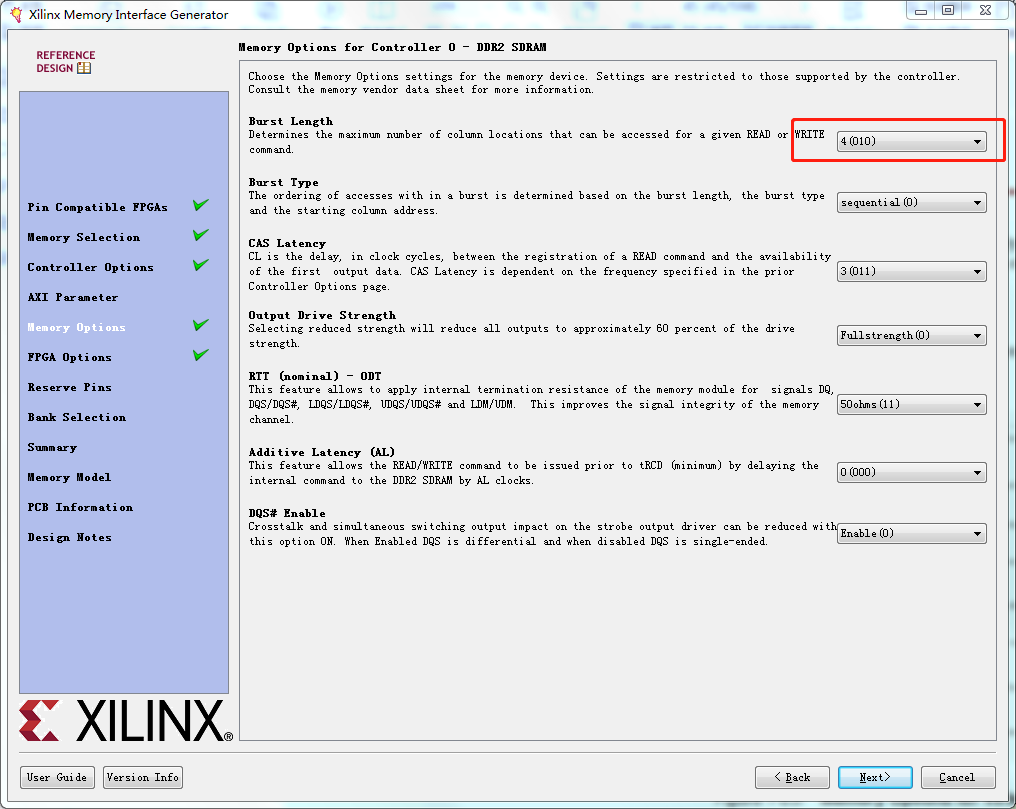

内存选择,此页面需要关注的是burst length突发长度。ddr2支持4和8的突发长度。这里可以修改。对于这两种突发模式,在对ddr2进行读写操作的时候地址和数据对应关系,对于突发长度为4,每个地址对应于数据fifo的两次写入,对于突发长度为8,每个地址对应于数据fifo的四次写入。其他参数默认即可。

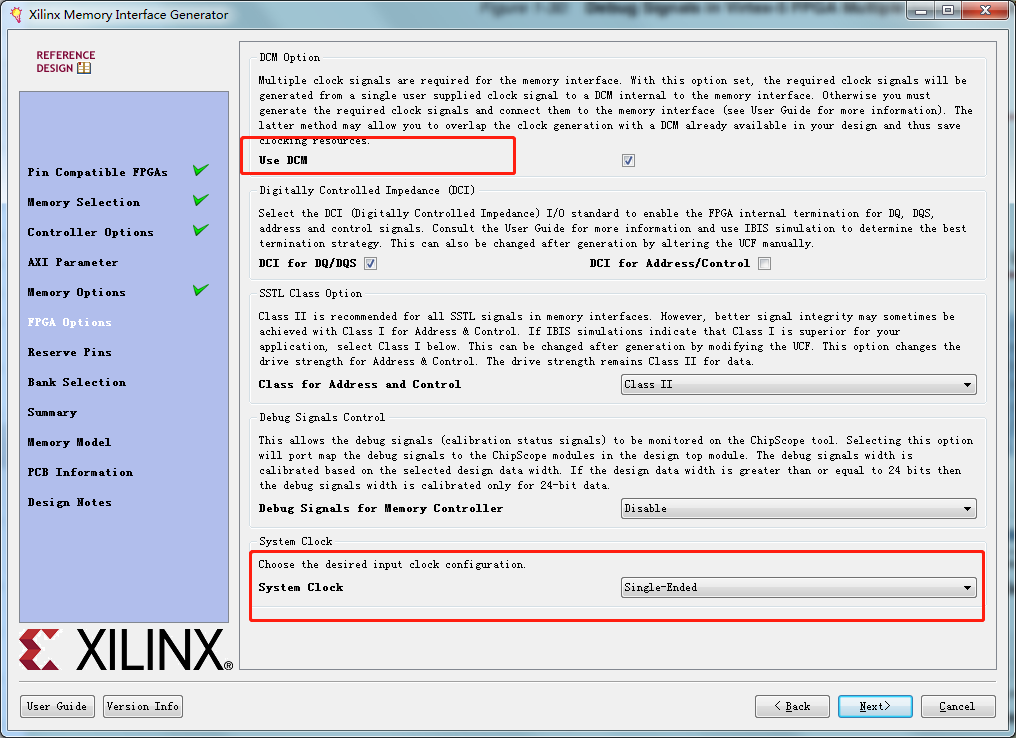

FPGA选择,这里默认选择为使用DCM,即时钟需要经过DCM后输入到DDR2。系统时钟选择为单端,根据实际选择。

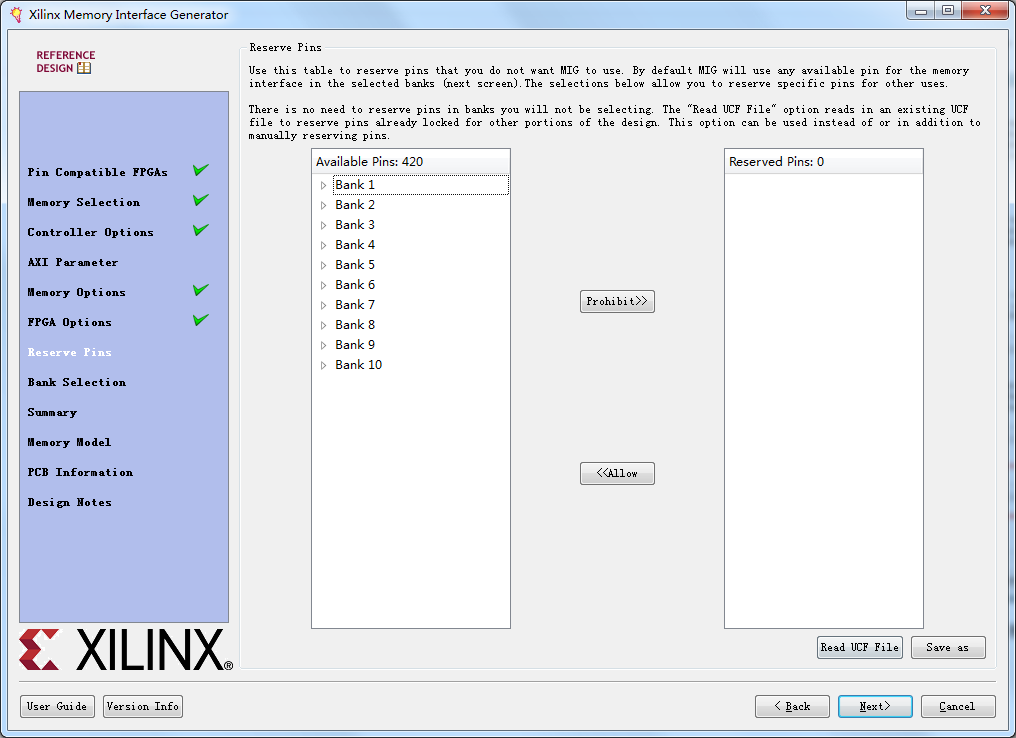

选择UCF引脚。这里我们只做仿真,不设置,如果有UCF引脚可以直接点击Read UCF File。

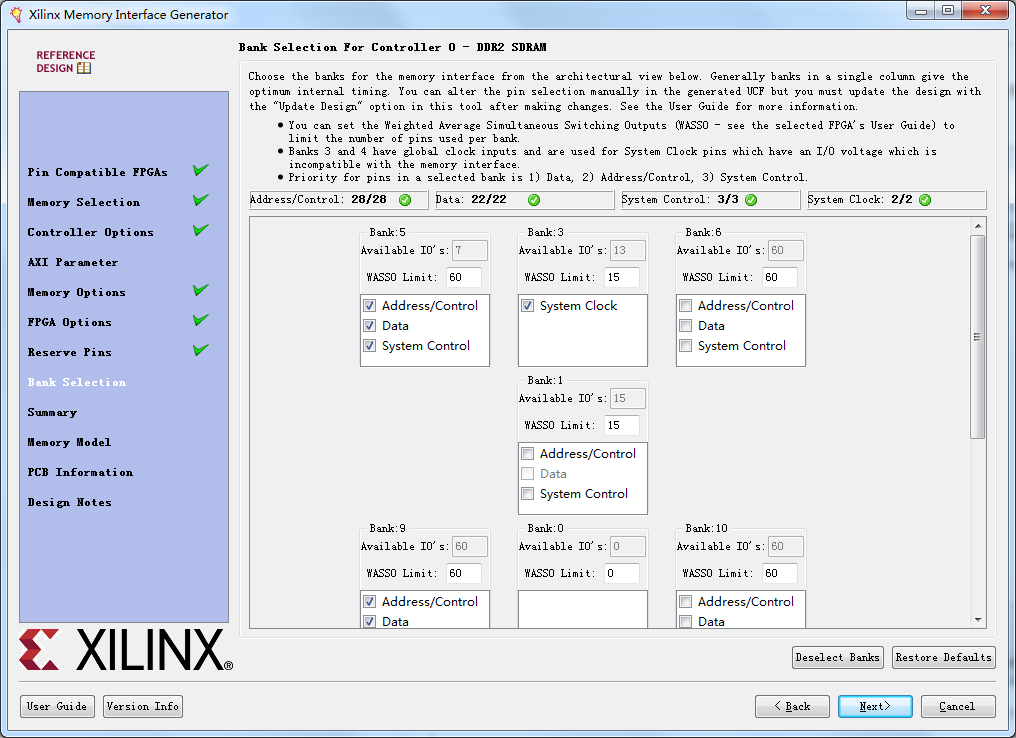

保持默认分配的引脚。

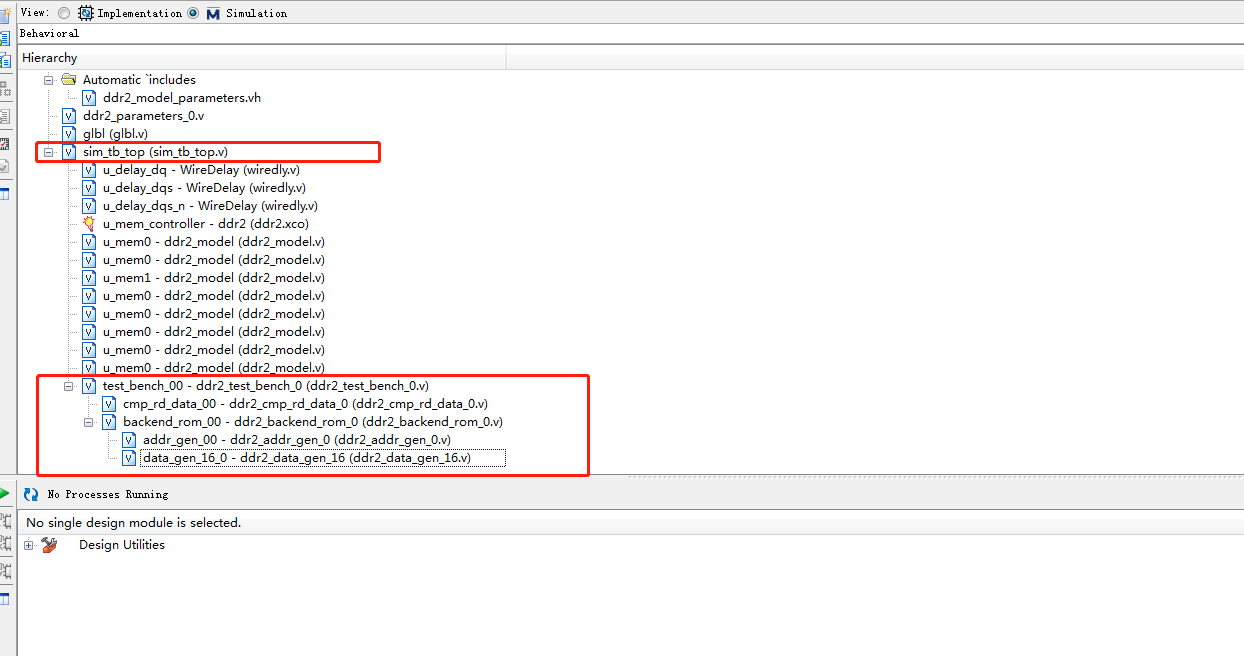

总结说明。之后一路next,生成IP。 关于DDR2的MIG核的仿真打开仿真工程,添加文件如下。 E:\code1\FPGAzero_bace\Virtex4\DDR2_TEST\ddr2_test\ipcore_dir\ddr2\user_design\sim文件夹下的全部文件。文件添加成功后效果如下。

添加后效果如下,官方的例程结构是一个很好的参考工程。可以方便大家理解DDR2内部信号的传输。

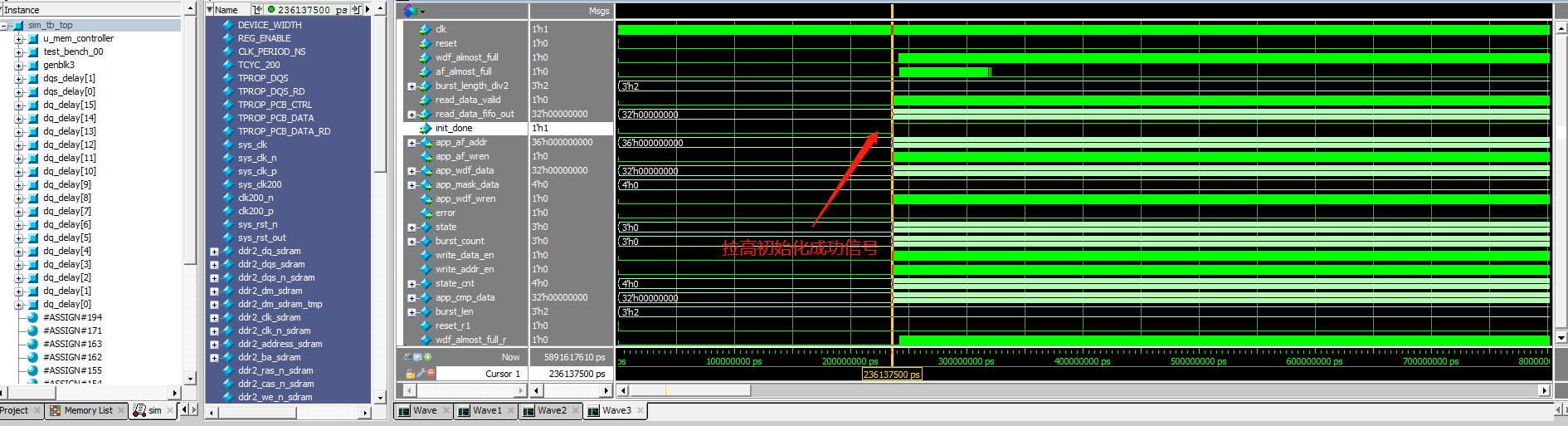

可以看到成功拉高init_done初始化成功信号。通过ug086可以知道,test_bench_00模块交替执行了8个写入命令和8个读出命令。我们选择的突发长度为4,所以执行写入了32个数据字(16个上升沿数据字和16个下降沿数据字)。而对于突发长度为8的设计,执行8个写入命令将执行写入64个数据字。 在test_bench模块中,addr_gen和data_gen产生地址和数据,ddr2_cmp_rd_data模块验证收到的数据是否正确。 感兴趣的同学可以研究一下他们的测试代码。 下面我们使用自己的代码来代替官方的这部分仿真代码实现自由读写ddr2。 下面分析一下sim_tb_top,该文件是对ddr2的仿真,top端设置了时钟的产生。 //*************************************************************************** // Clock generation and reset //*************************************************************************** initial sys_clk = 1'b0; always sys_clk = #(CLK_PERIOD_NS/2) ~sys_clk; //设置系统时钟CLK_PERIOD_NS= 5000.0 / 1000.0;时间刻度是ns,即系统时钟5ns翻 //转一次,sys_clk=100MHZ. //差分时钟sys_clk_p/n也是一致,其中n相差180° assign sys_clk_p = sys_clk; assign sys_clk_n = ~sys_clk; initial sys_clk200 = 1'b0; always sys_clk200 = #(TCYC_200/2) ~sys_clk200; //TCYC_200=5,sys_clk200为200mhz时钟。 assign clk200_p = sys_clk200; assign clk200_n = ~sys_clk200; //pci 时钟 initial pci_clk = 1'b0; always pci_clk = # 15 ~pci_clk; assign pci_rst = ~sys_rst_n; initial begin sys_rst_n = 1'b0; #200; sys_rst_n = 1'b1; end //测试复位200ns后拉高 assign sys_rst_out = `RESET_ACTIVE_LOW ? sys_rst_n : ~sys_rst_n; //输出到DDR的复位高有效模拟产生ddr的控制信号。 // ============================================================================= // BOARD Parameters // 这部分模拟产生ddr的控制信号 // ============================================================================= // These parameter values can be changed to model varying board delays // between the Virtex-4 device and the memory model always @( * ) begin ddr2_clk_sdram |

【本文地址】