FPGA实现HDMI视频输出 |

您所在的位置:网站首页 › r9000p是满血显卡吗 › FPGA实现HDMI视频输出 |

FPGA实现HDMI视频输出

|

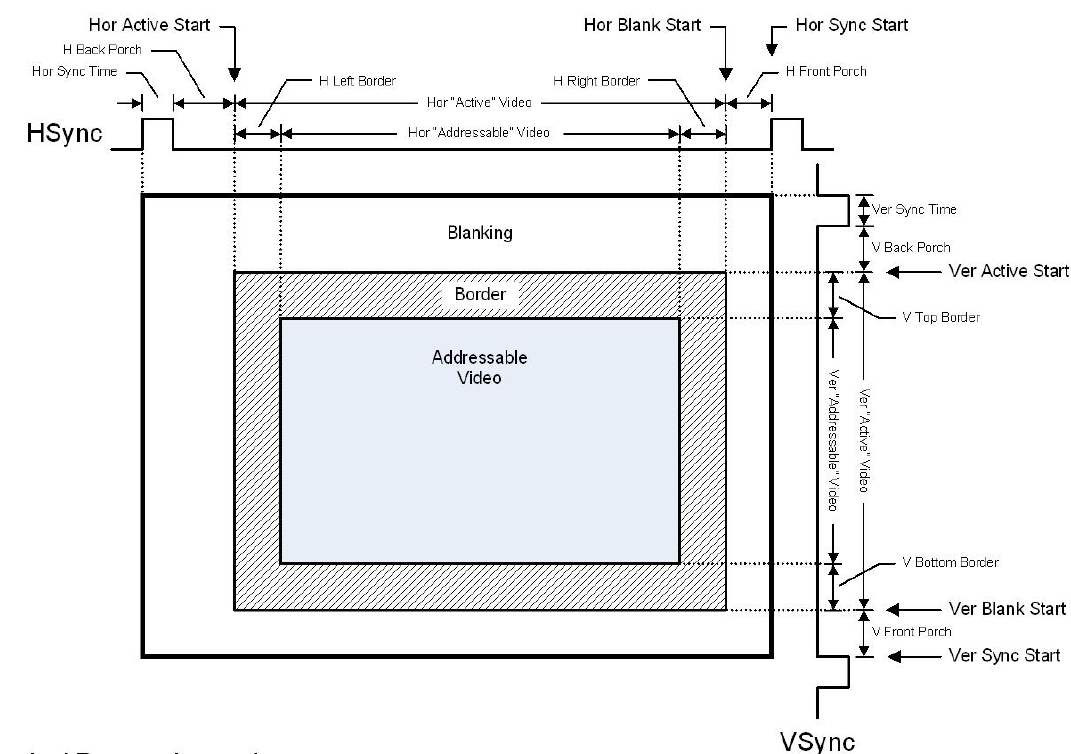

HDMI显示器扫描方式从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。 完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。标准的显示的场频60Hz。 时钟频率:以1024*768(60Hz)为例,每场对应806个行周期,其中768为显示行。每显示行包括1344点时钟,其中1024点为有效显示区。由此可知:需要点时钟频率:806*1344*60约65MHz。

VGA扫描,基本元素是行扫描,多行组成一帧,下图显示一行的时序,其中“Active”Video是一行视频的有效像素,大部分分辨率时钟中Top/Left Border 和 Bottom / Right Border都是0。“Blanking”是一行的同步时间,“Blanking”时间加上Active”Video时间就是一行的时间。“Blanking”又分为“Front Porch”、“Sync”、“Back Porch”三段。 |

【本文地址】

今日新闻 |

推荐新闻 |