基于vivado(语言Verilog)的FPGA学习(1) |

您所在的位置:网站首页 › q1q2q3什么意思 › 基于vivado(语言Verilog)的FPGA学习(1) |

基于vivado(语言Verilog)的FPGA学习(1)

|

基于vivado(语言Verilog)的FPGA学习(1)——了解程序面板和编译过程

每日废话:最近找实习略微一些焦虑,不想找软件开发,虽然有些C++和python基础(之前上课学的),但重点头疼的并不是语言,而是算法。想到本科阶段,有几次接触FPGA和MSP430时还是觉得很有意思,所以想往集成电路上转一下。(虽然当时还用的阿特尔(现被英特尔收购)的quartusⅡ工具,用的还是简单的VHDL和大量的时序集成电路。)去年一年回头又看了看Verilog的基本语法,趁着找实习的劲儿打算实操实操。 该系列文章主要记录自己学习AMD赛灵思的zed-board板子,在这个过程中慢慢熟悉一下Verilog和vivado工具。 文章目录 基于vivado(语言Verilog)的FPGA学习(1)——了解程序面板和编译过程1、vivado界面介绍1.1 左边的导航栏1.2 右边的文件栏 1、vivado界面介绍奇了怪,总觉得上学期写了这部分,梦里写的?

第一个是整个项目的管理(设置包含了项目设备选择、语言选择、文件管理等;添加资源文件;语言模板;IP目录)其中IP就是集成好的逻辑器件,最早在quartus上也是用这个进行连线的。 第二个就是IP集成,分别是创建块设计(手贱点了一下就有了右边的bd后缀文件);打开块设计(手继续贱打开后发现可以生成已经存在的IP核和自己编译的模块,可能经过连接就可以组合在一起变成“新设计出来的块”) 2.综合功能仿真:模拟无延迟情况,和行为仿真相同。 3.综合时序仿真:只要器件延迟(下面这个逻辑就不定状态了,很迷) 5.实现时序仿真:同上,包含了器件延迟和延迟线(例如在板子里,延迟线就是一对输入输出的实际距离连线)。这个地方与综合时序仿真不同,后面还恢复正常了??? 第四个是RTL分析,也就是可以画出原理图程度的仿真。寄存器转换级 有三类文件夹: 第一个是源代码文件(.v),可以自己写很多模块(函数库) 第二个是约束文件(.xdc),管脚赋值文件,这个感觉写着还很麻烦,需要将自己写的输入输出变量和硬件口对应起来。 本文可能有一些问题,可能之后的笔记会对此进行修正。如果大家觉得有问题,感谢大家提醒!!! |

【本文地址】

今日新闻 |

推荐新闻 |

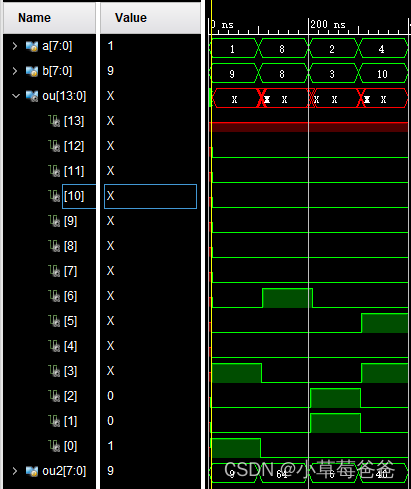

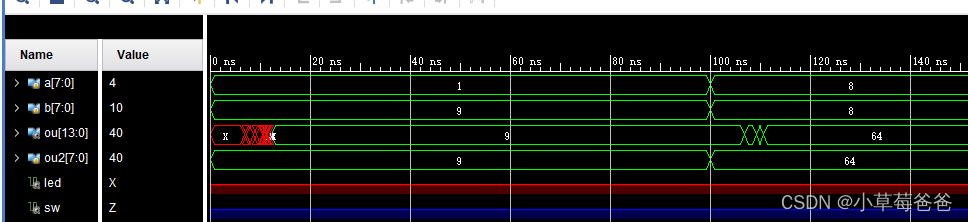

第三个是运行仿真,里面: 1.行为仿真:比如在测试某个模块功能时,只需要写一个.v的激励文件测试该模块。以下四种会考虑电路情况

第三个是运行仿真,里面: 1.行为仿真:比如在测试某个模块功能时,只需要写一个.v的激励文件测试该模块。以下四种会考虑电路情况

4.实现功能仿真:会将生成模块的逻辑器件映射到板子中的基本逻辑单元中,无延迟,所以和行为仿真相同

4.实现功能仿真:会将生成模块的逻辑器件映射到板子中的基本逻辑单元中,无延迟,所以和行为仿真相同

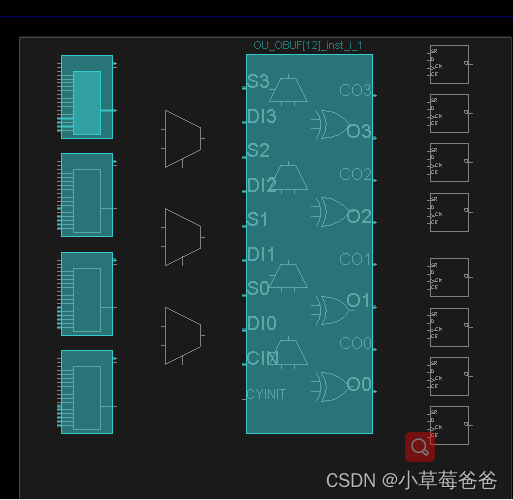

第五个是综合分析,可以画出实际情况会用到哪些具体原件的原理图。门级网表(因为用了for循环,叠加着加电路,图乱)

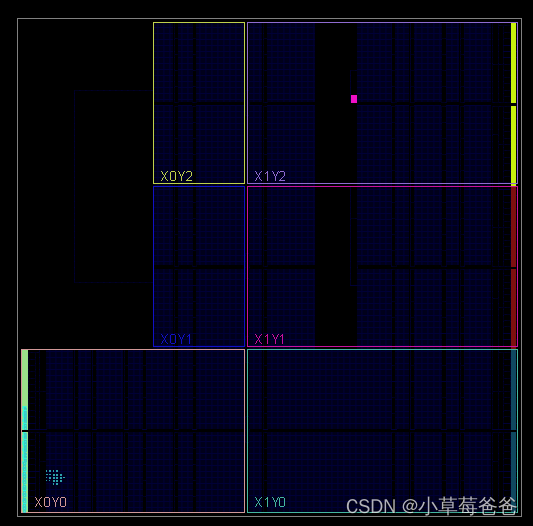

第五个是综合分析,可以画出实际情况会用到哪些具体原件的原理图。门级网表(因为用了for循环,叠加着加电路,图乱)  第六个是实现分析,会画出在板子上,用到哪些区域的哪些逻辑单元(LUT、乘法器、IO等)。实现级

第六个是实现分析,会画出在板子上,用到哪些区域的哪些逻辑单元(LUT、乘法器、IO等)。实现级  距离拉近后:

距离拉近后:  再拉近:

再拉近:

第三个是激励文件,一般需要设置成top顶层文件(主函数)。里面可以把模块用上。但这个是不是和那个《块设计》冲突了,这个地方还不懂,过几天试一试看看。

第三个是激励文件,一般需要设置成top顶层文件(主函数)。里面可以把模块用上。但这个是不是和那个《块设计》冲突了,这个地方还不懂,过几天试一试看看。