固体微电子学与半导体物理学(八) |

您所在的位置:网站首页 › p型半导体的结构 › 固体微电子学与半导体物理学(八) |

固体微电子学与半导体物理学(八)

|

九、半导体表面和MIS结构

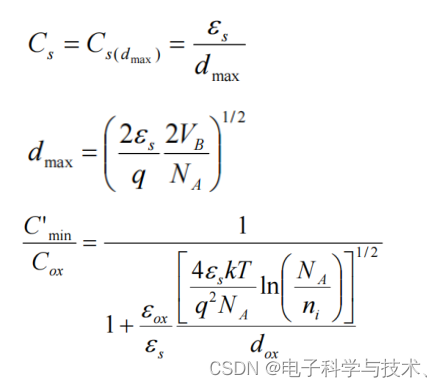

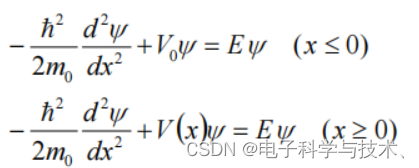

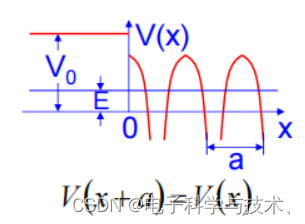

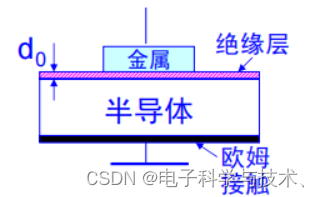

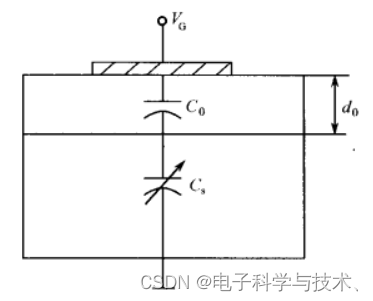

九、半导体表面和MIS结构 9.1 表面态 9.1.1 表面的特质 9.1.2 理想表面 9.2 表面电场效应 9.2.1 空间电荷层 9.2.2 半导体表面电场、电势和电容半导体表面电场、电势和电容 9.2.3 半导体表面层的五种基本状态 9.3 氧化层和Si--SiO2系统性质 9.4 MIS结构和C-V特性 9.4.1 理想MIS和C-V曲线 9.4.2 MIS能带图 9.5 实际MIS的C-V曲线 9.5.1 功函数差影响 9.5.2 绝缘层电荷影响 9.5.3 Bias-Temperature温度偏压实验 9.6 表面电导和迁移率 简述MOSFET 对于MESFET: MOSFET: HEMT(高电子迁移率晶体管) FGMOS(FLASH浮栅晶体管) 共基极电路 共射电路 Cs:表面空间电荷层电容 Qs:表面电荷 VB:费米电势差/半导体内中线和费米能级的电势差 Vs:表面电势差 LD:德拜长度 Xd:表面耗尽层宽度 VFB:平带电压 CFB:平带电容 Tth:热弛豫时间 C0:绝缘层单位面积电容 d0:绝缘层厚度 QM:金属表面的面电荷密度 dVG:小信号电压变化量 9.1 表面态 9.1.1 表面的特质 1. 表面处晶体的周期场中断 2. 表面往往易受到损伤、氧化和沾污,从而影响器件的稳定性 3. 表面往往需要特殊保护措施,如钝化等 4. 表面是器件制备的基础,如MOSFET等 9.1.2 理想表面 以一维周期性晶格为例,引入薛定谔方程 上式解:等同于一维无限周期场的解

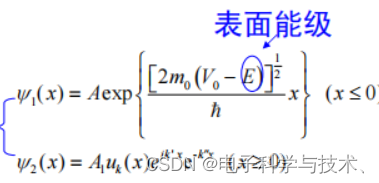

下式解:对应于表面态

上式解:等同于一维无限周期场的解

下式解:对应于表面态

—— 在表面(x=0)两边,波函数指数衰减,说明电子分布几率主要集中在x=0处,即电子被局限

在表面附近。波函数本来就是指数衰减,平方变成概率函数ρ(x),衰减只会更快。

—— 每个表面原子对应禁带中一个表面能级,这些能级组成表面能带

—— 以Si为例,晶体表面的原子密度是10^15/cm³ ,悬挂键(表面未饱和键)的密度为10^15/cm³

9.2 表面电场效应

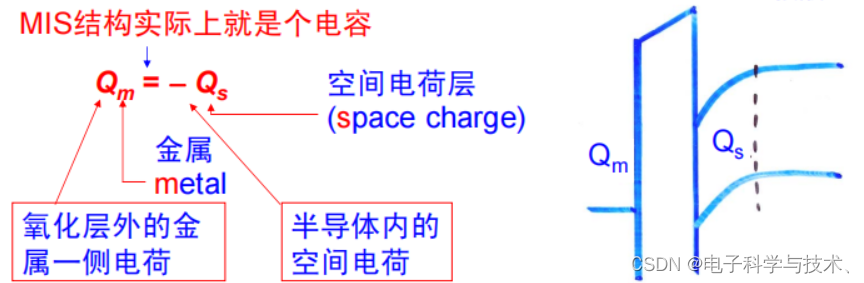

9.2.1 空间电荷层

半导体表面产生电场原因:外加偏压、功函数差、电荷 (固定电荷, 界面态等)

半导体中自由载流子密度低得多,对应Qs的电荷量需要分布在一定厚度的表面层内,这个带电的

表面层叫做空间电荷层

—— 在表面(x=0)两边,波函数指数衰减,说明电子分布几率主要集中在x=0处,即电子被局限

在表面附近。波函数本来就是指数衰减,平方变成概率函数ρ(x),衰减只会更快。

—— 每个表面原子对应禁带中一个表面能级,这些能级组成表面能带

—— 以Si为例,晶体表面的原子密度是10^15/cm³ ,悬挂键(表面未饱和键)的密度为10^15/cm³

9.2 表面电场效应

9.2.1 空间电荷层

半导体表面产生电场原因:外加偏压、功函数差、电荷 (固定电荷, 界面态等)

半导体中自由载流子密度低得多,对应Qs的电荷量需要分布在一定厚度的表面层内,这个带电的

表面层叫做空间电荷层

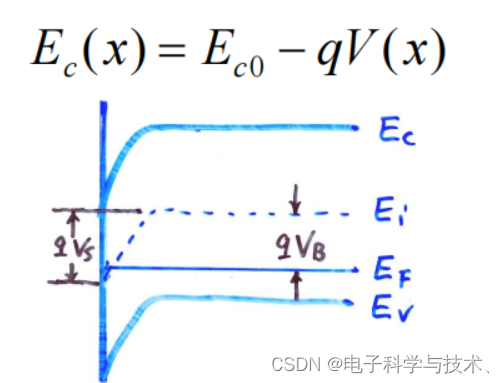

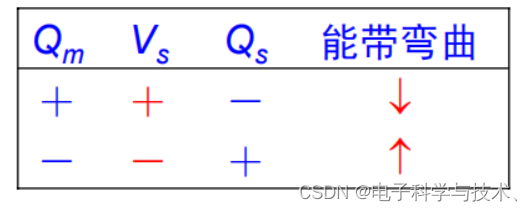

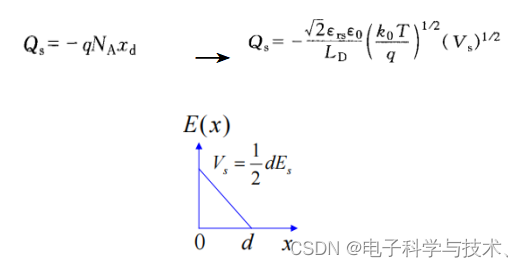

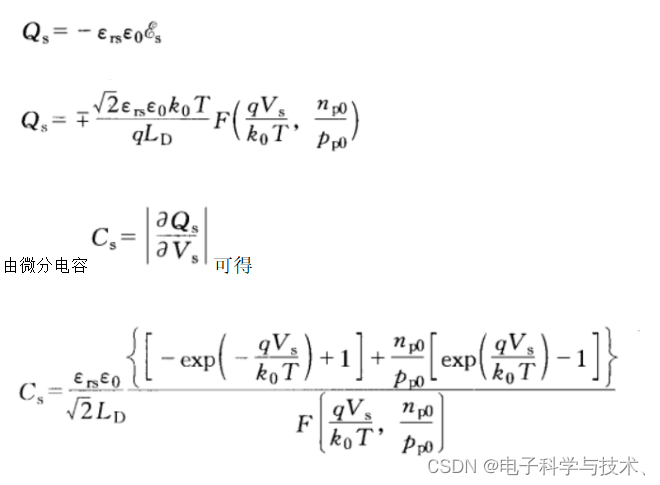

能带弯曲方向判断(助记): 解空间电荷层的泊松方程: 我们做如下假设: 1. 半导体表面是个无限大的面→一维近似 2. 半导体体内电中性,即半导体厚度 >> 空间电荷层厚度 3. 半导体均匀掺杂 4. 非简并统计适用于空间电荷层 5. 不考虑量子效应

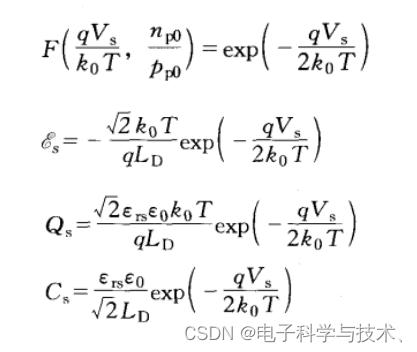

表面空穴浓度分布在德拜长度以内,可以近似认为是薄层电荷  根据高斯定理,由于指向半导体内的电场为正电场,所以必须加上一个负号来翻转方向。又由于半

导体表面积累的是负电荷,所以此时再加上一个负号。

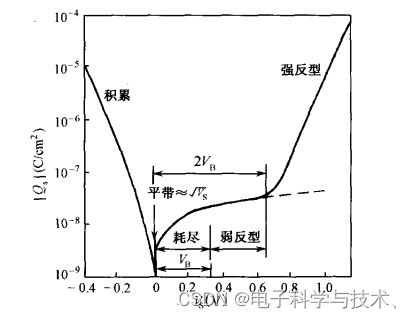

9.2.3 半导体表面层的五种基本状态

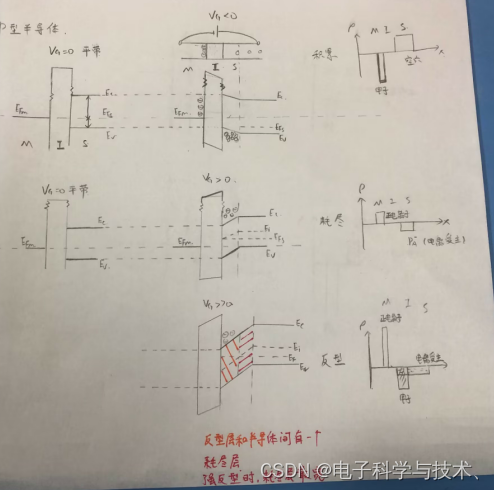

以p型半导体为例:

Ⅰ、多子积累:外加电压小于0,表面势以及表面层内

电势都是负的。表面能带下弯表面

空穴积累

Ⅱ、平带:当外加电压Vc=0时,表面势V=0,表面处能带不发生弯曲,称做平带状态。

Ⅲ、耗尽:当外加电压Vc为正但其大小还不足以使表面处禁带中央能量E;Ei能带弯曲到费米能级

以下时,表面不会出现反型,空间电荷区处于空穴耗尽状态。

Ⅳ、反型:随着外加正电压Vc增大,表面处禁带中央能值E;可以下降到Ei以下,即出现反型层。

反型状态可分为

强反型和

弱反型两种情况

Ⅴ、深耗尽:在金属与半导体间加一脉冲阶跃或高频正弦波形成的正电压,由于空间电荷层内的少

数载流子的产生速率赶不上电压的变化,反型层来不及建立,只有靠耗尽层延伸向半导体内

深处而产生大量

受主负电荷以满足电中性条件。因此,这种情况时耗尽层的宽度很大,可远

大于强反型的最大耗尽层宽度,且宽度随电压幅度的增大而增大,这种状态称为深耗尽状态。

根据高斯定理,由于指向半导体内的电场为正电场,所以必须加上一个负号来翻转方向。又由于半

导体表面积累的是负电荷,所以此时再加上一个负号。

9.2.3 半导体表面层的五种基本状态

以p型半导体为例:

Ⅰ、多子积累:外加电压小于0,表面势以及表面层内

电势都是负的。表面能带下弯表面

空穴积累

Ⅱ、平带:当外加电压Vc=0时,表面势V=0,表面处能带不发生弯曲,称做平带状态。

Ⅲ、耗尽:当外加电压Vc为正但其大小还不足以使表面处禁带中央能量E;Ei能带弯曲到费米能级

以下时,表面不会出现反型,空间电荷区处于空穴耗尽状态。

Ⅳ、反型:随着外加正电压Vc增大,表面处禁带中央能值E;可以下降到Ei以下,即出现反型层。

反型状态可分为

强反型和

弱反型两种情况

Ⅴ、深耗尽:在金属与半导体间加一脉冲阶跃或高频正弦波形成的正电压,由于空间电荷层内的少

数载流子的产生速率赶不上电压的变化,反型层来不及建立,只有靠耗尽层延伸向半导体内

深处而产生大量

受主负电荷以满足电中性条件。因此,这种情况时耗尽层的宽度很大,可远

大于强反型的最大耗尽层宽度,且宽度随电压幅度的增大而增大,这种状态称为深耗尽状态。

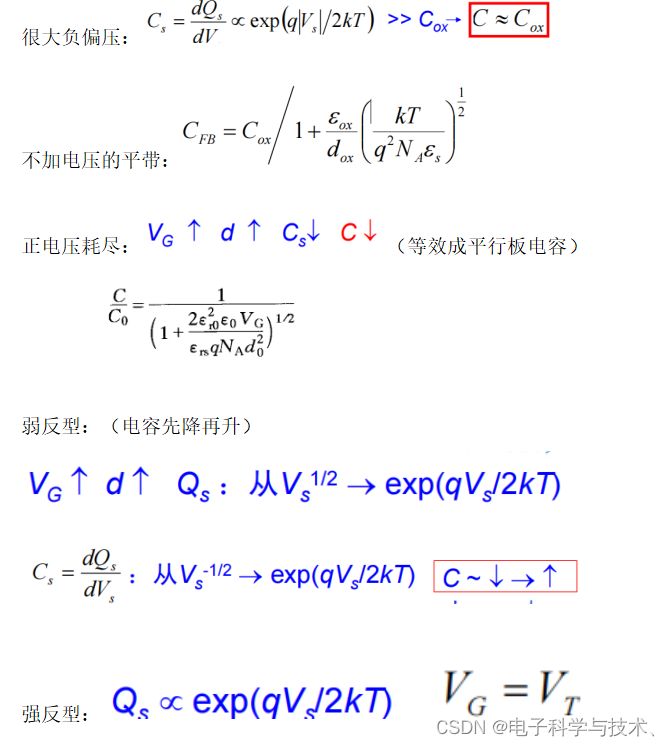

Ⅰ、Es Qs Cs正比于 exp【-qVs/2kt】,Vs<0

Ⅰ、Es Qs Cs正比于 exp【-qVs/2kt】,Vs<0

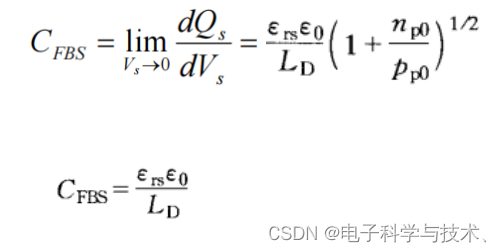

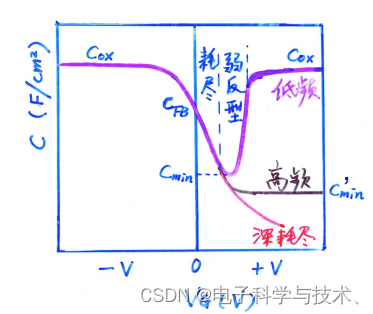

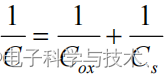

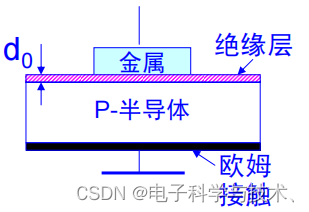

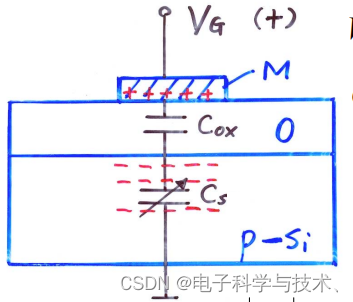

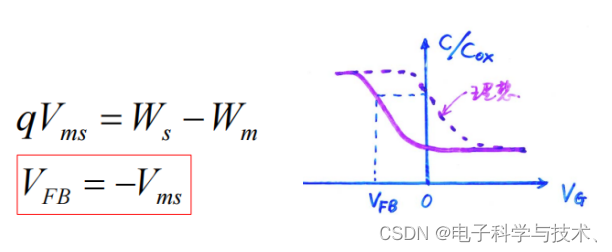

氧化层电容和表面层电容是串联关系: 值得注意的是,我们能从图中得出很多有用的信息 1. 利用左平段,我们可以得到绝缘层厚度d0:d0=ε0εr/d 2. 利用积累区电容公式平带点C,可以求掺杂浓度和功函数Ws(CFB越高,证明掺杂浓度越高) 3. 费米势只与掺杂浓度有关 高频情况下( 10^4~10^6 Hz) 高频情况下出现偏差的原因是:反型层中电子的产生与复合跟不上高 频信号的变化。QS的变化只 能靠耗尽层的电荷变化实现,强反型时耗尽层已达最大厚度。 少子不响应高频信号变化,直流少子积累在O-S界面。

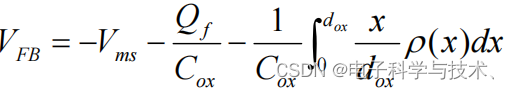

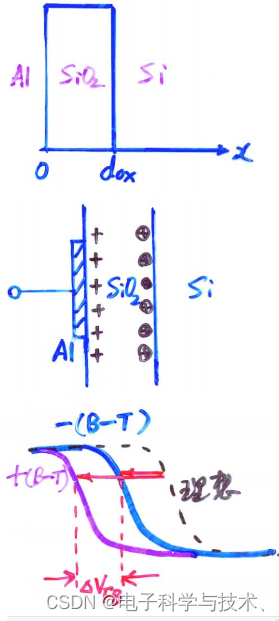

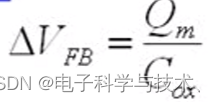

9.5.2 绝缘层电荷影响

平带电压=接触电势差+固定正电荷电压+可动电荷电压

9.5.2 绝缘层电荷影响

平带电压=接触电势差+固定正电荷电压+可动电荷电压

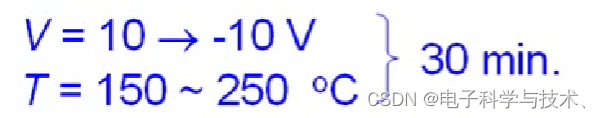

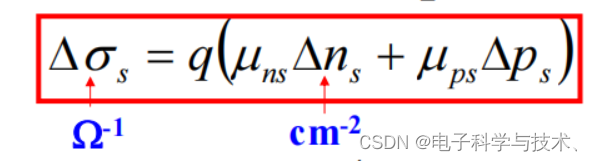

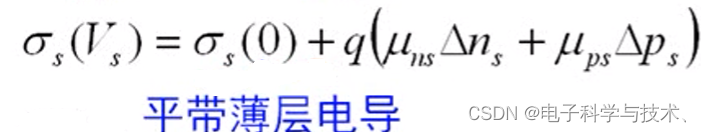

实验作用:测量二氧化硅层可动电荷密度 实验条件: 在-10V电压作用下,钠离子靠近半导体一侧。这时我们需要一个较大的负电压来屏蔽这些正电荷的影响,因此C-V曲线左移(可动电压贡献平带电压) z在+10V电压作用下,钠离子靠近金属一侧,此时金氧间的电阻是无穷大的,Qf/Cox趋近于0,也就不再需要用额外的负电压来平衡正离子(可动电荷不贡献平带电压) 所以。两条曲线的横向间距就是可动电荷贡献的平带电压,可用于计算二氧化硅层的电荷密度

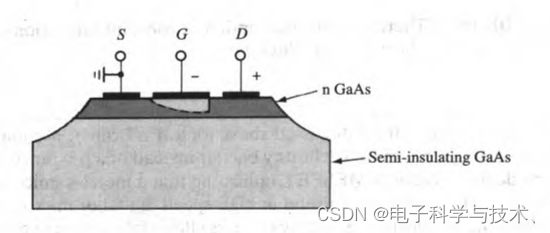

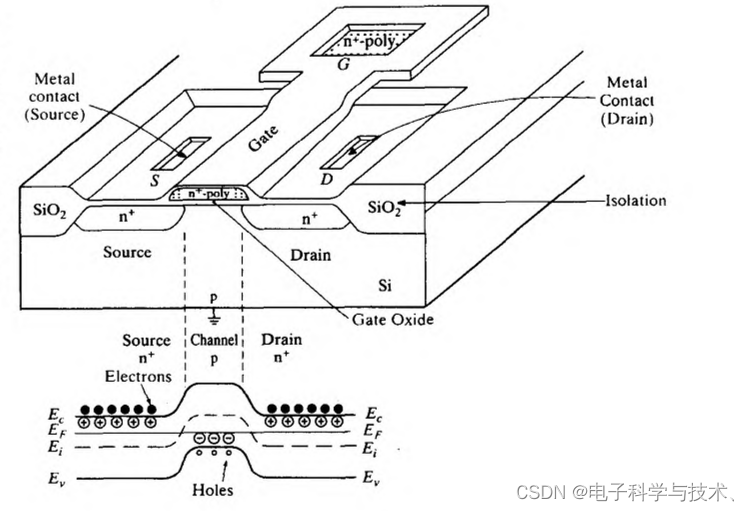

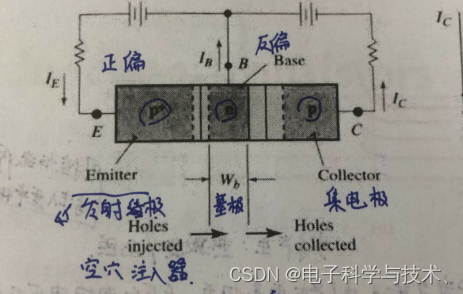

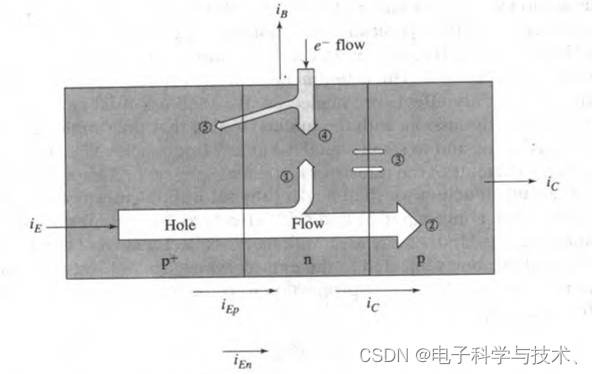

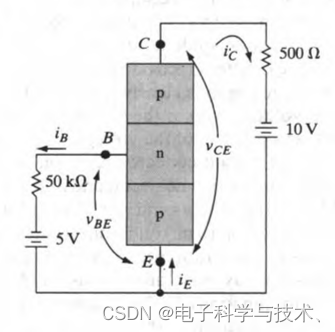

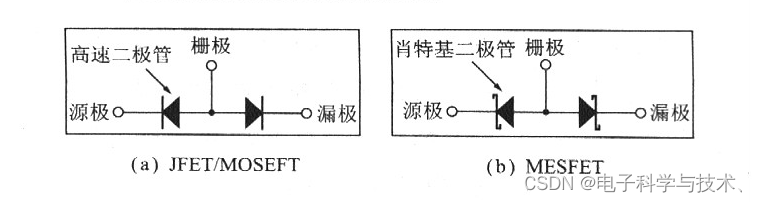

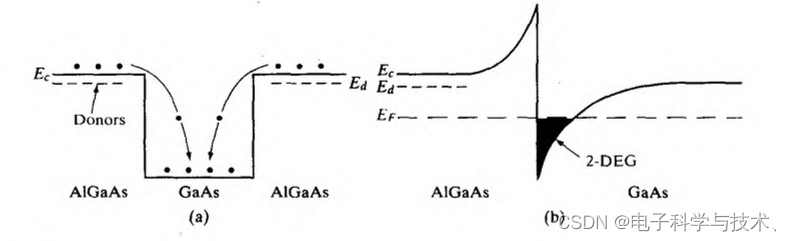

MOSFET由MOS(Metal Oxide Semiconductor金属氧化物半导体)+FET(Field Effect Transistor场效应晶体管)这个两个缩写组成。即通过给金属层(M-金属铝)的栅极和隔着氧化层(O-绝缘层SiO2)的源极施加电压,产生电场的效应来控制半导体(S)导电沟道开关的场效应晶体管。由于栅极与源极、栅极与漏极之间均采用SiO2绝缘层隔离,MOSFET因此又被称为绝缘栅型场效应管。 市面上大家所说的功率场效应晶体管通常指绝缘栅MOS型(Metal Oxide Semiconductor FET),简称功率MOSFET(Power MOSFET)。实际上场效应管分为结型和绝缘栅两种不同的结构。场效应管是利用输入回路的电场效应来控制输出回路电流的一种半导体器件。它仅靠半导体中的多数载流子导电,又称为单极型晶体管。结型功率场效应晶体管一般称作静电感应晶体管(Static Induction Transistor-SIT)。其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,但其电流容量小,耐压低,一般只适用于功率不超过10kW的电力电子装置。MOSFET功率场效应晶体管,大多数用作开关和驱动器,工作于开关状态,耐压从几十伏到上千伏,工作电流可达几安培到几十安。功率MOSFET基本上都是增强型MOSFET,它具有优良的开关特性。 MOSFET分类 按导电沟道类型分可分为:P型 和 N型 按栅极电压幅值可分为:增强型和耗尽型 另外还有一种是MESFET(金属-半导体场效应晶体管) 对于MESFET:

对于MESFET:

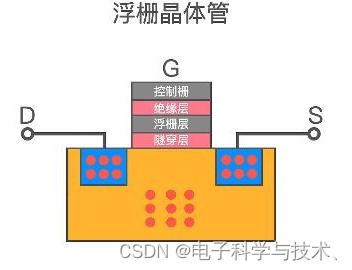

FGMOS(FLASH浮栅晶体管)

制作

闪存的主要原理

在p-MOSFET的基础上,只是把栅极改变为一个浮空的栅极——浮栅(用多晶硅制作);该浮栅被

优质SiO2包围着,其中的电荷可较长时间地保存起来。要去除(擦除)该器件存储的电荷(信

号)时,一般比较困难,即需要高能量光子(紫外光或者X射线)等的照射才能使得浮栅中的电子

被释放出来。

根据MOS器件的导通与否,就可以得知浮栅中是否存储有电荷;这也就意味着FAMOS可以实现信

号(电荷)的

存储和检测,即具有存储器的功能。

FGMOS(FLASH浮栅晶体管)

制作

闪存的主要原理

在p-MOSFET的基础上,只是把栅极改变为一个浮空的栅极——浮栅(用多晶硅制作);该浮栅被

优质SiO2包围着,其中的电荷可较长时间地保存起来。要去除(擦除)该器件存储的电荷(信

号)时,一般比较困难,即需要高能量光子(紫外光或者X射线)等的照射才能使得浮栅中的电子

被释放出来。

根据MOS器件的导通与否,就可以得知浮栅中是否存储有电荷;这也就意味着FAMOS可以实现信

号(电荷)的

存储和检测,即具有存储器的功能。

参考资料: 半导体物理与器件,(第四版),赵毅强、姚素英等译,电子工业出版社。 半导体物理学,(第七版),刘恩科、朱秉升、罗晋生等,电子工业出版社。 晶体管原理与设计,陈星弼张庆中等,电子工业出版社。 光电子技术,(第三版),狄红卫、朱思祁、张永林等,高等教育出版社。 电子科技大学刘诺公开课。 蒋玉龙半导体物理公开课。 |

【本文地址】

今日新闻 |

推荐新闻 |