【ZYNQ】学习笔记:VDMA彩条显示实验Part2 |

您所在的位置:网站首页 › ps百分之百显示 › 【ZYNQ】学习笔记:VDMA彩条显示实验Part2 |

【ZYNQ】学习笔记:VDMA彩条显示实验Part2

|

【学习视频】正点原子https://www.bilibili.com/video/BV11j411f7Co =================================================================== 【ZYNQ】学习笔记:VDMA彩条显示实验Part1 https://www.cnblogs.com/steven913/p/17298510.html =================================================================== 【学习笔记】 【1】端口定义

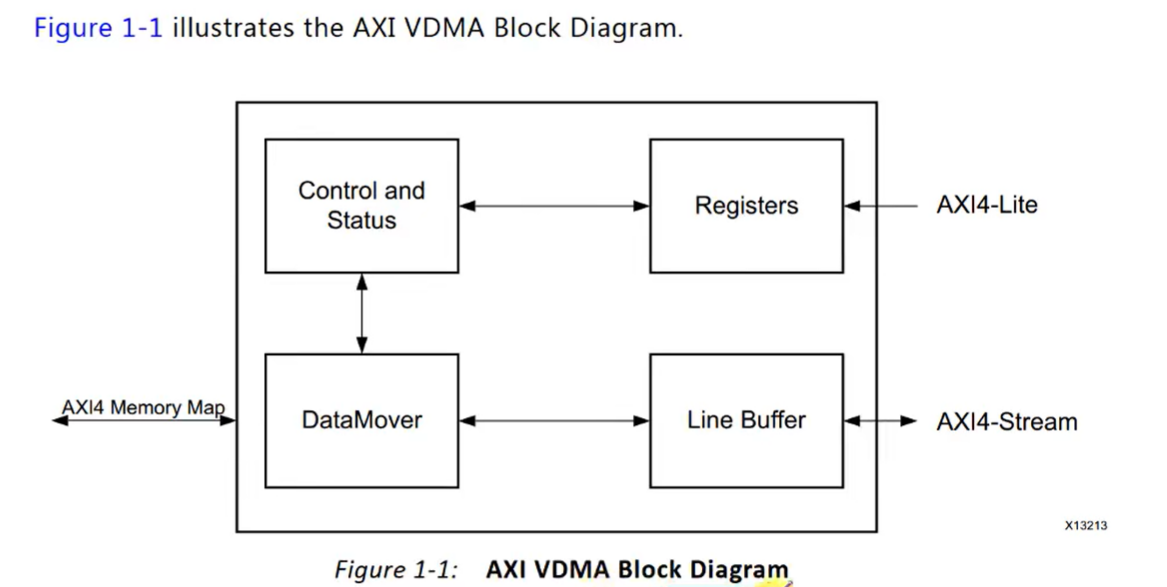

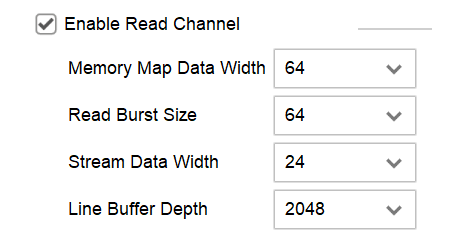

AXI4-Lite接口:用于配置VDMA; AXI4 Memory Map:存储映射接口; AXI4-Stream接口

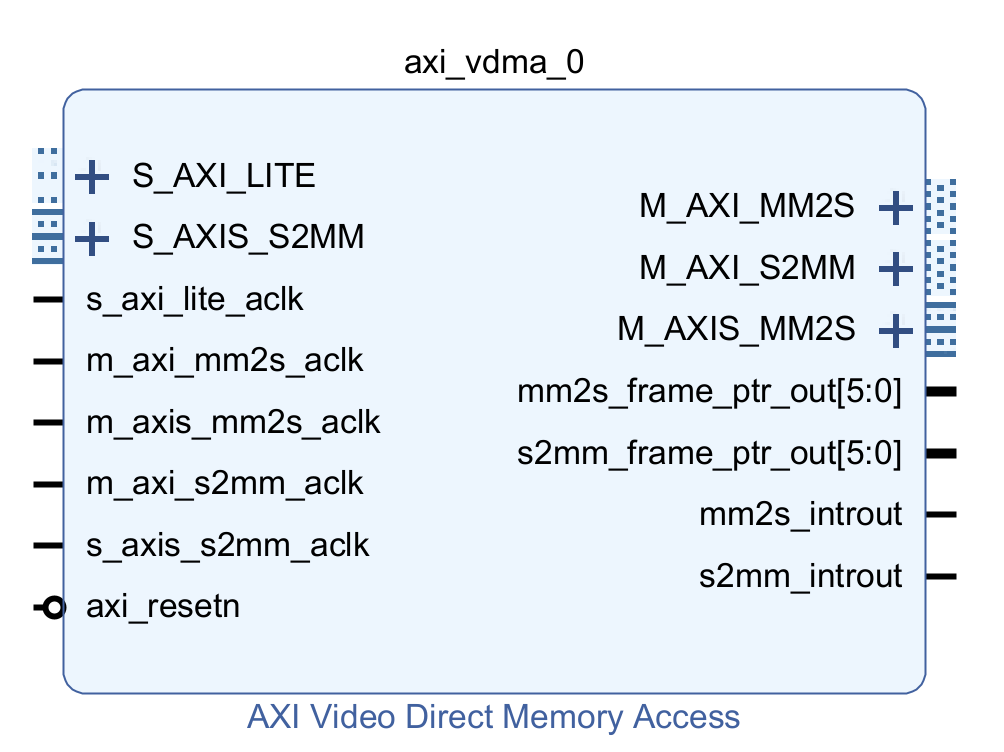

S_AXI_LITE:从(Slave)的AXI4-Lite接口,受到ZYNQ的PS端的配置,即连接到PS端的M_AXI_GP0接口。

S_AXIS_S2MM:AXI4-Stream的VDMA写路径,将数据从外部写入MM,所以VMDA为从(Slave),该接口开头为S。 M_AXIS_MM2S:AXI4-Stream的VDMA读路径,将数据从MM读出,所以VDMA为主(Master),该接口开头为M。

由于本次实验通过AXI4-Stream输出视频数据,故使用M_AXIS_MM2S接口。

M_AXI_MM2S、M_AXI_S2MM:存储映射接口,读写存储器DDR。

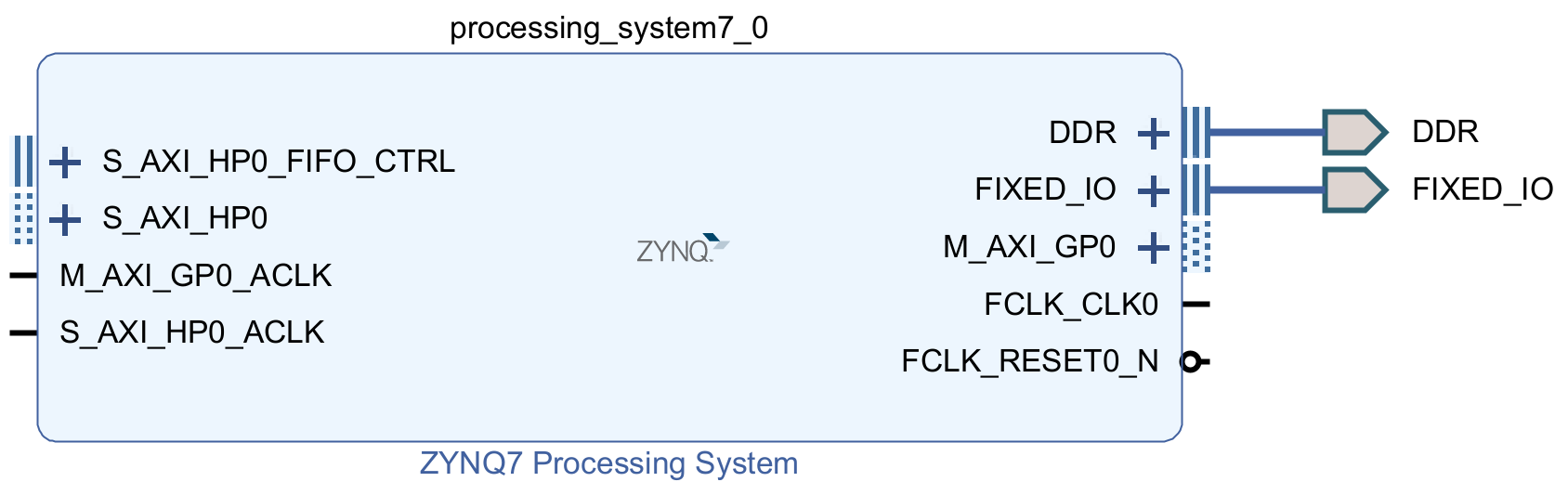

由于DDR位于ZYNQ的PS端,且本次实验仅用到VDMA的数据读取路径,故M_AXI_MM2S连接到PS端的S_AXI_HP0接口。 mm2s_frame_ptr_out[5:0]:帧指针信号,告诉我们读端口正在访问哪一个帧缓存。 s2mm_frame_ptr_out[5:0]:帧指针信号,告诉我们写端口正在访问哪一个帧缓存。 mm2s_introut:读端口中断信号 2smm_introut:写端口中断信号

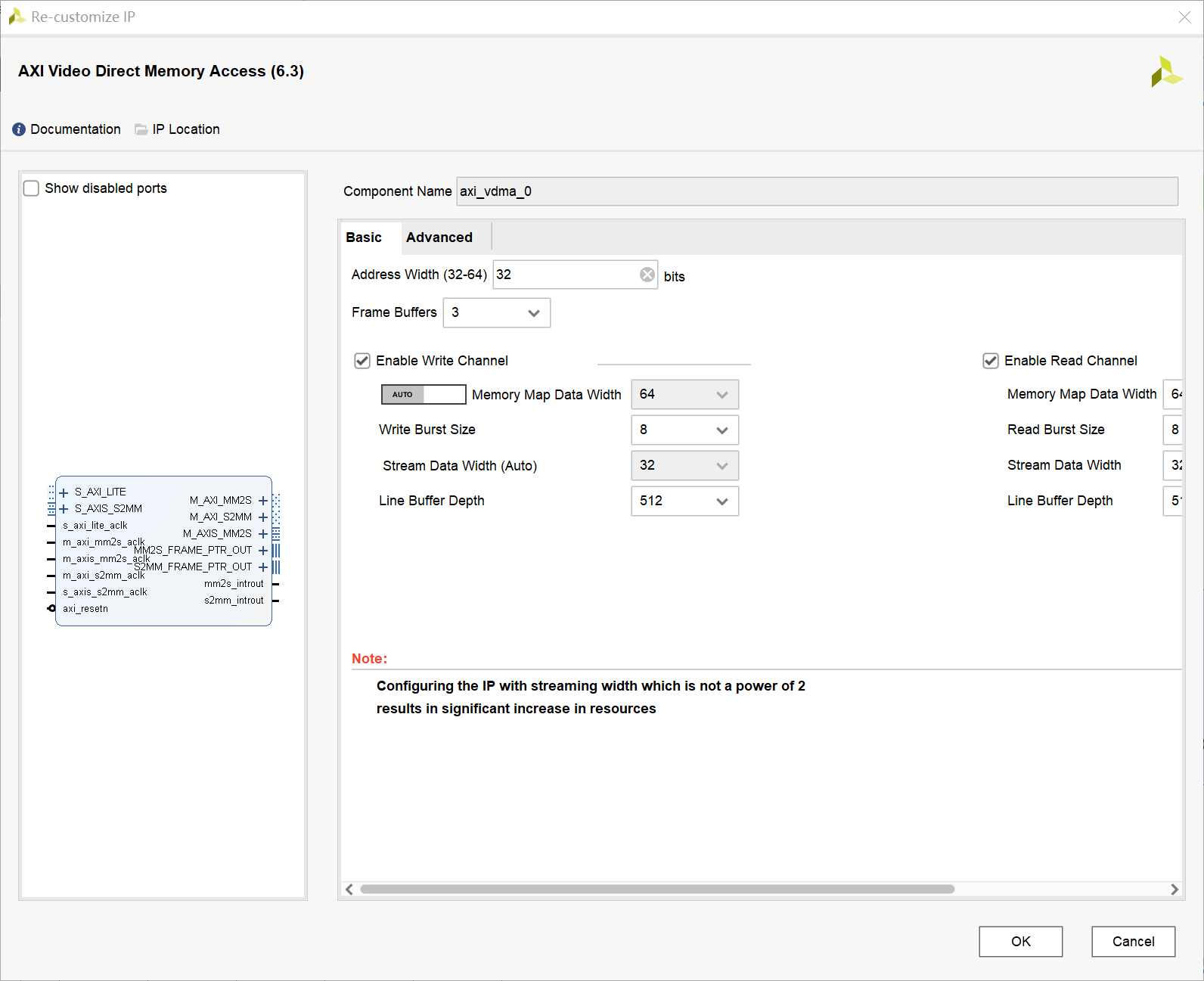

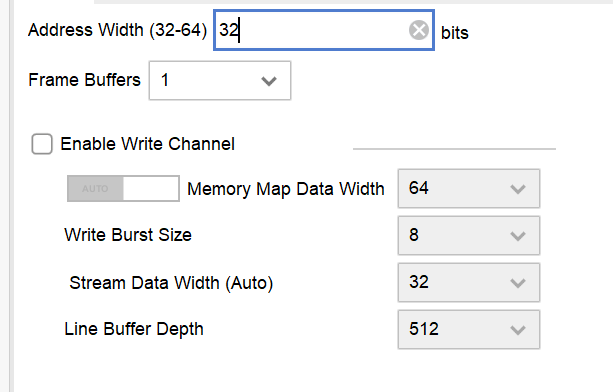

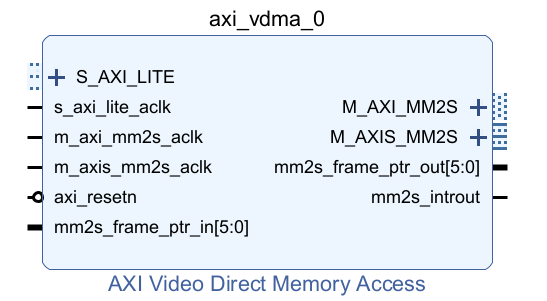

【2】VDMA配置

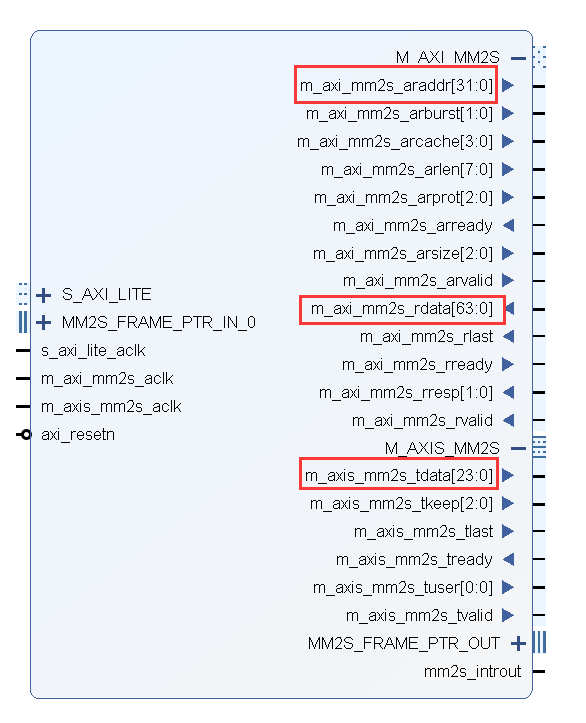

地址位宽(Address Width) n bit,最大能访问2^n个地址,n=32~64。 同时使能写通道(Write Channel)和读通道(Read Channel)时,帧缓存(Frame Buffers)一般设置为3。 本次实验仅使能读通道,帧缓存设置为1即可。 读通道数据位宽(Memory Data Width) 读通道突发长度(Read Burst Size):AXI4-Stream突发传输的大小,此处设为64bit。 Stream接口的数据位宽(Stream Data Width):由于我们读取的是RGB888的数据,故设为24bit。 行缓存深度(Line Buffer Depth):根据图像输出设备的需求进行选择。本实验打算输出1920bit,但这里没有刚好的,故设为2048bit。

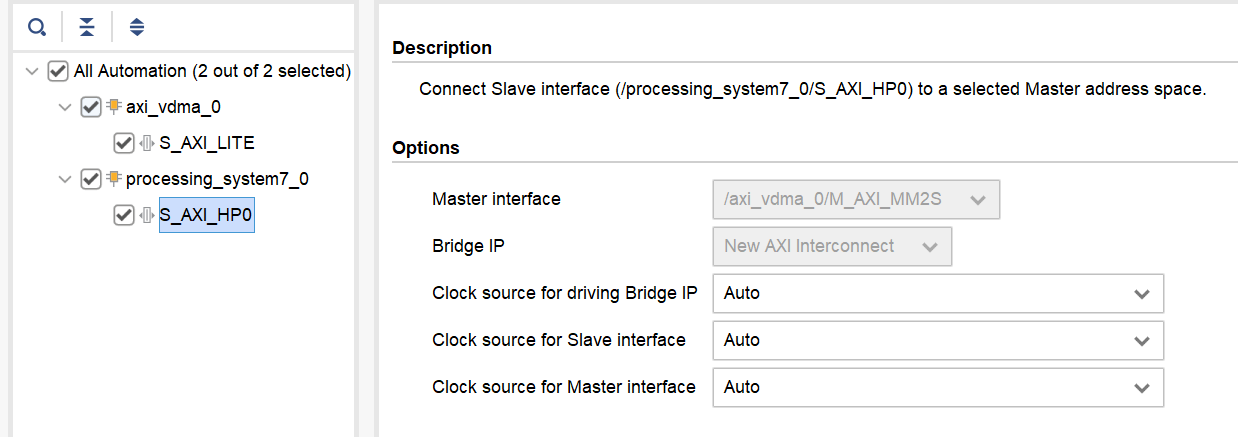

【3】自动连线

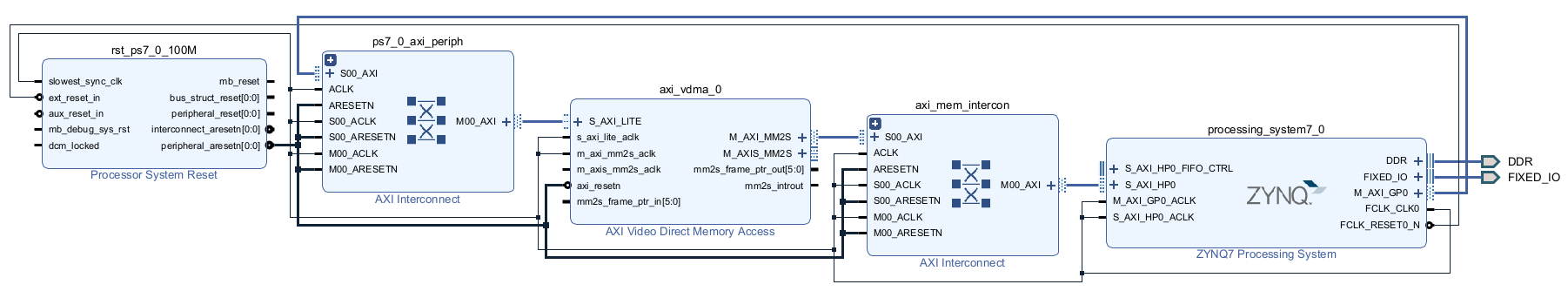

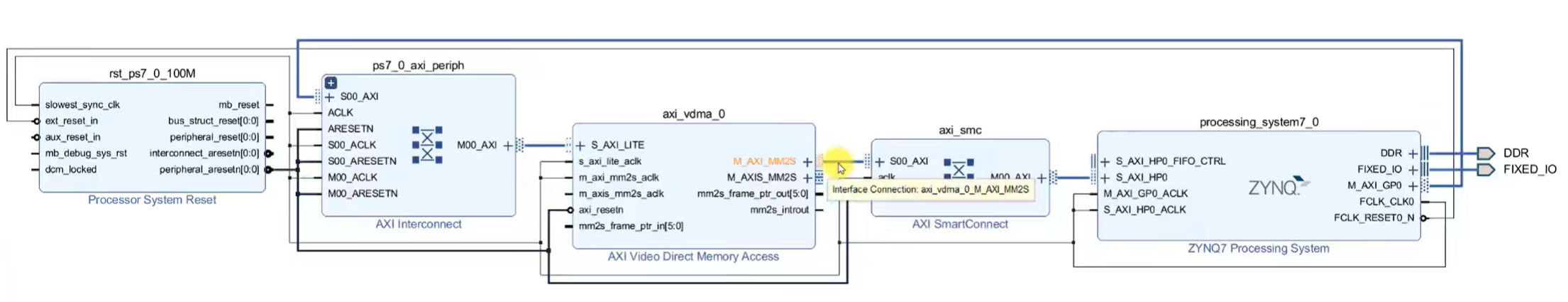

这里似乎出了一个小问题,即axi_vdma_0模块与ZYNQ的PS模块使用的是AXI互联,而不是AXI Smart连接;由于无法更改(进行自动连接配置时,Bridge IP为灰色),只能用AXI互联。不知道这在之后的实验中会有什么影响。我采用的时Vivado2022.2版本,正点原子为2018.3版本。 正点原子的教学视频采用的时AXI Smart连接,如下图:

AXI SmartConnect和AXI Interconnect IP核都是用于连接存储映射的IP核即MM2S和S2MM。 AXI SmartConnect被更加紧密地集成到了Vivado设计中,集成度高,需要的人为干预更少;AXI Interconnect可以用在所有的存储映射设计中。 针对中高性能、带宽的应用,使用SmartConnect可为我们提供更好的优化,即为系统提供更大的带宽和更低的延时;针对低性能(如 AXI4-Lite)设计可以采用AXI Interconnect,这也使得占用更小的设计面积(更少的器件数量)。 【4】导入AXI4-Stream to Video Out 并连线

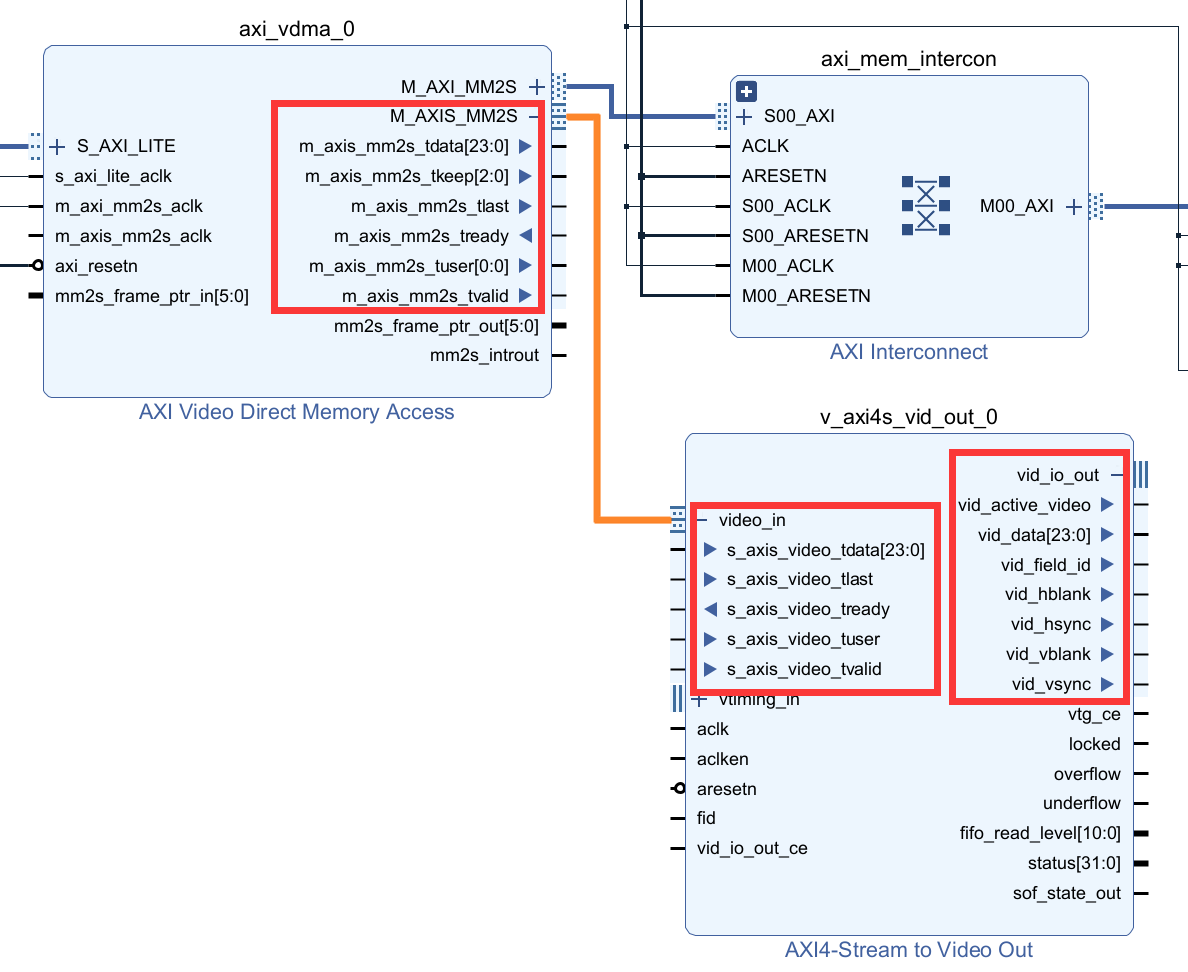

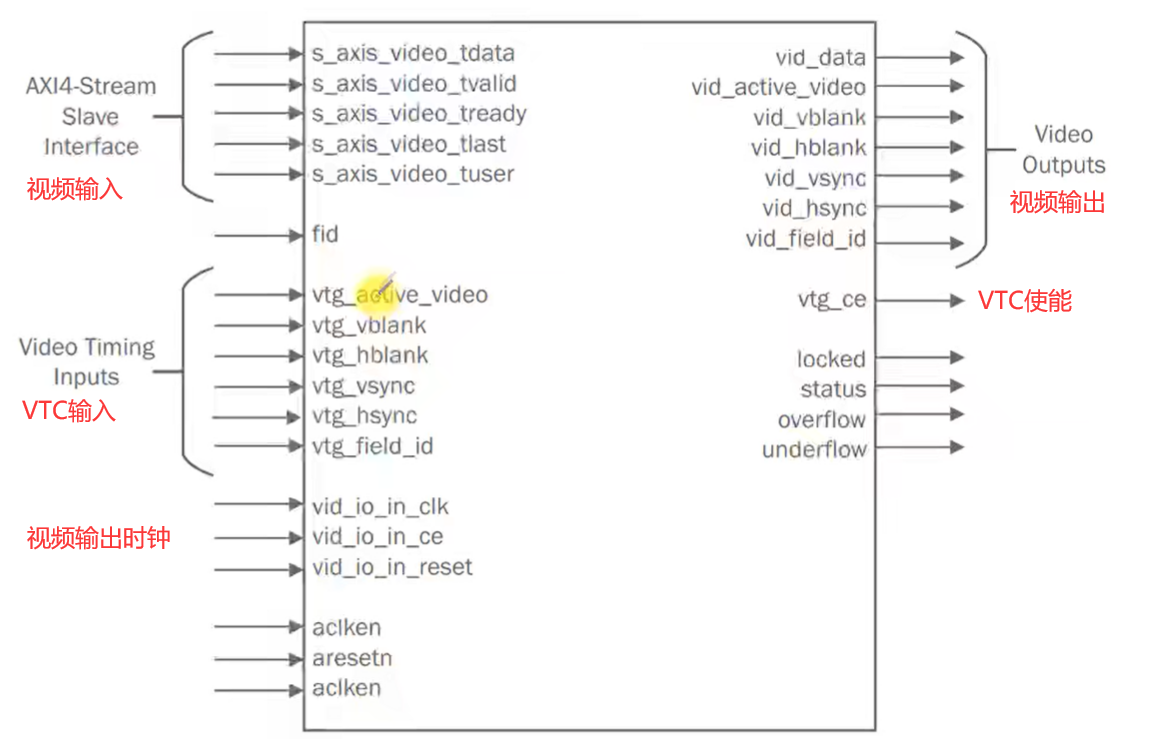

IP核AXI4-Stream to Video Out的作用是将AXI4-Stream信号转换为Video Out信号(可在LCD屏上显示)。 该IP核还需与Video Timing Controller(VTC)一同使用。 虽然IP核之间使用的是AXI4-Stream协议,但是整体视频系统(ZYNQ与各种显示设备之间)采用的却是独立的行同步、场同步信号以及时序信号,所以需要AXI4-Stream to Video Out这个IP核将处理IP核间信号的AXI4-Stream Video Protocol接口转换成视频系统所需要的独立同步信号和时序接口。这就是该IP核的作用和它出现的原因。

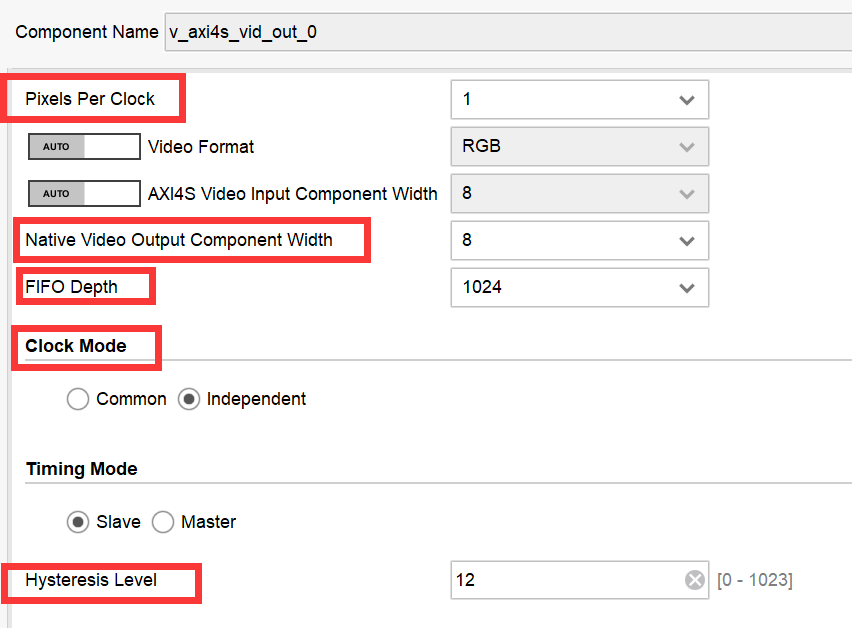

【5】配置AXI4-Stream to Video Out

每个时钟所处理的像素数量(Pixels Per Clock):1 视频输出的元件位宽(Native Video Output Component Width):我们输出的是RGB888,故每个通道的输出位宽为8bit,所以设置为8 FIFO深度(FIFO Depth):1024 时钟模式(Clock Mode):普通时钟(Common),AXI4-Stream的aclk与Video Clock相同,即同步时钟;独立时钟(Independent),AXI4-Stream的aclk与Video Clock不同,即异步时钟,此时会比Common模式多出一个vid_io_out_clk和vid_io_out_reset端口。 滞后等级(Hysteresis Level):为了把Stream接口输入的视频信号同步到VTC输入的时序信息上,所以在同步的过程中需要对输入的视频数据进行缓冲。滞后等级决定了需要缓存数据到什么样的程度才开始时序同步过程。滞后等级的最大值与FIFO深度保持一致。建议将其设置得小一些,以便IP核早一些开始进行时钟同步。 【6】AXI4-Stream to Video Out IP核的FIFO Depth(即Buffer缓冲深度)如何设置 如果FIFO太小,数据很有可能会被读空(数据空缺),导致视频输出数据的丢失和错位。(FIFO有满标志,所以一般不会溢出) 需要上游数据速率和下游视频输出时钟(速率)大致上相等。 如果输入Buffer的数据速率大于Buffer输出数据的速率,那么Buffer深度就可以设小一些; 如果输入Buffer的数据速率小于Buffer输出数据的速率,那么Buffer深度就可以设大一些。 【7】VTC的Slave模式 即,VDMA(根据输入视频数据和FIFO缓冲的大小)通过信号控制VTC什么时候产生输出时序。

减少向上游amster的反向压力;减小延迟和向下游的缓冲。 通过控制VTC来控制视频数据时序同步的过程(视频速率和VTC的相位关系),使得FIFO的读写速率大致相等(FIFO不空也不满)。 如果FIFO总是满的,FIFO会频繁向上级给出暂停输入的信号,导致上级FIFO也容易出现此情况,最终使得暂停信号不断向上传递造成系统问题。 【8】

当视频输入与VTC输入进行时序同步后,才会进行视频输出。

|

【本文地址】

今日新闻 |

推荐新闻 |