数电4 |

您所在的位置:网站首页 › pcm63解码器电路设计 › 数电4 |

数电4

译码器

1. 简介2. 二进制译码器2.1 真值表和输出逻辑表达式2.2 逻辑电路的实现采用二极管与门阵列实现CMOS门实现

2.3 拓展

3. 二-十进制译码器4. 用译码器设计组合逻辑电路4.1 实现特定的逻辑表达式4.1.1 逻辑函数转换4.1.2 得到电路图

4.2 实现全减器

5. 显示译码器5.1 半导体数码管(LED七段显示器)5.2 液晶显示器(LCD显示器)5.3 BCD-七段译码器真值表化简得逻辑表达式电路图工作电路

1. 简介

译码器是将每个输入的二进制代码译成对应的输出高、低电平信号,和编码器逆过程。常用的译码器分为二进制译码器、二-十进制译码器和显示译码器

2. 二进制译码器

二进制译码器:即将N位二进制代码译成

2

N

2^{N}

2N个高低电平信号,称为N线-

2

N

2^{N}

2N线译码器。如

N

=

3

N=3

N=3,则可译

2

N

=

8

2^{N} =8

2N=8个高低电平信号,称为3线-8线译码器图为3线-8线译码器的框图。其中:

A

2

~

A

0

A_{2} ~A_{0}

A2~A0是二进制代码输入端;

Y

7

~

Y

0

Y_{7} ~Y_{0}

Y7~Y0 为信号输出端  2.1 真值表和输出逻辑表达式

2.1 真值表和输出逻辑表达式

真值表 逻辑表达式 Y 0 = A 2 ′ A 1 ′ A 0 ′ = m 0 Y_{0}=A_{2}'A_{1}'A_{0}'=m_{0} Y0=A2′A1′A0′=m0 Y 1 = A 2 ′ A 1 ′ A 0 = m 1 Y_{1}=A_{2}'A_{1}'A_{0}=m_{1} Y1=A2′A1′A0=m1 Y 2 = A 2 ′ A 1 A 0 ′ = m 2 Y_{2}=A_{2}'A_{1}A_{0}'=m_{2} Y2=A2′A1A0′=m2 Y 3 = A 2 ′ A 1 A 0 = m 3 Y_{3}=A_{2}'A_{1}A_{0}=m_{3} Y3=A2′A1A0=m3 Y 4 = A 2 A 1 ′ A 0 ′ = m 4 Y_{4}=A_{2}A_{1}'A_{0}'=m_{4} Y4=A2A1′A0′=m4 Y 5 = A 2 A 1 ′ A 0 = m 5 Y_{5}=A_{2}A_{1}'A_{0}=m_{5} Y5=A2A1′A0=m5 Y 6 = A 2 A 1 A 0 ′ = m 6 Y_{6}=A_{2}A_{1}A_{0}'=m_{6} Y6=A2A1A0′=m6 Y 7 = A 2 A 1 A 0 = m 7 Y_{7}=A_{2}A_{1}A_{0}=m_{7} Y7=A2A1A0=m7 所以也称为最小项译码器(最小项:按照普通二进制进位写下去) 2.2 逻辑电路的实现 采用二极管与门阵列实现设

V

c

c

=

5

V

Vcc=5V

Vcc=5V,输入信号的高低电平为

3

V

3V

3V和

0

V

0V

0V,二极管导通压降为

0.7

V

0.7V

0.7V

S = S 3 S 2 S 1 S = S_{3}S_{2}S_{1} S=S3S2S1 当附加控制端 S 1 = 0 S_{1} =0 S1=0或者 S 2 ′ + S 3 ’ = 1 S_{2}'+S_{3}’=1 S2′+S3’=1时,译码器被禁止工作,输出端状态全部为高电平当 S 1 = 1 , S 2 ′ + S 3 ′ = 0 S_{1} =1,S_{2}' + S_{3}' =0 S1=1,S2′+S3′=0时,译码器处于工作状态Y i ′ = ( S m i ) ′ Y_{i}'=(Sm_{i})' Yi′=(Smi)′ 此译码器也是数据分配器,当 S 2 ′ S_{2} ' S2′ 和 S 3 ′ S_{3}' S3′为0,数据1由 S 1 S_{1} S1输入0输出位置由 A 2 A 1 A 0 A_{2}A_{1}A_{0} A2A1A0来确定 2.3 拓展试用两片3线-8线译码器74HC138组成4线-16线译码器,将输出的4位二进制代码

D

3

D

2

D

1

D

0

D_{3} D_{ 2} D_{ 1} D_{ 0}

D3D2D1D0 译成16个独立的低电平信号

Z

0

′

~

Z

15

′

Z_{ 0}' ~ Z_{ 15}'

Z0′~Z15′ 解:需要4个输入地址线,故要除了74HC138的3个输入端外,还要利用附加控制端,根据74HC138功能表,利用附加控制输入端的特点(如下图),当

S

1

=

1

S_{1}=1

S1=1且

S

2

′

+

S

3

’

=

0

S_{2}'+S_{3}’=0

S2′+S3’=0,由第一片输出,当

S

2

′

+

S

3

’

=

1

S_{2}'+S_{3}’=1

S2′+S3’=1第二片输出 二-十进制译码器就是将10个BCD代码(8421)译成10个高低电平的输出信号 BCD 码 以 外 的 伪 码(1010~1111),输出均无低电平信号产生 74HC42即为二-十进制的译码器 其内部逻辑图如图所示 其输出端逻辑式为

Y

I

′

=

m

i

′

(

i

=

0...9

)

Y_{I}'=m_{i}'(i=0...9)

YI′=mi′(i=0...9) 利用74HC138设计一个多输出的组合逻辑电路,输出逻辑函数式为 Z 1 = A C ′ + A ′ B C + A B ′ C Z_{1} = AC'+A'BC+AB'C Z1=AC′+A′BC+AB′C Z 2 = B C + A ′ B ′ C Z_{2}=BC+A'B'C Z2=BC+A′B′C Z 3 = A ′ B + A B ′ C Z_{3}=A'B+AB'C Z3=A′B+AB′C Z 4 = A ′ B C ′ + B ′ C ′ + A B C Z_{4}=A'BC'+B'C'+ABC Z4=A′BC′+B′C′+ABC 4.1.1 逻辑函数转换化成最小项之和 Z 1 = A C ′ + A ′ B C + A B ′ C Z_{1} = AC'+A'BC+AB'C Z1=AC′+A′BC+AB′C = A ( B + B ′ ) C ′ + A ′ B C + A B ′ C =A(B+B')C'+A'BC+AB'C =A(B+B′)C′+A′BC+AB′C = A B C ′ + A B ′ C ′ + A ′ B C + A B ′ C =ABC'+AB'C'+A'BC+AB'C =ABC′+AB′C′+A′BC+AB′C = m 3 + m 4 + m 5 + m 6 =m_{3}+m_{4}+m_{5}+m_{6} =m3+m4+m5+m6 同样的道理,得到下面的式子: Z 2 = m 1 + m 3 + m 7 Z_{2}=m_{1}+m_{3}+m_{7} Z2=m1+m3+m7 Z 3 = m 2 + m 3 + m 5 Z_{3}=m_{2}+m_{3}+m_{5} Z3=m2+m3+m5 Z 4 = m 0 + m 2 + m 4 + m 7 Z_{4}=m_{0}+m_{2}+m_{4}+m_{7} Z4=m0+m2+m4+m7 化成最小项的取反 利用反演定理: Z 1 = ( m 3 ′ m 4 ′ m 5 ′ m 6 ′ ) ′ Z_{1} =(m_{3}'m_{4}'m_{5}'m_{6}')' Z1=(m3′m4′m5′m6′)′ Z 2 = ( m 1 ′ m 3 ′ m 7 ′ ) ′ Z_{2}=(m_{1}'m_{3}'m_{7}')' Z2=(m1′m3′m7′)′ Z 3 = ( m 2 ′ m 3 ′ m 5 ′ ) ′ Z_{3}=(m_{2}'m_{3}'m_{5}')' Z3=(m2′m3′m5′)′ Z 4 = ( m 0 ′ m 2 ′ m 4 ′ m 7 ′ ) ′ Z_{4}=(m_{0}'m_{2}'m_{4}'m_{7}')' Z4=(m0′m2′m4′m7′)′ 4.1.2 得到电路图

试利用74HC138及与非门实现全减器,设A为被减数,B为减数, C I C_{I} CI 为低位的借位,D为差, C O C_{O} CO 为向高位的借位 写出真值表 写出逻辑表达式并化简

D

=

(

m

1

m

2

′

m

4

′

m

7

)

′

D=(m_{1}m_{2}'m_{4}'m_{7})'

D=(m1m2′m4′m7)′

C

=

(

m

1

m

2

′

m

3

′

m

7

)

′

C=(m_{1}m_{2}'m_{3}'m_{7})'

C=(m1m2′m3′m7)′电路图 写出逻辑表达式并化简

D

=

(

m

1

m

2

′

m

4

′

m

7

)

′

D=(m_{1}m_{2}'m_{4}'m_{7})'

D=(m1m2′m4′m7)′

C

=

(

m

1

m

2

′

m

3

′

m

7

)

′

C=(m_{1}m_{2}'m_{3}'m_{7})'

C=(m1m2′m3′m7)′电路图  5. 显示译码器

5. 显示译码器

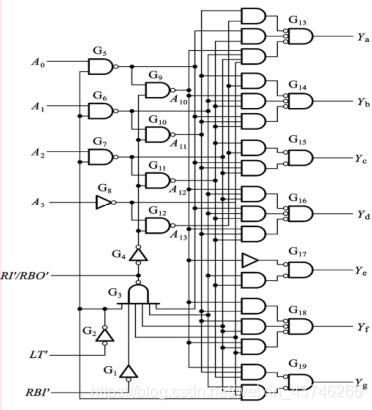

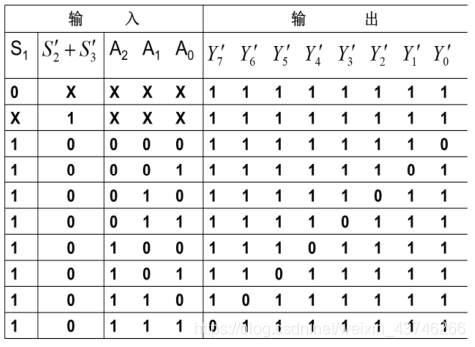

显示译码器:七段字符显示器,即用七段字符显示0~9个十进制数码,常用的七段字符显示器有半导体数码管和液晶显示器两种 5.1 半导体数码管(LED七段显示器)(1)半导体数码管每段都是一个发光二极管(LED),材料不同,LED发出光线的波长不同,其发光的颜色也不一样 (2)半导体数码管分共阴极和共阳极两类,S201A属于共阴极类型,因为从内部电路上看,其各发光二极管的阴极是接在一起的。当外加高电平时,发光二极管亮,故高电平有效。而共阳极则阳极连在一起,故低电平有效。 (3)导体数码管的优点是工作电压低,体积小、寿命长、可靠性高、响应时间短、亮度高等。缺点为工作电流大(10mA) 5.2 液晶显示器(LCD显示器)(1)液晶是一种既有液体的流动性又具有光学特性的有机化合物。它的透明度和呈现的颜色是受外加电场的影响,利用这一点做成七段字符显示器 (2)工作原理:七段液晶电极也排列成8字形,当没有外加电场时,由于液晶分子整齐地排列,呈透明状态,射入的光线大部分被返回,显示器呈白色;当有外加电场,并且选择不同的电极组合并加以电压,由于液晶分子的整齐排列被破坏,呈浑浊状态,射入的光线大部分被吸收,故呈暗灰色,可以显示出各种字符来 (3)液晶显示器的最大优点是功耗极低,工作电压也低,但亮度很差,另外它的响应速度较低。一般应用在小型仪器仪表中 【就是我们之前用的计算器,是利用入射光线,太暗看不到】 5.3 BCD-七段译码器七段数码管需要驱动电路,使其点亮。驱动电路可以是TTL电路或者CMOS电路,其作用是将BCD代码转换成数码管所需要的驱动信号,共阳极数码管需要低电平驱动;共阴极数码管需要高电平驱动 以共阴极为例子,需要高电平驱动:

利用卡诺图圈零取反 按照逻辑添加一些控制输入端得到下面的电路: 【这一部分本人有点模糊,需要再修改】 工作电路

|

【本文地址】

今日新闻 |

推荐新闻 |

附加控制端:S 1 ,S 2 和S 3 ; 输入端:A 0 ,A 1 和A 2 ; 输出端低电平有效

附加控制端:S 1 ,S 2 和S 3 ; 输入端:A 0 ,A 1 和A 2 ; 输出端低电平有效 最后电路如下图

最后电路如下图

例如当要显示4(输入0100)时,需要电量bcfg四根二极管,所以对应的输出为高电平

例如当要显示4(输入0100)时,需要电量bcfg四根二极管,所以对应的输出为高电平 得到逻辑表达式:

得到逻辑表达式: