PCIe 参考时钟架构 (Refclk Architecture) |

您所在的位置:网站首页 › pcie的时钟频率 › PCIe 参考时钟架构 (Refclk Architecture) |

PCIe 参考时钟架构 (Refclk Architecture)

|

开聊之前先梳理几个概念: Jitter,时钟抖动,是对于同一 Clock 而言的, 是时钟源引起的,用来描述被测时钟与理想时钟在时域的偏差(单位为 ps RMS,皮秒均方根)。 Skew,时钟偏斜,是对于多个时钟线而言的,是时钟树不平衡引起的。 此外还有一个概念是频率稳定性,用来描述被测时钟频率与理想时钟频率的偏差(单位 ppm,百万分之一)。参考时钟PCIe Serdes 在时钟驱动下收发串行数据流。Serdes 所用时钟由 PHY 内的 PLL 生成,PLL 的参考时钟由外部提供或从接收数据流中恢复出来。 PCIe 协议指定标准的参考时钟为 HCSL 电平的 100 MHz 时钟,Gen1~Gen4 下要求收发端参考时钟精度在 ±300 ppm 以内,Gen5 要求频率稳定性 ±100 ppm。在 FPGA 应用中,为了兼顾其他 IP,采用 LVCMOS/LVDS/LVPECL 电平 125 MHz/250 MHz 的方案也较为常见。 时钟架构PCIe 时钟架构是指 PCIe 系统中收发端设备给定参考时钟的方案。PCIe 有 3 种时钟架构(图 1),分别为:Common Clock Architecture (CC),Separate Clock Architecture 和 Data Clock Architecture。

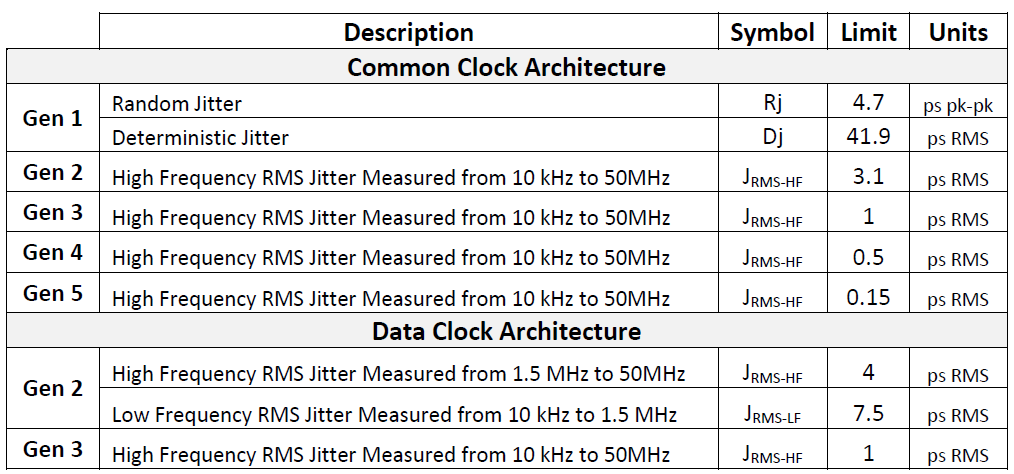

Common Clock Architecture (CC),通用参考时钟架构,收发端共享同一个参考时钟。三种 PCIe 参考时钟架构中,Common Clock 是最为常用的一种时钟架构,采用 Common Clock 支持时钟扩频(SSC, Spread Spectrum Clock) 且对参考时钟的要求不如 Separate Clock 方案严苛。Common Clock 对于频率稳定性的要求是 ±300 ppm。 对于适用同一 Common Clock 作为参考时钟的 PCIe 设备,所有设备间的时钟偏斜(Clock Skew)必须保持在 12 ns 以内,这无疑对大型电路板上或跨板的 PCIe 设备间布局布线形成巨大挑战。 Separate Clock ArchitectureSeparate Clock Architecture,收发端采用独立的参考时钟,根据有无 SSC 可进一步分为 SRNS ( Separate Refclk with No SSC) 及 SRIS (Separate Refclk with Independent SSC)。 对于收发端采用独立参考时钟的方案,其收发端独立使用不同的参考时钟源,无需单独传递时钟,对布局布线的要求更宽松。SRNS 允许 ±300 ppm (600ppm),而 SRIS 允许 ±2800 ppm (5600 ppm,其中SSC允许 5000ppm,TX/RX允许 600 ppm)。 若 PCIe 设备开启了 SRIS,其发生 SKP 的频率应该加大,同时加大弹性缓存(Elastic Buffer)的深度。弹性缓存加大使得延时更大,在一定程度上降低了 performance。对于一条 PCIe 链路,如何知道要不要采用 SRIS 呢?遗憾的是,目前尚没有机制实现收发端之间的 SRIS 协商。 Data Clock ArchitectureData Clock Architecture,仅发送端需要 Refclk,接收端无需外部 RefClk,其 CDR (Clock Data Recovery,时钟数据恢复)的 Refclk 参考时钟从数据流中恢复出来。Data Clock 时钟方案是三种方案中最易实现的方案,其无需外部参考时钟,在数据流中携带有时钟信息,接收端接收数据流并从中恢复出时钟供给其 CDR 作参考时钟。 Data Clock 时钟方案仅适用于 Gen2 及 Gen3,单 lane 单向最高速率 8GT/s。 扩频时钟(SSC)扩频时钟可以抑制电磁干扰(EMI)。为了降低 PCIe 时钟及数据线的电磁辐射、增强高速数据传输可靠性,PCIe 时钟可以采用 SSC 对参考进行时钟扩频。Gen1~Gen5 都支持 SSC,但只有 Gen3 及以上支持 SRIS。 PCIe 扩频模式为向下扩频,扩频范围为-0.5%~0%,确保最大频率在标称频率之下。最大调制幅度为 -0.5%! 调制频率为 30 KHz ~ 33 KHz,确保 PLL 能够跟得上,同时减小音频噪声的引入。调制波形采用三角波,该波形易于实现,且调制后的频谱接近均匀分布。 注意:30 KHz ~ 33 KHz 是指频率随时间周期变化的频率,不是展宽的带宽,带宽为时钟频率的 0.5% 。 更多扩频相关介绍,请查看文末参考资料。 Clock JitterCommon Clock 与 Data Clock Jitter随着 PCIe 速率的提升,其对时钟抖动 (Jitter) 的要求也越来越严苛。图 2 为 Common Clock 及 Data Clock 模式下的不同 PCIe 速率对 Jitter 的要求。

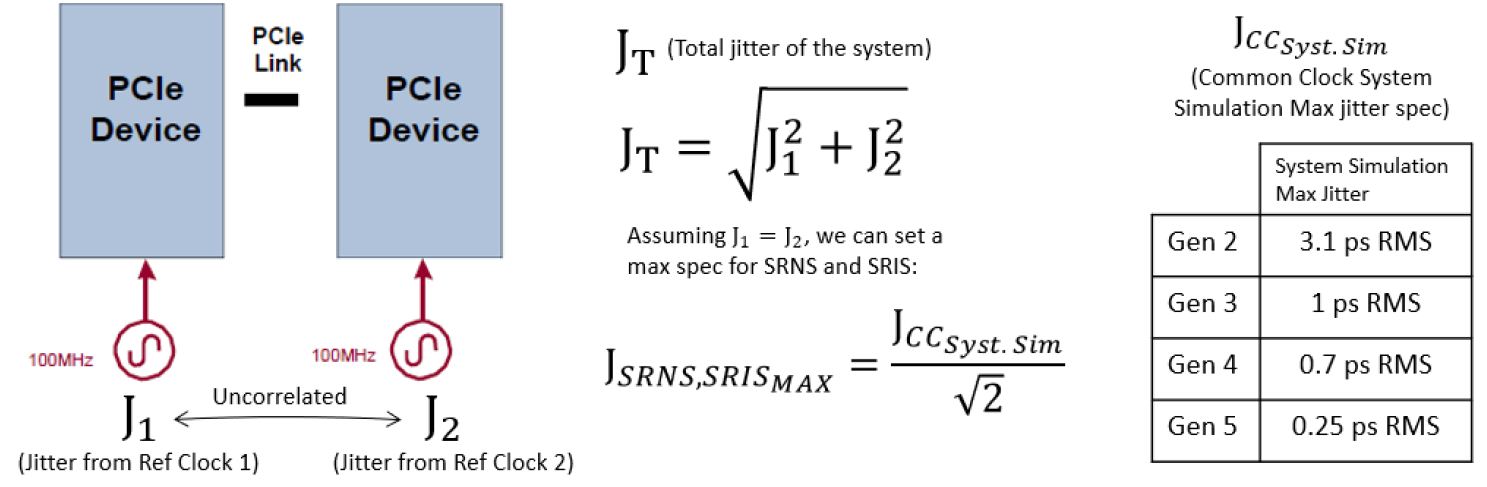

▲ 图 2 Common Clock 及 Data Clock 架构的 Jitter 需求 SRNS/SRIS Clock Jitter目前尚未出台 SRNS/SRIS 模式下 Gen4/Gen5 的 Jitter Limit,现有的 SRNS/SRIS Jitter Limit 是基于 Common Clock Jitter Limit 等效推算出来的。 假设 Separate Clock 收发端采用跟 Common Clock 相同电平、相同 Jitter 、相同频率的时钟。设 Common Clock 系统 Jitter Limit 为 J C C S y s t . S i m J_{CC_{Syst.Sim}} JCCSyst.Sim(仿真结果,非标准指定),那么采用 Separate Clock 的方案,引入了两个随机独立的 Jitter J 1 J_1 J1 和 J 2 J_2 J2(图3)。系统总的 Jitter 可以表示为两者平方和的根,即: JT=J12+J22 假设 J 1 = J 2 = J S R N S , S R I S J_1=J_2=J_{SRNS,SRIS} J1=J2=JSRNS,SRIS, Separate Clock 要达到跟 Common Clock 相同的系统 Jitter Limit J C C S y s t . S i m J_{CC_{Syst.Sim}} JCCSyst.Sim, 其收端或发端 Clock Jitter Limit 可以表示为: JSRNS,SRISMAX=JCCSyst.Sim/2

▲ 图 3 Separate Reference Architecture Jitter Distribution

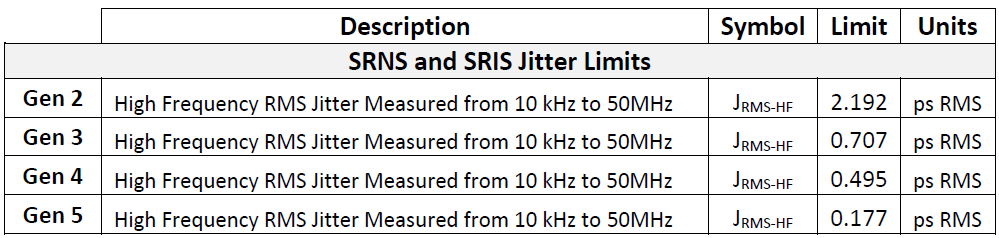

▲ 图 4 Separate Clock 架构的 Jitter 需求 图4 是基于 Common Clock 架构计算出的 SRNS/SRIS Jitter Limit。整体来看,Separate Clock 的 Jitter Limit 比 Common Clock 和 Data Clock Jitter Limit 都要小,也就是说Separate Clock 对Clock Jitter 的要求更为严苛。 注意:Common Clock 及 Data Clock 时,考虑到长距离时钟线上的耦合噪声,标准中给定的 Limit 是要比仿真结果小的,比如系统仿真 Gen5 的 Clock Jitter Limit 是0.25 ps RMS,标准中给定的是 0.15 ps RMS。但采用 Seoparate Clock 架构的 PCIe 系统,其收发端各自有一个独立的时钟源,消除了时钟线的耦合噪声,其 Jitter Limit 仍采用仿真结果。 参考 PCI Express Base 6.0,Chapter 4.3.9 & 8.6 关于PCIe参考时钟的讨论 PCIe 的时钟结构 Selecting the Optimum PCI Express Clock Source 进行精准的PCIe 4.0时钟抖动测量 PCIe Separate Reference Clock With Independent Spread (SRIS) Architecture Overview PCIe Spread Spectrum Clocking (SSC) for Verification Engineers 什么是SSC(扩频时钟) 采用扩频技术的EMI解决方案 扩频时钟SSC技术,即展频 高速协议时钟SSC扩频展频学习整理 时钟抖动计算 |

【本文地址】