FPGA学习 |

您所在的位置:网站首页 › oppofindx屏幕出现彩条 › FPGA学习 |

FPGA学习

|

FPGA学习--RGB-LCD屏彩条显示实验

RGB-LCD屏原理程序设计

参考正点原子视频

RGB-LCD屏原理

LCD 是一种液晶显示屏,它采用薄膜晶体管(TFT)技术提升图像质量,如提高图像亮度和对比度等。相比于传统的 CRT 显示器,LCD 有着轻薄、功耗低、无辐射、图像质量好等诸多优点,因此广泛应用于电视机、电脑显示器、手机等各种显示设备中。 其显示的每个像素点都由集成在液晶后面的薄膜晶体管独立驱动。 分辨率 如720K、1080K、2K或4K。一个像素点代表一个灯,每个灯的颜色由RGB三个颜色构成。1080P的意思就是一个LCD屏幕上的像素数量是1920*1080个。

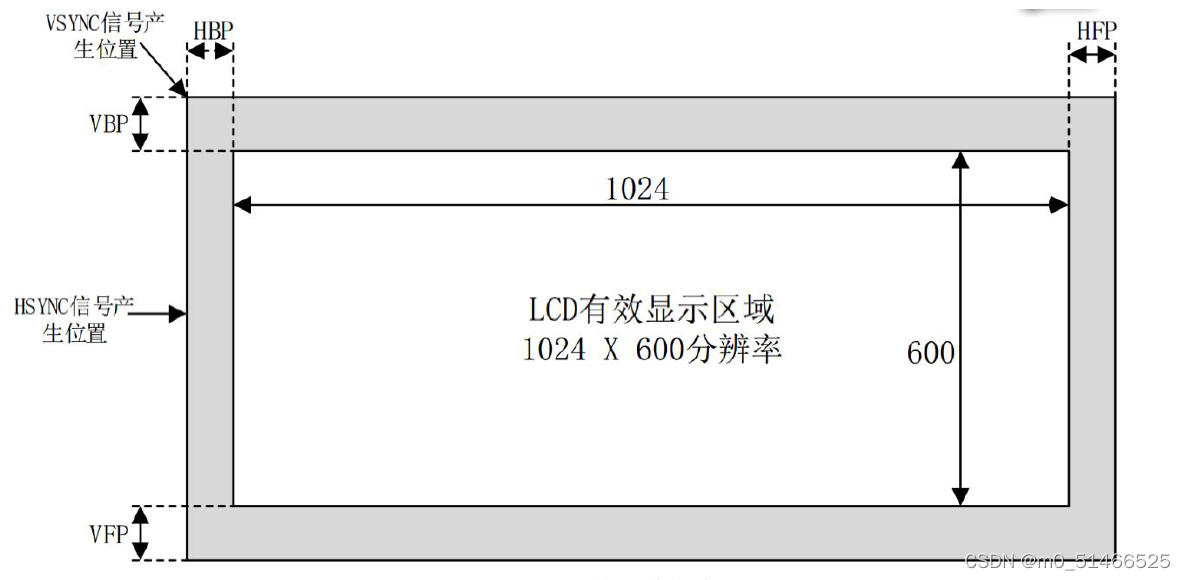

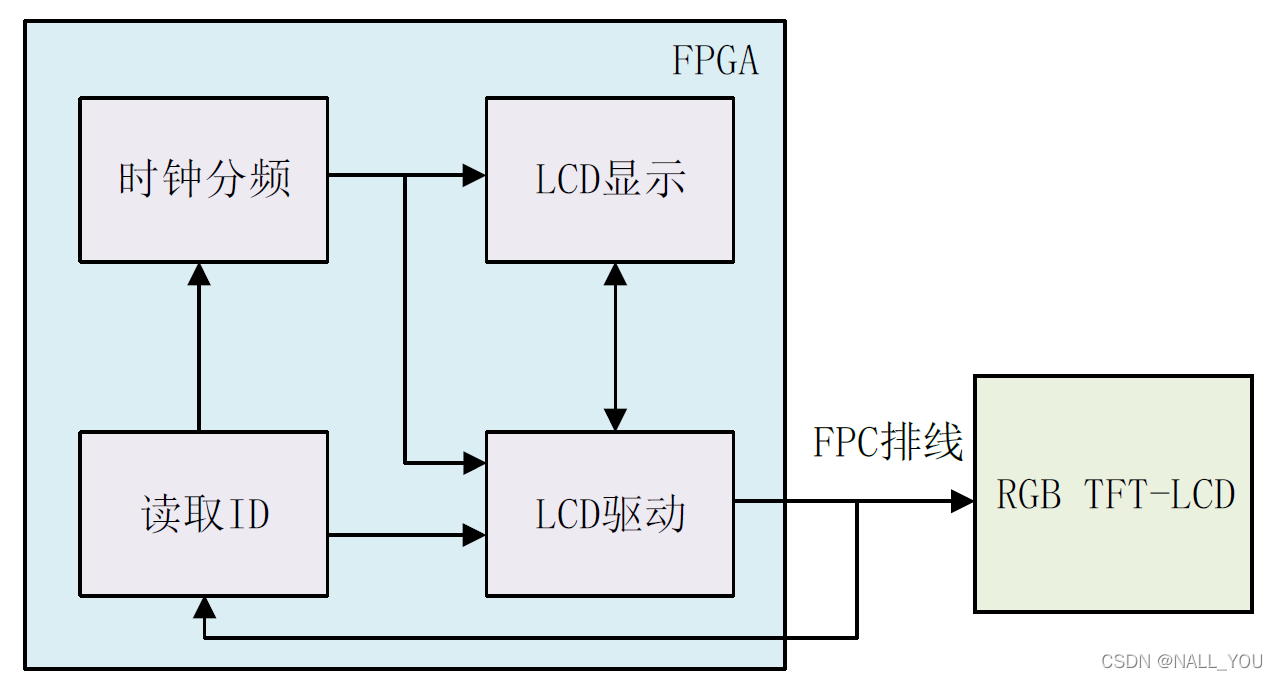

一共有 1920 * 1080=2073600 个像素点(每一行1920个,共有1080行)。2K 就是 2560*1440 个像素点,4K 是 3840 * 2160 个像素点。很明显,在 LCD 尺寸不变的情况下,分辨率越高越清晰。同样的,分辨率不变的情况下,LCD 尺寸越小越清晰。由此可见,LCD 显示器的分辨率是一个很重要的参数,但是并不是分辨率越高的 LCD 就越好。衡量一款 LCD 的好坏,分辨率只是其中的一个参数,还有色彩还原程度、色彩偏离、亮度、可视角度、屏幕刷新率等其他参数。 像素格式 控制RGB三种颜色的亮度就可以显示各种色彩。那么如何控制呢?一般一个R,G,B这三部分分别使用8bit的数据,那么一个像素点就是24bit。也就是一个像素点需要 3个字节,这种像素格式称为RGB888。常见的像素格式也有RGB565,只需要两个字节,就是色彩对比度上差一点。 红色对应的值就是 24’hFF0000, 24’h00FF00对应蓝色,绿色对应的值为 24’h0000FF。通过调节 R、G、B 的比例可以产生其它的颜色,比如 24’hFFFF00 就是黄色,黑色就是24’h000000,24’hFFFFFF 就是白色。大家可以打开电脑的“画图”工具,在里面使用调色板即可获取到想要的颜色对应的数值。 LCD屏幕接口 显示器的接口有VGA、HDMI、DP等接口,这次我们用的是RGB-LCD接口。 其中,如下图,。默认情况,R1 和 R6 焊接,设置 LCD_LR 和 LCD_UD,控制 LCD 的扫描方向,是从左到右,从上到下(横屏看)。而 LCD_R7/G7/B7 则用来设置 LCD的 ID。由于 RGBLCD 没有读写寄存器,也就没有所谓的 ID,这里我们通过在模块上面,控制 R7/G7/B7 的 上/下拉,来自定义 LCD 模块的 ID,帮助 MCU 判断当前 LCD 面板的分辨率和相关参数,以提高程序兼容性。 4384的话,设置为100即可。 LCD时间参数 如何显示一帧图像呢?就像用一支笔从左到右,从上到下地进行绘画。HSYNC是行同步信号(水平同步信号),产生此信号代表开始显示新的一行了。VSYNC是帧同步信号(垂直同步信号),产生此信号代表开始新的一帧图像了。 但是可以看到旁边有一圈黑边,这是什么呢?其实是延时信号,IC执行指令需要反应时间(需要时间来识别一行数据扫描完了或一帧数据来继续下一步操作),所以当HSYNC结束之后会产生一段延时,产生之前也会产生。(HBP和HFP)VSYNC也是同理,产生的延时是VFP和VBP。–锁定有效的像素数据。 RGB-LCD屏幕时序 行显示的时序图是以CLK为单位的,而帧显示的时序图是以行为单位的。具体时序如下两图所示。需要注意的是,有两种数据同步方式。一种是行场同步模式,另一种是DE同步模式。 在行场同步模式中,行同步信号和场同步信号作为数据传输的同步信号,此时DE必须为低电平。DE同步模式,DE作为数据的有效信号,只有同时扫描到帧有效显示区域和行有效显示区域,DE信号才有效(为高电平)。当选择此模式时,VS和HS都必须为高电平。 一般都采用DE模式,行场同步和VGA接口的协议有点类似。 像素时钟 像素时钟是时钟信号。 N CLK))= (VSPW+VBP+LINE+VFP) * (HSPW + HBP + HOZVAL + HFP)= (2 + 128 + 480 + 10) * (33 + 88 + 800 + 40) = 620 * 961 = 578522 –以ATK4384为例。(800480,LIINE等于480,HOZVAL等于800) 显示一帧时钟需要578522个时钟数,显示60帧是:57852260=34711320约等于34.7M,所以像素时钟就是34.7MHZ。 当然严格上也不用按照60帧来计算,我们可以给个33.3HZ,其刷新率也在60帧左右。 以下是不同分辨率的时序参数。 分为5个模块。顶层模块、读取ID模块、时钟分频模块、LCD显示模块、LCD驱动模块。其中输入信号包括3个要素:像素时钟、同步信号和图像数据。 系统框图如下图: 此处把rgb的引脚定为双向的状态,如果de为低电平,引脚状态由外围电路决定(也就是赋高阻态);当de为高电平,此时写入的数据将会有效地赋给输入了,下面也用到了一个简单的译码器。 rd_id.v //reg define reg rd_flag; //读ID标志 //获取LCD ID M2:B7 M1:G7 M0:R7 always @(posedge clk or negedge rst_n)begin if(!rst_n)begin rd_flag |

【本文地址】

今日新闻 |

推荐新闻 |

rgb_top.v

rgb_top.v