半导体器件和工艺模拟:使用Silvaco设计构建NMOS并提取各项工艺及器件参数 |

您所在的位置:网站首页 › nmos管参数 › 半导体器件和工艺模拟:使用Silvaco设计构建NMOS并提取各项工艺及器件参数 |

半导体器件和工艺模拟:使用Silvaco设计构建NMOS并提取各项工艺及器件参数

|

半导体器件和工艺模拟

使用Silvaco设计构建NMOS并提取各项工艺及器件参数

一、目的: 1、熟练氧化、离子注入与扩散工艺,使用Silvaco软件进行模拟 2、掌握nmos工艺流程。 3、学会用Silvaco软件提取MOS晶体管的各种参数 4、掌握MOS晶体管器件模拟 二.要求 1.用Anthena构建一个NMOS管,要求沟道长度不小于0.8微米,阈值电压在-0.5v 至 1V之间,要说明在工艺中如何调整阈值电压并在模拟结果中有所体现。 2.工艺模拟过程要求提取S/D结结深、阈值电压、沟道表面掺杂浓度、S/D区薄层电阻等参数。 3.进行器件模拟,要求得到NMOS输出特性曲线族以及特定漏极电压下的转移特性曲线,并从中提取MOS管的阈值电压和β值。 4.分析各关键工艺步骤对器件性能的影响。 三.步骤: 1、启动silvaco软件。 2、创建一个网格并定义衬底的参数。 3、由于本实验运用了cmos工艺,所以先在衬底上做一个p阱,严格定义p阱的浓度,注入能量,以及阱区的推进。 4、生长栅氧化层,严格控制各参数。 diffus time=10 temp=950 dryo2 press=1.00 hcl.pc=3 5、淀积多晶硅,其厚度为0.2um。 6、刻蚀掉x=0.35左面的多晶硅,然后低剂量注入磷离子,形成轻掺杂层,剂量为3e13,能量为20kev。 7、淀积氧化层,然后再进行刻蚀,以进行下一步的源漏区注入。 8、进行源漏砷离子的注入,剂量为4e15,能量为40kev。 9、淀积铝,形成S/D金属接触。 10、进行向右镜像操作,形成完整的nmos结构并定义电极。 11、抽取源漏结深,阈值电压,n+区薄层电阻,沟道表面掺杂浓度,轻掺杂源漏区的薄层电阻等参数。 12、描述输出特性曲线并绘出。 13、描述转移特性曲线并绘出,同时从中提取MOS管的阈值电压和β值。 四、结果及分析 1、工艺图

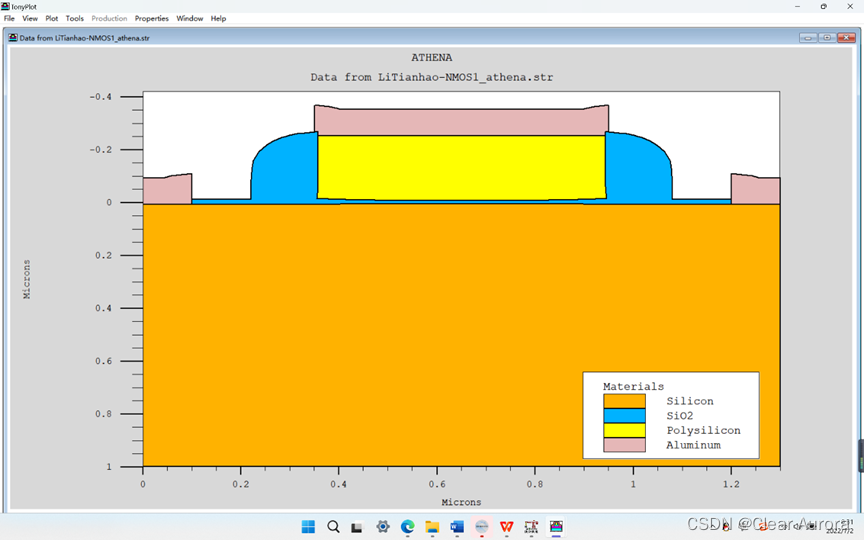

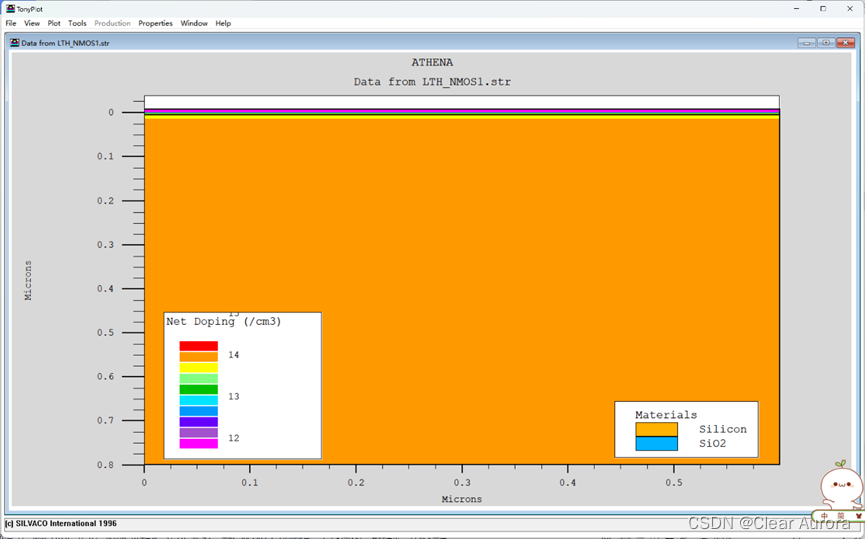

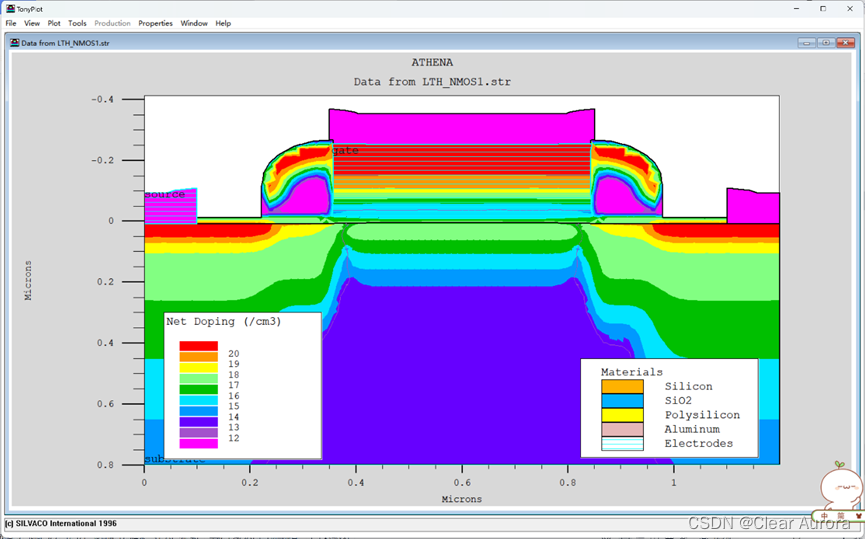

由图可见,此NMOS沟道长度不小于0.8微米,符合要求。 2、工艺过程: (1)定义矩形网格: #定义X网格 line x loc=0 spac=0.1 line x loc=0.2 spac=0.006 line x loc=0.6 spac=0.006 #定义Y网格 line y loc=0.00 spac=0.002 line y loc=0.2 spac=0.005 line y loc=0.5 spac=0.05 line y loc=0.8 spac=0.15 (2)定义初始硅并氧化:100 晶向,作为P 型衬底,用硼掺杂,掺杂浓度为1e14,之后制作栅氧化层:把硅片放在950摄氏度,干氧,一个大气压下掺氯(氯化氢)氧化10分钟,结果如下:

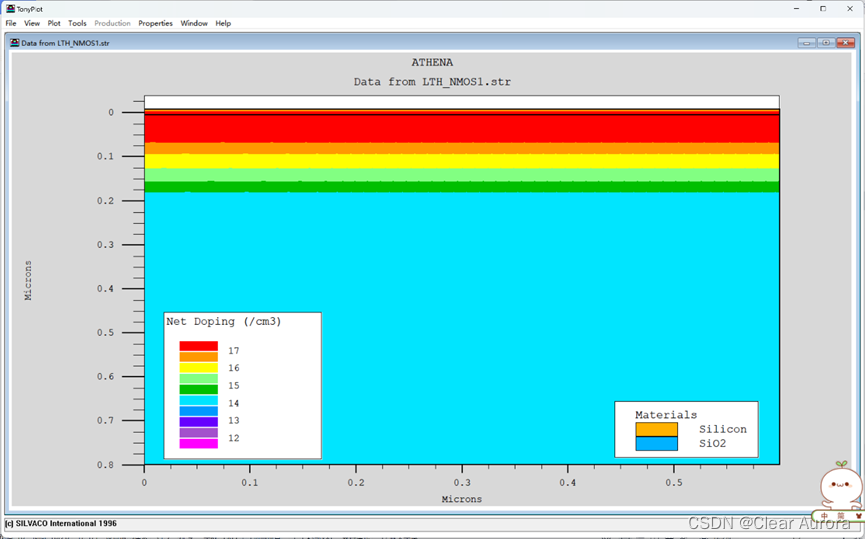

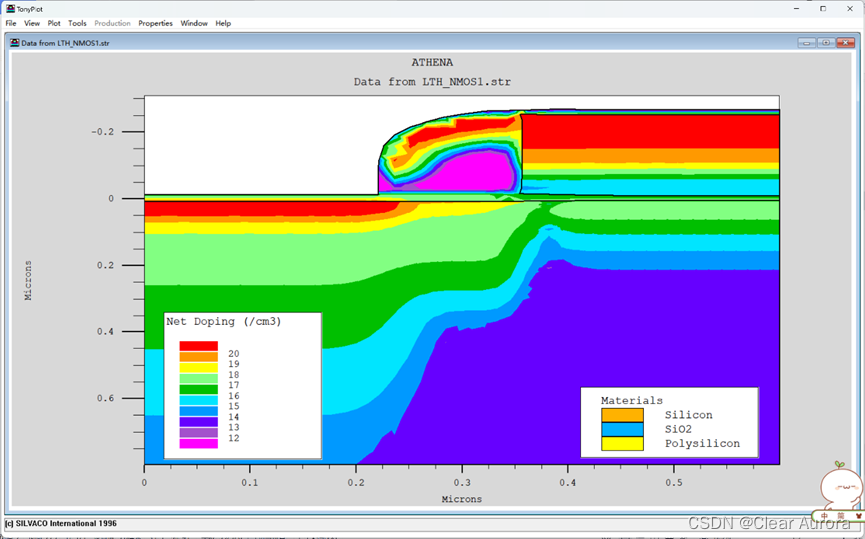

(3)调整阈值电压,离子注入,注入硼离子,剂量为2e12,能量为10KeV:

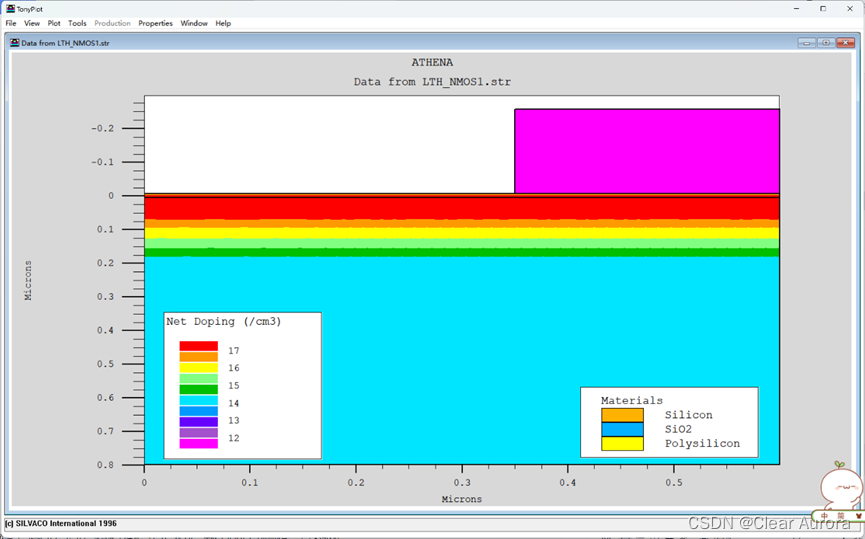

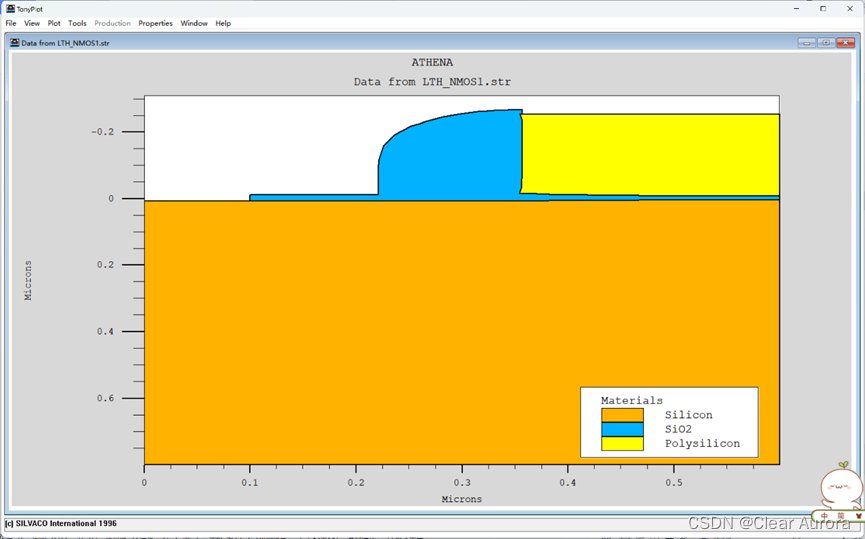

(4)淀积Poly层后进行栅刻蚀:刻蚀掉x=0.35左面的多晶硅,结果如下:

(5)湿氧氧化后进行轻掺杂,轻掺杂使用离子注入,注入磷离子,剂量为3e13,能量为20KeV,之后沉积氧化层再进行干刻蚀,以进行下一步的源漏区注入 ,其结果如下:

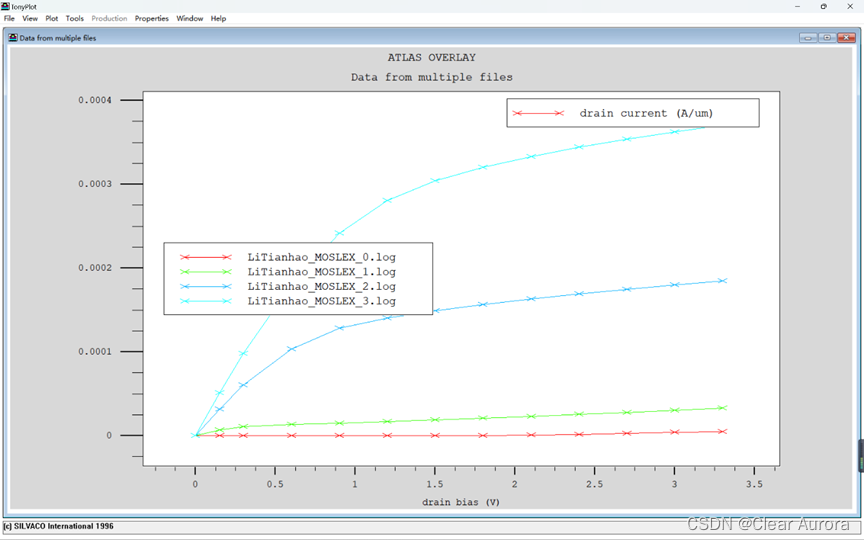

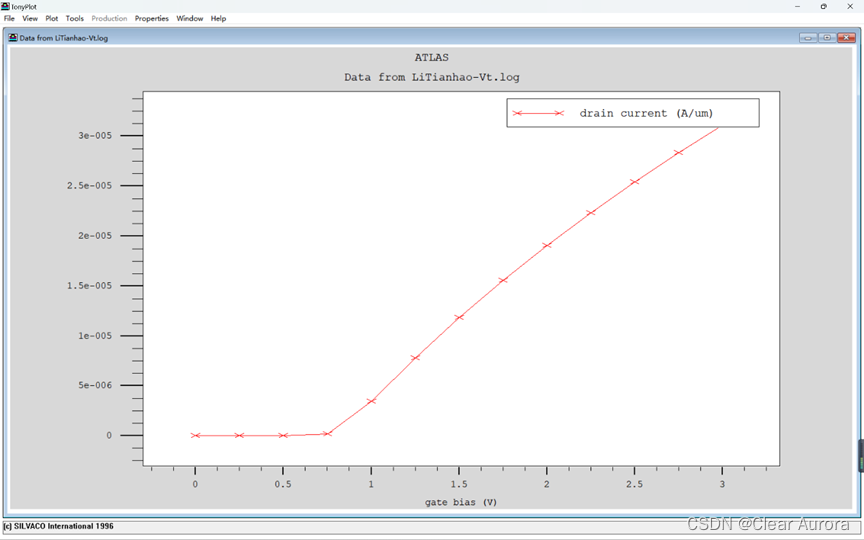

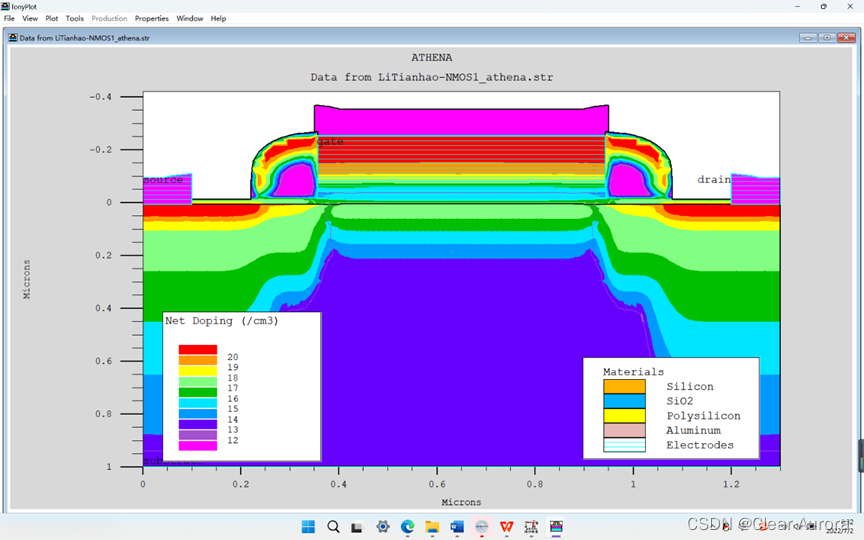

3、器件仿真结果及参数特性分析: (1)结深: 结深测量语句:extract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1 测量结果: EXTRACT> extract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1 nxj=0.882642 um from top of first Silicon layer X.val=0.1 (2)测量沟道阈值电压 沟道阈值电压测量语句: extract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49 测量结果: EXTRACT> extract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49 n1dvt=0.953742 V X.val=0.49 (3)沟道表面掺杂浓度 沟道表面掺杂浓度测量语句: extract name="chan surf conc" surf.conc impurity="Net Doping" \ material="Silicon" mat.occno=1 x.val=0.45 测量结果: EXTRACT> extract name="chan surf conc" surf.conc impurity="Net Doping" chan surf conc=8.22657e+020 atoms/cm3 (4)获取S/D区薄层电阻 获取语句: extract name="n++ sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.05 region.occno=1 获取结果: EXTRACT> #extract the N++ regions sheet resistance EXTRACT> extract name="n++ sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.05 region.occno=1 n++ sheet rho=40.5223 ohm/square X.val=0.05 (5)NMOS输出特性曲线 上图为该器件仿真 Id-VDS曲线(输出特性曲线)的结果,由图可知:

1、由理论知识得,当栅极电压小于NMOS阈值电压时,没有导电沟道形成,无论VDS取值如何,均不会有漏极电流:图中红色输出曲线是栅压为0.5V时(NMOS截止)的输出曲线。 2、当栅极电压大于NMOS阈值电压时,在栅极下方的衬底会出现反型层,从而形成导电沟道,此时在漏源区加上电压VDS,就会产生漏极电流。 3、当VDS较小时,漏极电流随VDS呈线性增长,此时 MOSFET 工作在线性区。 4、继续增大VDS,一定程度后导电沟道会被夹断,此后Id不再随VDS的增大而变化,Id只与栅极电压VGS有关,此时MOSFET 工作在饱和区。(上方除红色曲线外三条输出曲线分别是栅极电压为1.1V、2.2V、3.3V 时的输出特性曲线,说明 NMOS 的输出特性曲线随栅极电压的不同而变化。) 由仿真结果可知,NMOS输出特性与理论分析相符。 (6)NMOS转移特性曲线: 上图为漏极电压VDS恒定时的 Id-VGS 曲线(转移特性曲线),由曲线可以看出: 1、当VDS一定时,栅压很小的时候不存在导电沟道,NMOS截止。 2、随着栅极电压VGS的增大,P型衬底将出现反型层,当VGS大于NMOS阈值电压时,导电沟道出现且宽度变宽,载流子浓度随VGS的增大而增加,VDS呈线性增长。 由仿真结果可以看出, NMOS转移特性与理论分析相符。 (7)提取MOS管的阈值电压 EXTRACT>extract name="nvt"(xintercept(maxslope(curve(abs(v."gate"), abs(i."drain"))))- abs(ave(v."drain"))/2.0) nvt=0.751552 可见此NMOS阈值电压在-0.5v 至 1V之间,符合要求。 (8)提取参数 1、nxj=0.882642 um 2、n1dvt=0.953742 V 3、chan surf conc=8.22657e+020 atoms/cm3 4、n++ sheet rho=40.5223 ohm/square 5、nvt=0.751552 6、nbeta=0.000173251 附录实验程序代码块如下: go athena #定义X网格 line x loc=0 spac=0.1 line x loc=0.2 spac=0.006 line x loc=0.65 spac=0.006 #定义Y网格 line y loc=0.00 spac=0.002 line y loc=0.2 spac=0.005 line y loc=0.5 spac=0.05 line y loc=1.0 spac=0.15 #定义初始硅:100 晶向,作为P 型衬底,用硼掺杂,掺杂浓度为1e14 init silicon c.boron=1e14 orientation=100 space.mul=2 two.d #制作栅氧化层:把硅片放在950摄氏度,干氧,一个大气压下掺氯(氯化氢)氧化10分钟 diffus time=10 temp=950 dryo2 press=1.00 hcl.pc=3 #抽取栅氧化层厚度 extract name="gateox" thickness oxide mat.occno=1 x.val=0.3 #调整阈值电压,离子注入,注入硼离子 implant boron dose=2e12 energy=10 pearson #淀积Poly层 depo poly thick=0.25 divi=10 #栅刻蚀:刻蚀掉x=0.35左面的多晶硅 etch poly left p1.x=0.35 #湿氧氧化为轻掺杂做准备 diffuse time=3 temp=900 weto2 #轻掺杂离子注入,注入磷离子,形成轻掺杂层,剂量为3e13,能量为20kev implant phosphor dose=3e13 energy=20 tilt=0 rotation=0 #沉积氧化层再进行干刻蚀,以进行下一步的源漏区注入 depo oxide thick=0.120 divisions=8 etch oxide dry thick=0.120 #进行源漏砷离子的注入,剂量为4e15,能量为40kev implant arsenic dose=4.0e15 energy=40 tilt=0 rotation=0 #快速退火 method fermi diffus time=1 temp=900 nitro press=1.00 #下面处理漏源极 #刻蚀掉x=0.1以左的氧化层 etch oxide left p1.x=0.1 #刻蚀掉一个矩形,把栅极多晶硅上面的氧化层刻蚀掉,我写的下面四句蚀刻掉了(0.357,-0.15)->(0.6,-0.15)->(0.6,-0.3)->(0.357,-0.3)区域内的氧化层 etch oxide start x=0.357 y=-0.15 etch cont x=0.65 y=-0.15 etch cont x=0.65 y=-0.3 etch done x=0.357 y=-0.3 #沉积铝 deposit alumin thick=0.1 div=20 #刻蚀掉一个矩形区域的铝,我写的下面四句蚀刻掉了(0.35,0.1)->(0.1,0.1)->(0.1,-0.4)->(0.35,0.4)区域内的铝 etch alumin start x=0.35 y=0.1 etch cont x=0.1 y=0.1 etch cont x=0.1 y=-0.4 etch done x=0.35 y=-0.4 #接下来进行结果分析的提取,查看器件特性 #Extract design parameters #extract final S/D Xj extract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1 #extract the N++ regions sheet resistance extract name="n++ sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.05 region.occno=1 #extract the sheet rho under the spacer,of the LDD region extract name="ldd sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.3 region.occno=1 #extract the surface conc under the channel. extract name="chan surf conc" surf.conc impurity="Net Doping" material="Silicon" mat.occno=1 x.val=0.45 #extract a curve of conductance versus bias. extract start material="Polysilicon" mat.occno=1 bias=0.0 bias.step=0.2 bias.stop=2 x.val=0.45 extract done name="sheet cond v bias" curve(bias,1dn.conduct material="Silicon" mat.occno=1 region.occno=1) outfile="extract.dat" #extract the long chan Vt extract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49 #接下来进行镜像和电极定义 #镜像对称 structure mirror right #保存镜像结构,完整的nMOS structure outfile=mirror.str electrode name=gate x=0.5 y=-0.2 electrode name=source x=0.05 y=0 electrode name=drain x=1.30 y=0 electrode name=substrate backside #工艺仿真器件制作完成,保存到我的LiTianhao-NMOS1_athena.str文件中 structure outfile=LiTianhao-NMOS1_athena.str tonyplot LiTianhao-NMOS1_athena.str #接下来进行器件物理特性分析,先求栅压为1.1V,2.2V,3.3V时,漏电流与漏电压的关系,即进行CVT分析 go atlas # 定义栅极功能,N型接触 contact name=gate n.poly # 定义栅氧化层正电荷为3e10 interface qf=3e10 # 使用CVT模型分析 MOS models cvt srh print numcarr=2 # 设置栅极偏置,同时设置Vds=0V solve init solve vgate=0.5 outf=solve_tmp0_LiTianhao solve vgate=1.1 outf=solve_tmp1_LiTianhao solve vgate=2.2 outf=solve_tmp2_LiTianhao solve vgate=3.3 outf=solve_tmp3_LiTianhao #加载文件和步进Vd load infile=solve_tmp0_LiTianhao log outf=LiTianhao_MOSLEX_0.log solve name=drain vdrain=0 vfinal=3.3 vstep=0.3 load infile=solve_tmp1_LiTianhao log outf=LiTianhao_MOSLEX_1.log solve name=drain vdrain=0 vfinal=3.3 vstep=0.3 load infile=solve_tmp2_LiTianhao log outf=LiTianhao_MOSLEX_2.log solve name=drain vdrain=0 vfinal=3.3 vstep=0.3 load infile=solve_tmp3_LiTianhao log outf=LiTianhao_MOSLEX_3.log solve name=drain vdrain=0 vfinal=3.3 vstep=0.3 # 提取最大漏极电流和β值(斜率) extract name="nidsmax" max(i."drain") extract name="sat_slope" slope(minslope(curve(v."drain",i."drain"))) tonyplot -overlay -st LiTianhao_MOSLEX_0.log LiTianhao_MOSLEX_1.log LiTianhao_MOSLEX_2.log LiTianhao_MOSLEX_3.log #接下来进行Vt 测试:返回 Vt、Beta 和 θ go atlas #建立材料模型 models cvt srh print contact name=gate n.poly interface qf=3e10 method gummel newton solve init # 漏极给偏置电压 solve vdrain=0.1 # 栅压步进 log outf=LiTianhao-Vt.log master solve vgate=0 vstep=0.25 vfinal=3.0 name=gate save outf=LiTianhao-Vt.str tonyplot LiTianhao-Vt.log #提取器件参数 extract name="nvt"(xintercept(maxslope(curve(abs(v."gate"),abs(i."drain"))))- abs(ave(v."drain"))/2.0) extract name="nbeta" slope(maxslope(curve(abs(v."gate"),abs(i."drain"))))* (1.0/abs(ave(v."drain"))) extract name="nsubvt" 1.0/slope(maxslope(curve(abs(v."gate"),log10(abs(i."drain"))))) quit |

【本文地址】

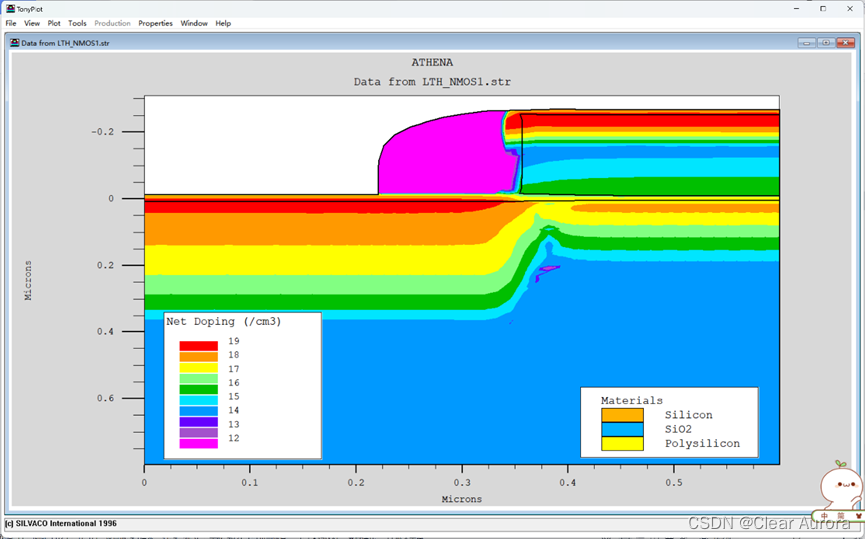

(6)进行源漏砷离子的注入,重掺杂,剂量为4e15,能量为40KeV,掺杂完成后进行快速退火,结果如下:

(6)进行源漏砷离子的注入,重掺杂,剂量为4e15,能量为40KeV,掺杂完成后进行快速退火,结果如下: (7)下面处理漏源极,先刻蚀掉x=0.1以左的氧化层 ,再刻蚀掉一个矩形,把栅极多晶硅上面的氧化层刻蚀掉,以便于之后与金属接触制作电极。我蚀刻掉了(0.357,-0.15)->(0.6,-0.15)->(0.6,-0.3)->(0.357,-0.3)区域内的氧化层,结果如下:

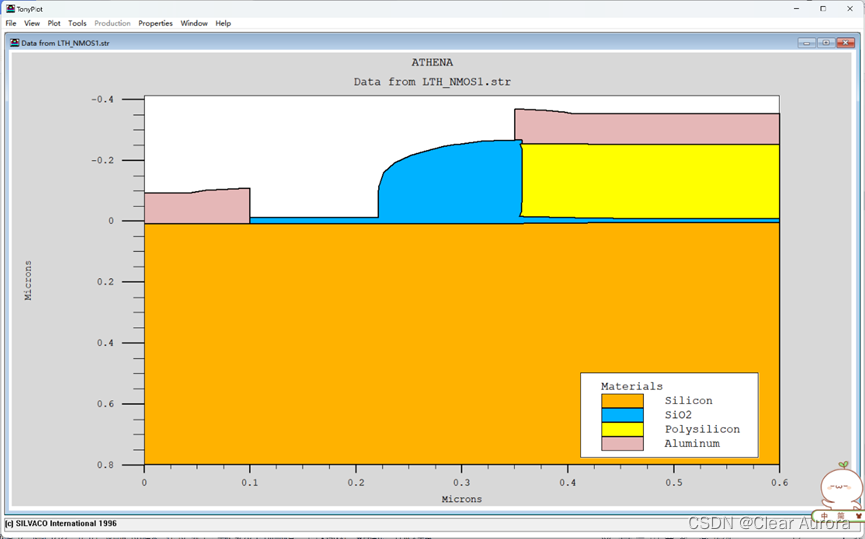

(7)下面处理漏源极,先刻蚀掉x=0.1以左的氧化层 ,再刻蚀掉一个矩形,把栅极多晶硅上面的氧化层刻蚀掉,以便于之后与金属接触制作电极。我蚀刻掉了(0.357,-0.15)->(0.6,-0.15)->(0.6,-0.3)->(0.357,-0.3)区域内的氧化层,结果如下: (8)在表面淀积铝之后,刻蚀掉一个矩形区域的铝,留下金属电极。我蚀刻掉了(0.35,0.1)->(0.1,0.1)->(0.1,-0.4)->(0.35,0.4)区域内的铝,结果如下:

(8)在表面淀积铝之后,刻蚀掉一个矩形区域的铝,留下金属电极。我蚀刻掉了(0.35,0.1)->(0.1,0.1)->(0.1,-0.4)->(0.35,0.4)区域内的铝,结果如下: (9)进行镜像和电极定义,镜像对称并保存镜像结构后,完整的NMOS如下:

(9)进行镜像和电极定义,镜像对称并保存镜像结构后,完整的NMOS如下: 至此,完整的NMOS设计工艺过程结束。

至此,完整的NMOS设计工艺过程结束。