FMC/FSMC/EXMC总线NORFlash/PSRAM接口(异步 |

您所在的位置:网站首页 › nbl是什么缩写 › FMC/FSMC/EXMC总线NORFlash/PSRAM接口(异步 |

FMC/FSMC/EXMC总线NORFlash/PSRAM接口(异步

|

请勿转载

目录 1 简介 1.1 框图 1.2 接口定义 1.3 读写时序图、时序配置参数 1.4 PSRAM控制器异步工作模式分类 1.5 PSRAM寄存器配置 1.5.1 控制寄存器BCR 1.5.2 片选时序寄存器BTR 1.5.3 写入时序寄存器BWTR 2 异步复用FPGA接口设计 2.1 实际配置的时序 2.2 接口信号处理 3 同步复用突发模式 3.1 手册中时序及reg配置 3.2寄存器设置、测试代码 3.3 FPGA实际抓取的时序图 4 参考文献 1 简介 使用STM32F4xx系列的 FMC 总线实现与 FPGA 的通信,FMC 是 Flexible Memory Controller 的缩写,译为可变存储控制器。它可以用于驱动包括 SRAM、SDRAM、NOR、FLASH 以及 NAND FLSAH 类型的存储器。 FMC 包含五个主要模块: AHB 接口(包括 FMC 配 置 寄 存 器 )、 NOR Flash/PSRAM/SRAM 控制器、NAND Flash/PC 卡控制器、SDRAM 控制器和外部器件接口。 所有的外部存储器共享数据器输出的地址、数据、控制总线,每个外部设备可以通过唯一一 个片选信号加于区分。 1.1 框图FMC 的框图、地址分配如下图所示。

本设计用到的接口说明。

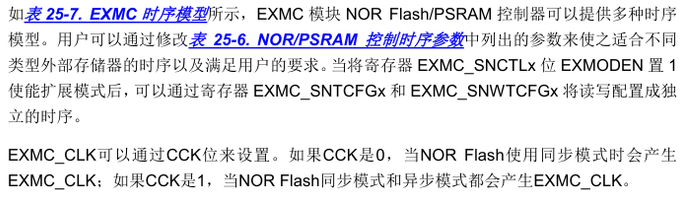

若外部连接真是存储器,则参数的配置需要与具体的存储器对应,满足其要求。参数在配置寄存器中设置。 ADDSET=地址建立时间;ADDHOLD=地址保持时间; DATAST=数据建立时间;CLK由HCLK分频得出。

详见参考文献1的《RM0090 / STM32F40xxx、STM32F41xxx、STM32F42xxx、STM32F43xxx基于 ARM 内核的 32 位高级 MCU 》第32章。本设计采用的是复用模式。 主要分为扩展模式(ABCD),非扩展模式(1,2),复用模式。其中扩展模式要用到第3个配置寄存器。

PSRAM内部分为4块,每一块都有一组3个配置寄存器。 ABCD的扩展模式要用到第3个寄存器BWTR1..4单独配置写时序参数,其他模式读写都共用第2个寄存器BTR1..4中的参数。 1.5.1 控制寄存器BCR

位 19 CBURSTRW:写入突发使能 (Write burst enable)。 位 15 ASYNCWAIT:异步传输期间的等待信号 (Wait signal during asynchronous transfers) 位 14 EXTMOD:扩展模式使能 (Extended mode enable)。 位 13 WAITEN:等待使能位 (Wait enable bit)。 位 12 WREN:写入使能位 (Write enable bit)。 位 11 WAITCFG:等待时序配置 (Wait timing configuration)。

注:此处没有提及的位,详见参考文献1《RM0090》. 注意:代码移植到GD32F450芯片时,[3:2]存储器类型必须是NOR flash,[12]打开flash写入使能。否则FMC总线时序不正常,没有地址使能。

在MemoryType=PSRAM 或NOR Flash时,异步复用模式都可调整总线周转间隔时间BusTurnAroundDuration(两个操作间隔),值越小连续操作越快。 下图中对比两种MTYP、BUSTURN=8 or 15。按手册说明应采用NOR FLASH模式。

下图中为PSRAM,调整BUSTURN=2 OR 4。采样CLK为200M,FMC的HCLK=180M。

本设计未用到,详见参考文献1《RM0090》。 2 异步复用FPGA接口设计 2.1 实际配置的时序

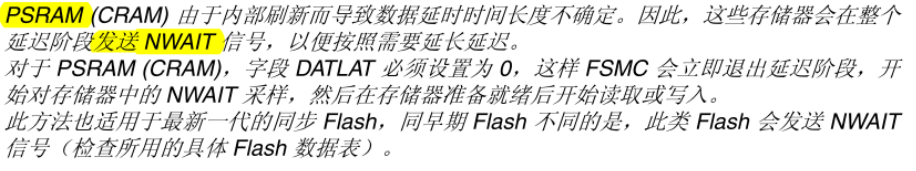

fpga_cs_ne1 片选,低有效 fpga_wr_nwe 写使能,低有效 fpga_nl_nadv 地址使能,低有效 fpga_rd_noe 读使能,低有效 fpga_db[15:0] 地址数据复用 地址使能有效: fmc_addr_en = ((!fpga_cs_ne1) & fpga_nl_nadv); 写使能有效: wire fmc_wr_en; //写使能 assign fmc_wr_en = ((!fpga_cs_ne1) & (!fpga_wr_nwe) & fpga_nl_nadv); wire [15:0] Din;//写入的数据,进入各个模块 assign Din = fpga_db; 读使能有效: wire fmc_rd_en; //读使能 assign fmc_rd_en = ((!fpga_cs_ne1) & (!fpga_rd_noe) & fpga_nl_nadv); reg [15:0] rd_data_reg; //读 数据到总线 assign fpga_db = fmc_rd_en ? rd_data_reg : 16'hzzzz;//当读使能=1时,输出数据;为低时,fpga_db为高阻抗,输入数据; (rd_data_reg 为内部读数据缓存寄存器,用读使能选择是否输出到三态总线) 3 同步复用突发模式 读写可以单独配置同步模式,非同步模式时仍采用时序寄存器的参数。读写在突发模式时,突发长度固定,读是4个半字,写是2个半字(一个半字16bits)。突发的地址应为偶数,若为奇数地址则突发写操作会被拆分为两次操作。软件中要把FMC_CLK的IO脚复用为FMC模式。printf函数不能直接打印64bits数据。 3.1 手册中时序及reg配置

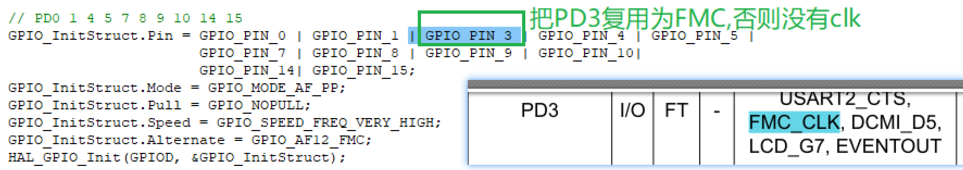

如下图PD3复用为FMC_CLK时钟,否则没有CLK输出。

同步复用突发模式的reg设置:

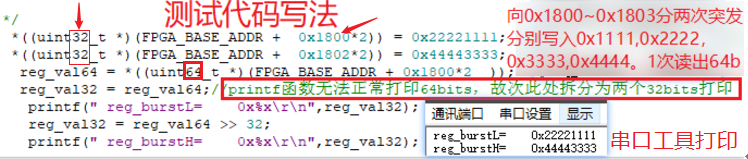

测试代码编写注意事项:

下图中采样时钟为180M,在FPGA中用FMC_CLK的90M同步处理:

下图仅用于观察突发起始地址为奇数地址时的总线时序(写突发拆分为2次操作): 4 参考文献 1.《RM0090 / STM32F40xxx、STM32F41xxx、STM32F42xxx、STM32F43xxx基于 ARM 内核的 32 位高级 MCU 》 2.《WinnerI 双 4 代核开发板 综合实例/ 第 11 章 微控制器与 FPGA 的 FMC 通信》

|

【本文地址】