基于FPGA的AXI协议讲解(1) |

您所在的位置:网站首页 › m寄存器的用法 › 基于FPGA的AXI协议讲解(1) |

基于FPGA的AXI协议讲解(1)

|

基于FPGA的AXI_Lite协议讲解

参考文献

项目简述

AXI协议简述

AXI协议接口简述

AXI4协议时序

VIVADO中AXI_Lite的搭建与使用

PS端操作

测试结果

总结

参考文献

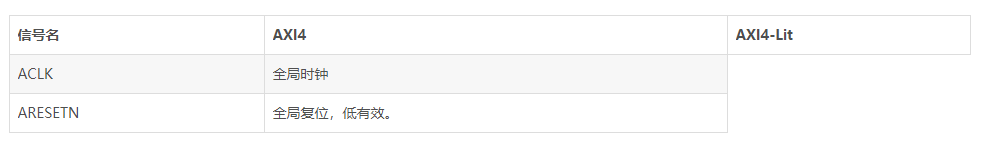

[1]、长弓的坚持 [2]、V3学院 项目简述这篇文章我们主要讲解AXI_Lite协议,主要内容包括AXI_Lite协议在FPGA中主要起到的作用,遵循的时序要求是什么,在FPGA中咋么编写Verilog代码。 本次实验将主要讲解AXI_Lite从机的协议,PS端通过AXI_Lite协议写寄存器控制PL端的LED、通过读寄存器读取PL端KEY的按键值。 这里为什么讲解AXI_Lite从机协议,因为PS端我们一般作为主机,那么需要我们实现的PL端的Verilog代码自然是从机 本次实验所用到的软硬件环境如下: 1、米联客MZ7015FA开发板 2、VIVADO 2019.1 AXI协议简述相信同学们都听说过AXI协议,现在Xilinx中提出了Block Design的设计思想,而这个设计思想的基础就是AXI协议。AXI协议起源于AMBA协议协议,2010发布的AMBA4.0包含了AXI的第二个版本AXI4。现在常见的AXI协议是AXI4版本的协议。AXI4总线协议规定的数据传输方式是猝发式的。它的地址/控制和数据相位是分离的,支持不对齐的数据传输。在突发传输中,使用首字节选通方式,只需要首地址,在独立的读写数据通道,采用独立的地址、控制和数据周期进行数据传输,支持非对齐方式的数据传输,能够发出多个未解析的地址,从而完成无序的数据传输交易,并更加容易并行时序收敛。 常用的AXI总线有:AXI4、 AXI_Lite、AXI_Stream。 AXI4:主要面向高性能地址映射通信的需求,允许最大256轮的数据突发传输; AXI4-Lite:是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元; AXI4-Stream:面向高速流数据传输,去掉了地址项,允许无限制的数据突发传输规模。 AXI4总线分为主、从两端,两者间可以连续的进行通信。 AXI协议接口简述AXI4和AXI4-Lite包含5个不同的通道: 1、 读地址通道 2、 写地址通道 3、 读数据通道 4、 写数据通道 5、 读响应通道 数据可以在主从设备间同步的双向传输,并且数据传输大小可以改变。AXI4将数据传输的突发长度限制为最大256,AXI4-Lite每次传输仅运输传输一个数据。 AXI4-Lite接口和AXI4接口类似,但是不支持AXI4的突发传输模式。AXI4-Stream接口仅使用数据通道传输数据流,数据突发长度无限。我们先对AXI4与AXI4_Lite的接口信号进行简要描述,因为他们的接口信号是一样的。 1)全局信号

我们讲完了AXI4的接口信号,那么我们将讲解AXI4遵循的时序要求,这里直接给出AXI4读写的时序要求。 AXI4写时序要求: 因为AXI4协议主要是为了Block Design的搭建而使用的协议,所以我们也以Block design的搭建为一个例子。而Block Design的操作是以IP为基本单元,所以我们得求助于VIVADO的IP封装工具。当我们打开IP封装工具的时候,我们会发现里面给出了AXI4协议的模板,所以我们也就使用上面的模板进行操作。 1、创建IP 然后修改VIVADO给我们提供的AXI4协议历程 myip_v1_0_S00_AXI 模块: `timescale 1ns / 1ps // ********************************************************************************* // Project Name : OSXXXX // Author : zhangningning // Email : [email protected] // Website : https://blog.csdn.net/zhangningning1996 // Module Name : myip_v1_0_S00_AXI.v // Create Time : 2020-06-19 12:48:34 // Editor : sublime text3, tab size (4) // CopyRight(c) : All Rights Reserved // // ********************************************************************************* // Modification History: // Date By Version Change Description // ----------------------------------------------------------------------- // XXXX zhangningning 1.0 Original // // ********************************************************************************* module myip_v1_0_S00_AXI # ( // Users to add parameters here // User parameters ends // Do not modify the parameters beyond this line // Width of S_AXI data bus parameter integer C_S_AXI_DATA_WIDTH = 32, // Width of S_AXI address bus parameter integer C_S_AXI_ADDR_WIDTH = 4 ) ( // Users to add ports here input [ 3:0] key , output reg [ 3:0] led , // User ports ends // Do not modify the ports beyond this line // Global Clock Signal input wire S_AXI_ACLK, // Global Reset Signal. This Signal is Active LOW input wire S_AXI_ARESETN, // Write address (issued by master, acceped by Slave) input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_AWADDR, // Write channel Protection type. This signal indicates the // privilege and security level of the transaction, and whether // the transaction is a data access or an instruction access. input wire [2 : 0] S_AXI_AWPROT, // Write address valid. This signal indicates that the master signaling // valid write address and control information. input wire S_AXI_AWVALID, // Write address ready. This signal indicates that the slave is ready // to accept an address and associated control signals. output wire S_AXI_AWREADY, // Write data (issued by master, acceped by Slave) input wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_WDATA, // Write strobes. This signal indicates which byte lanes hold // valid data. There is one write strobe bit for each eight // bits of the write data bus. input wire [(C_S_AXI_DATA_WIDTH/8)-1 : 0] S_AXI_WSTRB, // Write valid. This signal indicates that valid write // data and strobes are available. input wire S_AXI_WVALID, // Write ready. This signal indicates that the slave // can accept the write data. output wire S_AXI_WREADY, // Write response. This signal indicates the status // of the write transaction. output wire [1 : 0] S_AXI_BRESP, // Write response valid. This signal indicates that the channel // is signaling a valid write response. output wire S_AXI_BVALID, // Response ready. This signal indicates that the master // can accept a write response. input wire S_AXI_BREADY, // Read address (issued by master, acceped by Slave) input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_ARADDR, // Protection type. This signal indicates the privilege // and security level of the transaction, and whether the // transaction is a data access or an instruction access. input wire [2 : 0] S_AXI_ARPROT, // Read address valid. This signal indicates that the channel // is signaling valid read address and control information. input wire S_AXI_ARVALID, // Read address ready. This signal indicates that the slave is // ready to accept an address and associated control signals. output wire S_AXI_ARREADY, // Read data (issued by slave) output wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_RDATA, // Read response. This signal indicates the status of the // read transfer. output wire [1 : 0] S_AXI_RRESP, // Read valid. This signal indicates that the channel is // signaling the required read data. output wire S_AXI_RVALID, // Read ready. This signal indicates that the master can // accept the read data and response information. input wire S_AXI_RREADY ); // AXI4LITE signals reg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_awaddr; reg axi_awready; reg axi_wready; reg [1 : 0] axi_bresp; reg axi_bvalid; reg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_araddr; reg axi_arready; reg [C_S_AXI_DATA_WIDTH-1 : 0] axi_rdata; reg [1 : 0] axi_rresp; reg axi_rvalid; // Example-specific design signals // local parameter for addressing 32 bit / 64 bit C_S_AXI_DATA_WIDTH // ADDR_LSB is used for addressing 32/64 bit registers/memories // ADDR_LSB = 2 for 32 bits (n downto 2) // ADDR_LSB = 3 for 64 bits (n downto 3) localparam integer ADDR_LSB = (C_S_AXI_DATA_WIDTH/32) + 1; localparam integer OPT_MEM_ADDR_BITS = 1; //---------------------------------------------- //-- Signals for user logic register space example //------------------------------------------------ //-- Number of Slave Registers 4 reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg0; reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg1; reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg2; reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg3; wire slv_reg_rden; wire slv_reg_wren; reg [C_S_AXI_DATA_WIDTH-1:0] reg_data_out; integer byte_index; reg aw_en; // I/O Connections assignments assign S_AXI_AWREADY = axi_awready; assign S_AXI_WREADY = axi_wready; assign S_AXI_BRESP = axi_bresp; assign S_AXI_BVALID = axi_bvalid; assign S_AXI_ARREADY = axi_arready; assign S_AXI_RDATA = axi_rdata; assign S_AXI_RRESP = axi_rresp; assign S_AXI_RVALID = axi_rvalid; // Implement axi_awready generation // axi_awready is asserted for one S_AXI_ACLK clock cycle when both // S_AXI_AWVALID and S_AXI_WVALID are asserted. axi_awready is // de-asserted when reset is low. always @( posedge S_AXI_ACLK ) begin if ( S_AXI_ARESETN == 1'b0 ) begin axi_awready |

【本文地址】

今日新闻 |

推荐新闻 |

2)写地址通道信号

2)写地址通道信号  3)写数据通道信号

3)写数据通道信号  4)写响应通道

4)写响应通道 5)读地址通道

5)读地址通道  6)读数据通道

6)读数据通道  对于AXI4_Stream协议,该协议只是数据操作,不涉及地址操作,所以信号比较简单:

对于AXI4_Stream协议,该协议只是数据操作,不涉及地址操作,所以信号比较简单:  上面简要介绍了AXI4_Lite、AXI4、AXI4_Stream三种协议的信号,其中前两种协议接口信号一模一样,只是突发类型不一样。这也就导致了AXI4_Lite用于配置外部寄存器、配置IP的作用;AXI4用于数据传输、DDR的存取;AXI4_Stream用于不同模块的接口信号。

上面简要介绍了AXI4_Lite、AXI4、AXI4_Stream三种协议的信号,其中前两种协议接口信号一模一样,只是突发类型不一样。这也就导致了AXI4_Lite用于配置外部寄存器、配置IP的作用;AXI4用于数据传输、DDR的存取;AXI4_Stream用于不同模块的接口信号。 AXI4读时序要求:

AXI4读时序要求:  知道了接口类型与时序要求,那么我们便可以根据上面的知识编写AXI4的协议,下面便以一个例子为例进行讲解。

知道了接口类型与时序要求,那么我们便可以根据上面的知识编写AXI4的协议,下面便以一个例子为例进行讲解。 2、点击Next

2、点击Next  3、点击创建一个AXI4封装的IP

3、点击创建一个AXI4封装的IP  4、填写IP的名字、版本、描述、目录等信息

4、填写IP的名字、版本、描述、目录等信息  5、进行IP的配置

5、进行IP的配置  1、生成IP的名字 2、选择生成AXI4协议的类型 3、选择是主机还是从机 4、数据的位宽,对于AXI_Lite协议数据位宽恒定是32个,对于AXI4协议可以是64 5、存储器的数目,对于AXI_Full协议的从机需要设置 6、寄存器的数目、对于AXI_Lite协议的从机需要设置

1、生成IP的名字 2、选择生成AXI4协议的类型 3、选择是主机还是从机 4、数据的位宽,对于AXI_Lite协议数据位宽恒定是32个,对于AXI4协议可以是64 5、存储器的数目,对于AXI_Full协议的从机需要设置 6、寄存器的数目、对于AXI_Lite协议的从机需要设置 这里需要注意VIVADO给我们的历程时基于AXI4_Lite循环测试的历程,我们进行修改的话,只需要进行如下操作: 1、添加AXI4_Lite主机发送来数据的用途即可 2、修改AXI4_Lite发起读请求时,根据自己的功能对AXI4_Lite从机的axi_rdata信号即可。 这里为了方便大家理解我们给出源代码: myip_v1_0模块:

这里需要注意VIVADO给我们的历程时基于AXI4_Lite循环测试的历程,我们进行修改的话,只需要进行如下操作: 1、添加AXI4_Lite主机发送来数据的用途即可 2、修改AXI4_Lite发起读请求时,根据自己的功能对AXI4_Lite从机的axi_rdata信号即可。 这里为了方便大家理解我们给出源代码: myip_v1_0模块: