FPGA开发基础 |

您所在的位置:网站首页 › multisim简单灯泡电路仿真 › FPGA开发基础 |

FPGA开发基础

|

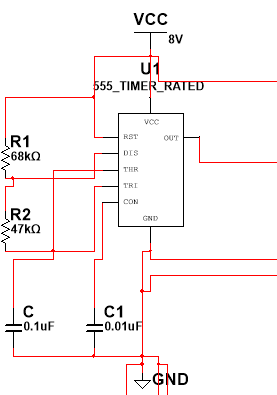

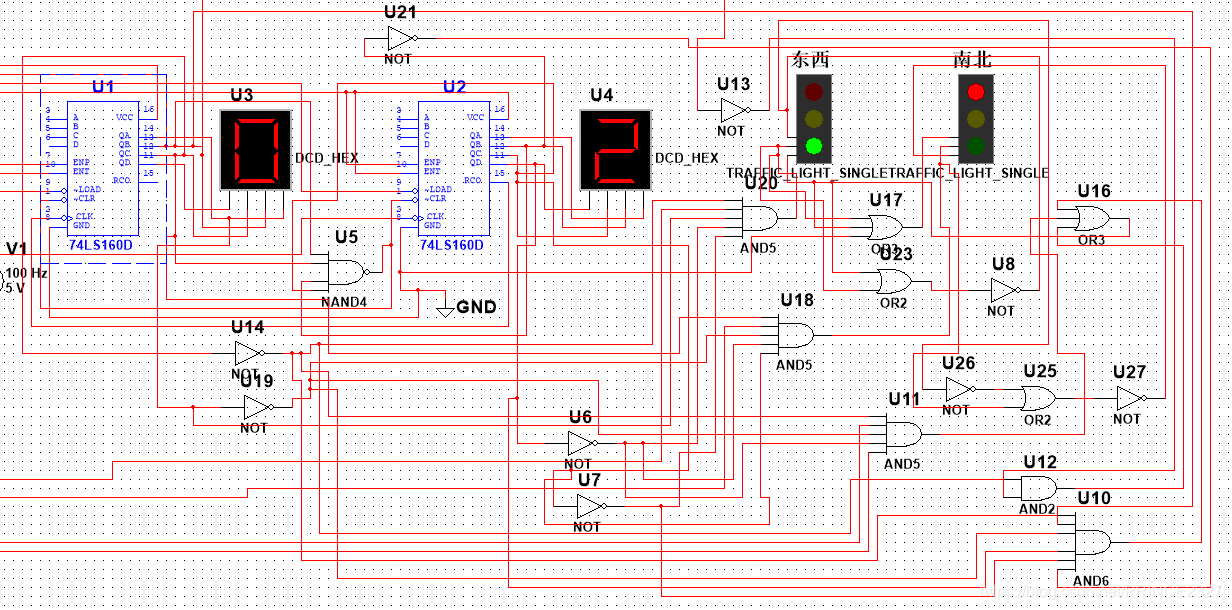

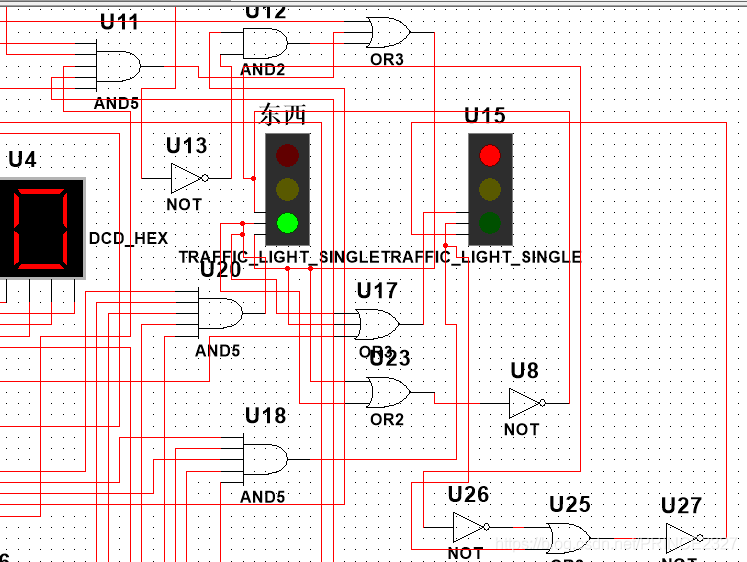

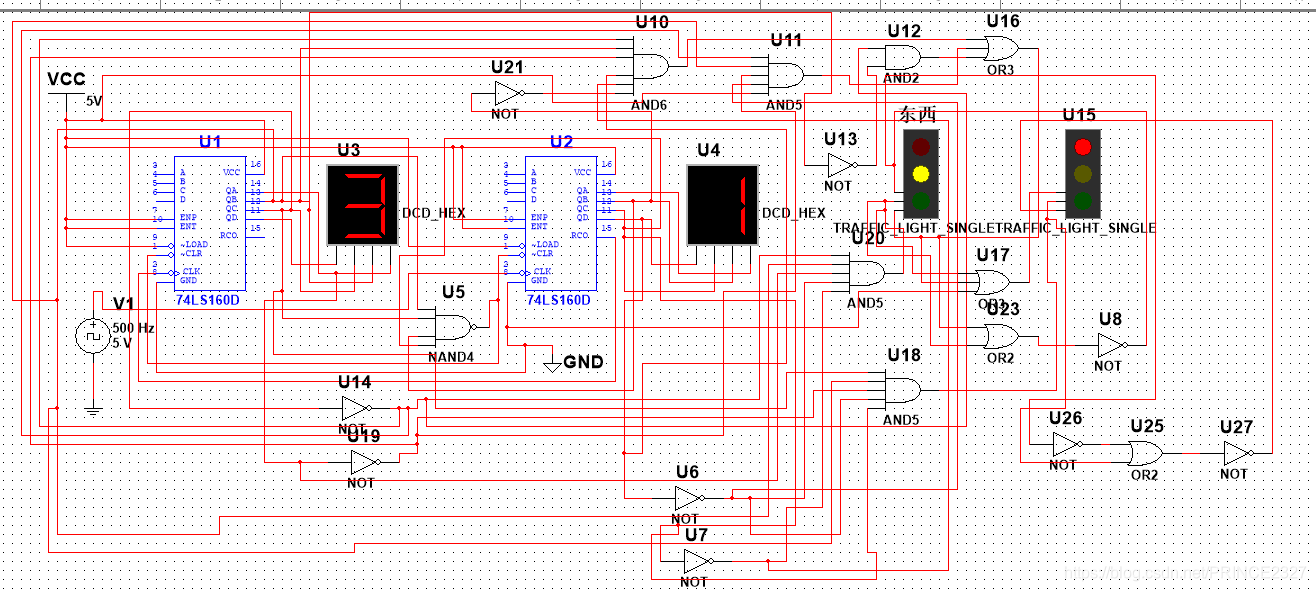

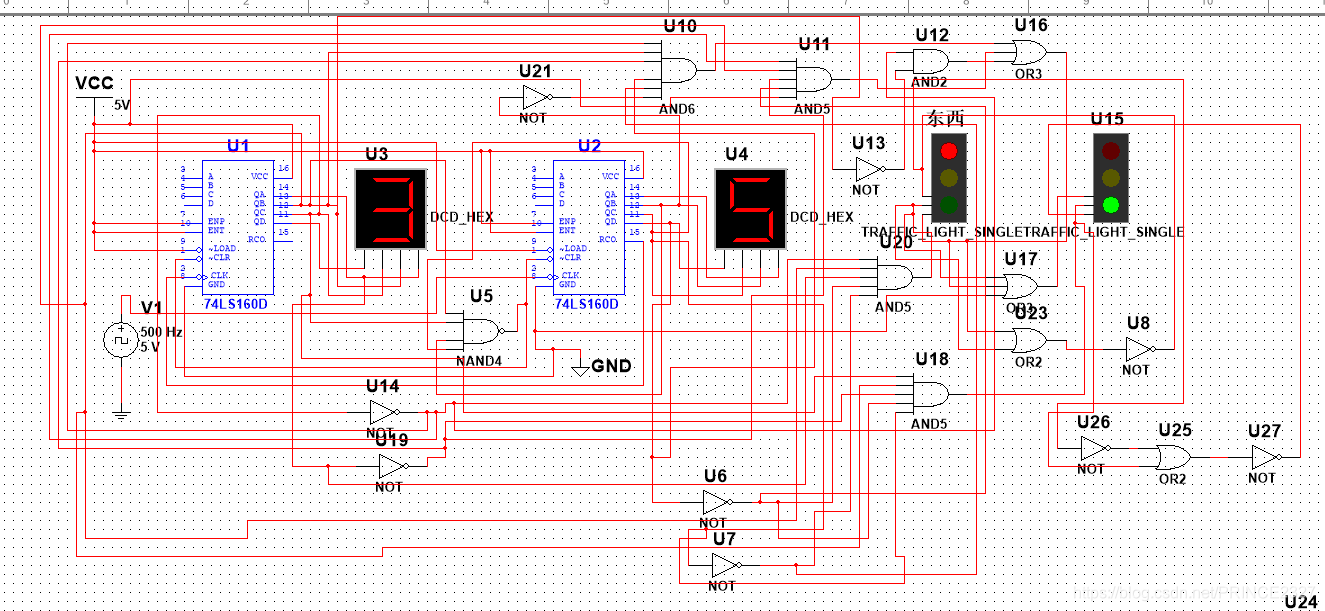

作者:王子齐 学校:电子科技大学 学号:2018151202014 设计目的:完成对于FGPA开发的基础练习,建立FPGA开发思想。 目录 设计要求基于multisim对于交通灯的电路搭建1.1 交通灯电路的组成部分1.2 振荡脉冲模块1.3 计数模块及显示模块1.4 主控模块1.5 信号灯译码模块1.6 总电路及其仿真效果 基于Quartus(verilog)对于交通灯的电路设计1.1 step by step1.1.1 首先给出状态转换表(此处状态编码为S1:000;S2:001:S3:010;S4:011;S5:100,即采用最简的状态编码形式)1.1.2 在1中已经得到了状态转换方程,下面给出状态输出表以便求出输出方程1.1.3 门级电路图。1.2 verilog 代码实现1.3 仿真效果 总结 设计要求设计并实现一个简单的十字路口交通灯控制电路。具体要求:以4个红色指示灯、4个绿色指示灯和4个黄色指示灯模拟路口东西南北4个方向的红绿黄交通灯。控制这些灯,使它们安下列规律亮灭。 1、东西方向绿灯亮,南北方向红灯亮。东西方向通车,时间30秒; 2、东西方向黄灯闪烁,南北方向红灯亮,时间2秒。 3、东西方向红灯亮,南北方向绿灯亮。南北方向通车,时间30秒; 4、东西方向红灯亮,南北方向黄灯闪烁,时间2秒。 5、返回1,继续运行。 要求在仿真软件中设计并运行,或设计实际电路调试运行,提交设计报告电子档,设计报告要求包括:设计方案、电路原理图、测试表格、分析结果总结,实现结果展示(要求用仿真结果截图或者实测照片截图展示实现效果)。 基于multisim对于交通灯的电路搭建 1.1 交通灯电路的组成部分对于交通灯电路,其大致有以下几大模块: 模块作用振荡脉冲模块产生信号源,使电路起振计数及其显示模块对于时间的一种显示,使得我们可以更好地了解交通灯的亮暗时间主控模块电路中最核心的部分,通过一定的数字逻辑关系对于最终的交通灯亮暗加以控制信号灯译码模块译码主控模块的控制信号,将其可视化下面我们逐一进行讨论并给出相应multisim电路图 1.2 振荡脉冲模块振荡脉冲模块事实上就是信号源产生模块,其主要功能就是为整个电路提高时钟脉冲,可以有多种方法去实现,直接使用时钟脉冲信号源或使用555定时器搭建多谐振荡器都可以实现相应目的,下面给出两种实现方法的电路图。 a)直接调用时钟脉冲(在multisim中搜索clock即可) t W 1 = ( R 1 + R 2 ) C t_{W1}=(R_{1}+R_{2})C tW1=(R1+R2)C t W 2 = R 1 C t_{W2}=R_{1}C tW2=R1C T = t W 1 + t W 2 T=t_{W1}+t_{W2} T=tW1+tW2 1.3 计数模块及显示模块计数电路是主控电路的输入源,通过计数电路的适当连接,可以得到我们希望的任意计数序列,而计数序列一方面可以当作时间在显示模块上得以可视化,另一方面又可以通过主控电路从而产生相应的控制信号。 对于显示电路,事实上,如果不考虑实际应用能力而只关心电路本身的性能,那么我们完全可以摒弃显示电路。但考虑在实际应用中,我们等待红绿灯时希望知道它的时间,所以在此加入显示电路。 译码电路采用计数器便可以实现,此处给出一种连接方法: a) 基于74LS160构造的计数器(模64,因为一个交通灯周期为64个时间单位)

主控模块是对电路控制的核心力量,是由一些门电路组成的组合逻辑块。由于主控模块往往是电路设计中较为艰难的部分,所以下面给出详细的推导过程。

计数器U1和U2级联形成模64计数器(0——63)。 根据上述设计要求,东西方向的黄灯只有在每次计数周期中低30—31个计数单位时亮起(前30S为东西方向绿灯亮起),故可列出如下真值表。(由于计数最大只计到63,故我们不关心U1的QD位) 输出项 Q C 1 Q_{C1} QC1 Q B 1 Q_{B1} QB1 Q A 1 Q_{A1} QA1 Q D 2 Q_{D2} QD2 Q C 2 Q_{C2} QC2 Q B 2 Q_{B2} QB2 Q A 2 Q_{A2} QA2 Y 1 Y_{1} Y1 G 1 G_{1} G1 R 1 R_{1} R1 Y 2 Y_{2} Y2 G 2 G_{2} G2 R 2 R_{2} R200000000010001100000010100012000001001000130000011010001400001000100015000010101000160000110010001700001110100018000100001000190001001010001100010000010001110010001010001120010010010001130010011010001140001100010001150010101010001160010110010001170010111010001180011000010001190011001010001200100000010001210100001010001220100010010001230100011010001240100100010001250100101010001260100110010001270100111010001280101000010001290101001010001300110000100000310110001100001320110010001010330110011001010340110100001010350110101001010360110110001010370110111001010380111000001010390111001001010401000000001010411000001001010421000010001010431000011001010441000100001010451000101001010461000110001010471000111001010481001000001010491001001001010501010000001010511010001001010521010010001010531010011001010541010100001010551010101001010561010110001010571010111001010581011000001010591011001001010601100000001010611100001001010621100010001100631100011001100根据上述真值表,可以采用卡诺图化简,下面给出详细推导过程。 (a)对于黄灯信号的卡诺图逻辑化简 对于东西方向的黄灯: Q C 1 Q B 1 Q A 1 = 000 Q_{C1} Q_{B1} Q{A1} = 000 QC1QB1QA1=000 时: Y 1 = 0 , Y 2 = 0 Y_{1}=0 , Y_{2}=0 Y1=0,Y2=0 Q C 1 Q B 1 Q A 1 = 001 Q_{C1} Q_{B1} Q{A1} = 001 QC1QB1QA1=001 时: Y 1 = 0 , Y 2 = 0 Y_{1}=0 , Y_{2}=0 Y1=0,Y2=0 Q C 1 Q B 1 Q A 1 = 010 Q_{C1} Q_{B1} Q{A1} = 010 QC1QB1QA1=010 时: Y 1 = 0 , Y 2 = 0 Y_{1}=0 , Y_{2}=0 Y1=0,Y2=0 Q C 1 Q B 1 Q A 1 = 011 Q_{C1} Q_{B1} Q{A1} = 011 QC1QB1QA1=011 时: Y 1 如 下 , Y 2 = 0 Y_{1}如下 , Y_{2}=0 Y1如下,Y2=0 Y 1 / Q D 2 Y_{1}/Q_{D2} Y1/QD2 Q C 2 Q_{C2} QC200011110 Q B 2 Q_{B2} QB2 Q A 2 Q_{A2} QA2////001000011000110000100000根据卡诺图化简可得到: Y 1 = Q C 1 ′ Q B 1 Q A 1 Q D 2 ′ Q B 2 ′ Q C 2 ′ Y_{1}=Q_{C1}^{'}Q_{B1}Q_{A1}Q_{D2}^ {'}Q_{B2}^{'}Q_{C2}^{'} Y1=QC1′QB1QA1QD2′QB2′QC2′ 同理,对于南北方向的黄灯: Q C 1 Q B 1 Q A 1 = 100 Q_{C1} Q_{B1} Q{A1} = 100 QC1QB1QA1=100 时: Y 1 = 0 , Y 2 = 0 Y_{1}=0 , Y_{2}=0 Y1=0,Y2=0 Q C 1 Q B 1 Q A 1 = 101 Q_{C1} Q_{B1} Q{A1} = 101 QC1QB1QA1=101 时: Y 1 = 0 , Y 2 = 0 Y_{1}=0 , Y_{2}=0 Y1=0,Y2=0 Q C 1 Q B 1 Q A 1 = 110 Q_{C1} Q_{B1} Q{A1} = 110 QC1QB1QA1=110 时: Y 1 = 0 , Y 2 如 下 : Y_{1}=0 , Y_{2}如下: Y1=0,Y2如下: Y 1 / Q D 2 Y_{1}/Q_{D2} Y1/QD2 Q C 2 Q_{C2} QC200011110 Q B 2 Q_{B2} QB2 Q A 2 Q_{A2} QA2////000000010000111000101000根据卡诺图化简可得到: Y 2 = Q C 1 Q B 1 Q A 1 ′ Q D 2 ′ Q B 2 Q C 2 ′ Y_{2}=Q_{C1}Q_{B1}Q_{A1}^{'}Q_{D2}^ {'}Q_{B2}Q_{C2}^{'} Y2=QC1QB1QA1′QD2′QB2QC2′ (b)对于绿灯信号的逻辑推导 对于东西方向绿灯的处理: Q C 1 Q B 1 Q A 1 = 000 Q_{C1} Q_{B1} Q{A1} = 000 QC1QB1QA1=000 时: G 1 = 1 , G 2 = 0 G_{1}=1 , G_{2}=0 G1=1,G2=0 Q C 1 Q B 1 Q A 1 = 001 Q_{C1} Q_{B1} Q{A1} = 001 QC1QB1QA1=001 时: G 1 = 1 , G 2 = 0 G_{1}=1 , G_{2}=0 G1=1,G2=0 Q C 1 Q B 1 Q A 1 = 010 Q_{C1} Q_{B1} Q{A1} = 010 QC1QB1QA1=010 时: G 1 如 下 , G 2 = 0 G_{1}如下 , G_{2}=0 G1如下,G2=0 G 1 / Q D 2 G_{1}/Q_{D2} G1/QD2 Q C 2 Q_{C2} QC200011110 Q B 2 Q_{B2} QB2 Q A 2 Q_{A2} QA2////001101011101111100101100根据卡诺图化简可有: G 1 = Q C 1 ′ Q B 1 ′ + Q C 1 ′ Q B 1 + Q C 1 ′ Q B 1 Q A 1 ′ Q D 2 Q B 2 ′ Q C 2 ′ G_{1}=Q_{C1} ^ {'}Q_{B1} ^ {'}+Q_{C1} ^ {'}Q_{B1} +Q_{C1}^{'}Q_{B1}Q_{A1}^ {'}Q_{D2}Q_{B2} ^ {'}Q_{C2}^{'} G1=QC1′QB1′+QC1′QB1+QC1′QB1QA1′QD2QB2′QC2′ 对于南北方向绿灯的处理: 南北方向上的绿灯可以通过卡诺图化简,但更加便捷的方法是:当东西方向红灯亮且南北方向黄灯不亮时,则南北方向绿灯亮,基于此思想可以得到: G 2 = ( R 1 + Y 2 ′ ) ′ G_{2}=(R_{1}+Y_{2}^{'})^{'} G2=(R1+Y2′)′ ©对于红灯信号的巧妙处理 对于东西方向红灯的处理: 当南北方向绿灯或黄灯亮时,东西方向红灯亮,故有: R 1 = G 2 + Y 2 R_{1}=G_{2}+Y_{2} R1=G2+Y2 对于南北方向红灯的处理: 当东西方向灯或黄灯亮时,南北方向红灯亮,故有: R 1 = G 2 + Y 2 R_{1}=G_{2}+Y_{2} R1=G2+Y2 1.5 信号灯译码模块当主控电路构建完成后,根据逻辑表达式连接到相应信号灯上即可。如下图: 电路整体搭建效果如下图:

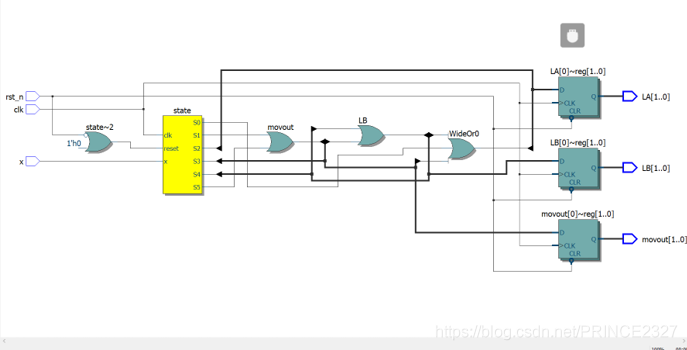

在介绍了multisim搭建电路实现交通灯的方法后,接下来介绍如何利用FPGA的思想去实现。 1.1 step by step 1.1.1 首先给出状态转换表(此处状态编码为S1:000;S2:001:S3:010;S4:011;S5:100,即采用最简的状态编码形式)

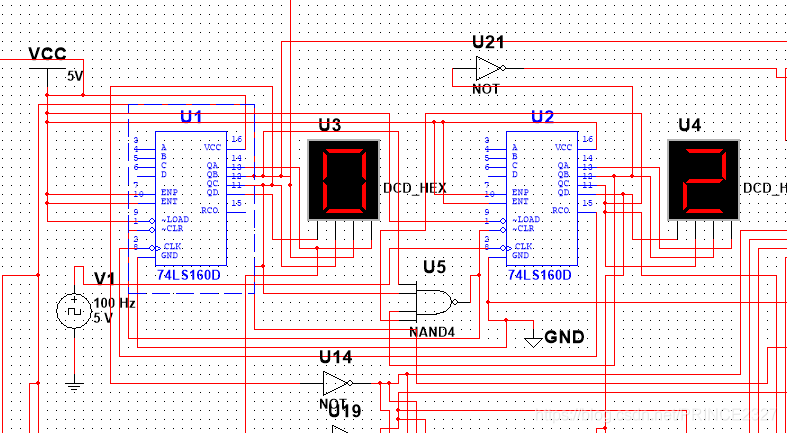

下面给出相应代码(verilog): timescale 1 ps/ 1 ps // 规定时间规模与时间精度 module trafficlight ( //建立模块 input clk, input rst_n, //端口说明 input x, output reg [1:0] LA, // 指明LA为两位reg型输出 output reg [1:0]LB, // 指明LB为两位reg型输出 output reg [1:0]movout // 指明movout为两位reg型输出 ); reg [2 : 0] state; //创立三位数组 parameter S0=0, S1=1, S2=2, //规定参数 S3=3, S4=4, S5=5; always@(posedge clk or negedge rst_n) //always块语句,括号中为敏感条件 Begin //begin-end语句 if(!rst_n) //当rst_n为0时,执行下列语句 begin LA=2'b00; // 将2位二进制数00赋值给LA LB=2'b00; movout=2'b00; //其余类似 state |

【本文地址】

今日新闻 |

推荐新闻 |

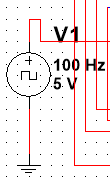

b)使用555搭建的多谐振荡器(在multisim中搜索555即可)

b)使用555搭建的多谐振荡器(在multisim中搜索555即可)  如上图,此时的OUT等效于某个频率的时钟脉冲信号,通过调节R1,R2,C的值可以改变输出的频率,下面给出相应公式以便读者自行调节脉冲频率:

如上图,此时的OUT等效于某个频率的时钟脉冲信号,通过调节R1,R2,C的值可以改变输出的频率,下面给出相应公式以便读者自行调节脉冲频率: 级联方式非常简单,采用清零法级联即可。

级联方式非常简单,采用清零法级联即可。 我们令计数器U1的输出为

Q

A

1

Q_{A1}

QA1

Q

B

1

Q_{B1}

QB1

Q

C

1

Q_{C1}

QC1

Q

D

1

Q_{D1}

QD1 ,令计数器U2的输出为

Q

A

2

Q_{A2}

QA2

Q

B

2

Q_{B2}

QB2

Q

C

2

Q_{C2}

QC2

Q

D

2

Q_{D2}

QD2。令东西方向的黄灯,绿灯和红灯输出分别为

Y

1

Y_{1}

Y1

G

1

G_{1}

G1

R

1

R_{1}

R1,南北方向的黄灯,绿灯和红灯输出分别为

Y

2

Y_{2}

Y2

G

2

G_{2}

G2

R

2

R_{2}

R2。

我们令计数器U1的输出为

Q

A

1

Q_{A1}

QA1

Q

B

1

Q_{B1}

QB1

Q

C

1

Q_{C1}

QC1

Q

D

1

Q_{D1}

QD1 ,令计数器U2的输出为

Q

A

2

Q_{A2}

QA2

Q

B

2

Q_{B2}

QB2

Q

C

2

Q_{C2}

QC2

Q

D

2

Q_{D2}

QD2。令东西方向的黄灯,绿灯和红灯输出分别为

Y

1

Y_{1}

Y1

G

1

G_{1}

G1

R

1

R_{1}

R1,南北方向的黄灯,绿灯和红灯输出分别为

Y

2

Y_{2}

Y2

G

2

G_{2}

G2

R

2

R_{2}

R2。

相应仿真结果如下:

相应仿真结果如下:

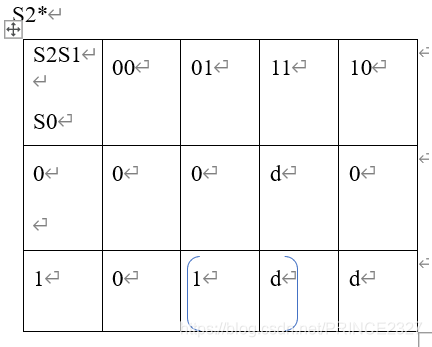

(注:此处设计采用最小成本法) 根据卡诺图化简可得:S2*=S1S0

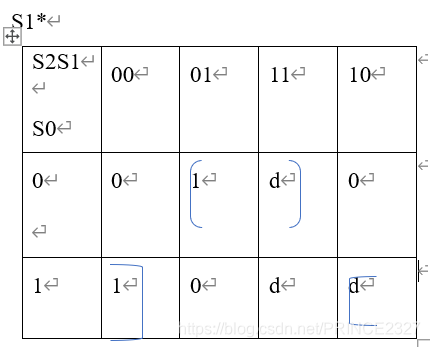

(注:此处设计采用最小成本法) 根据卡诺图化简可得:S2*=S1S0 (注:此处仍然采用最小成本法) 由卡诺图化简可得:S1*=S1S0’+S1’S0

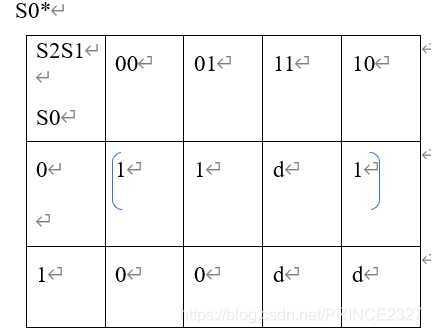

(注:此处仍然采用最小成本法) 由卡诺图化简可得:S1*=S1S0’+S1’S0 (注:此处仍然采用最小成本法) 由卡诺图化简可得:S0*=S0’

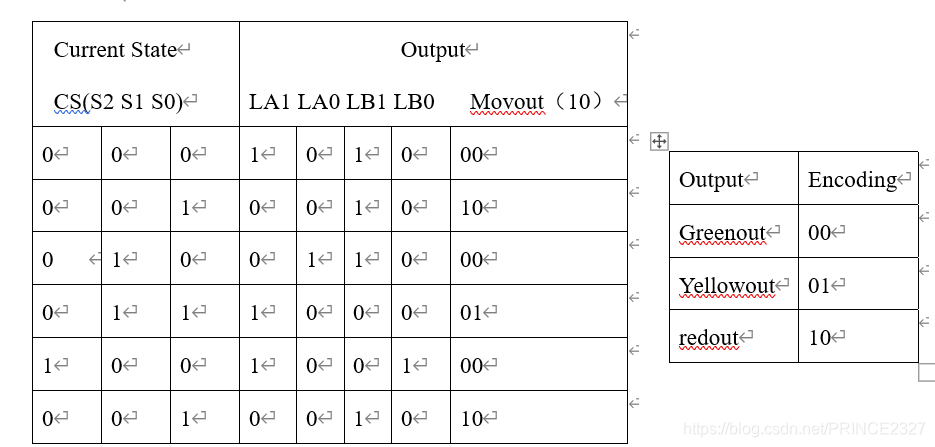

(注:此处仍然采用最小成本法) 由卡诺图化简可得:S0*=S0’ (注:LA为东西方向的灯,LB为南北方向的灯)

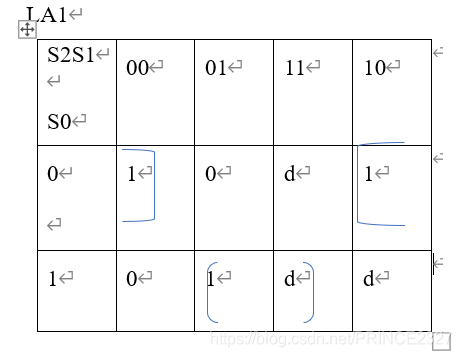

(注:LA为东西方向的灯,LB为南北方向的灯) (注:此处仍然采用最小成本法) 可有:LA1=S1’S0’

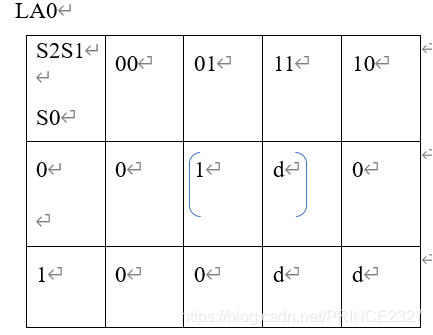

(注:此处仍然采用最小成本法) 可有:LA1=S1’S0’ (注:此处仍然采用最小成本法) 可有:LA0=S1S0’

(注:此处仍然采用最小成本法) 可有:LA0=S1S0’ (注:此处仍然采用最小成本法) 可有:LB1=S2’S0’+S2’S1’

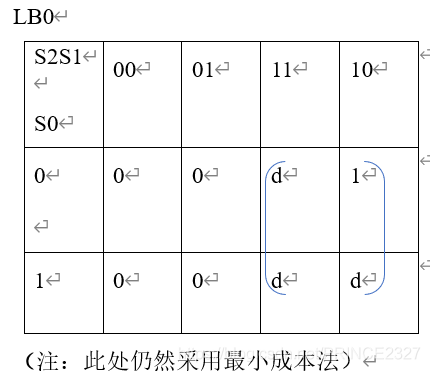

(注:此处仍然采用最小成本法) 可有:LB1=S2’S0’+S2’S1’ (注:此处仍然采用最小成本法) 可有:LB0=S2

(注:此处仍然采用最小成本法) 可有:LB0=S2 (注:此处仍然采用最小成本法) 可有:Movout1=S1’S0

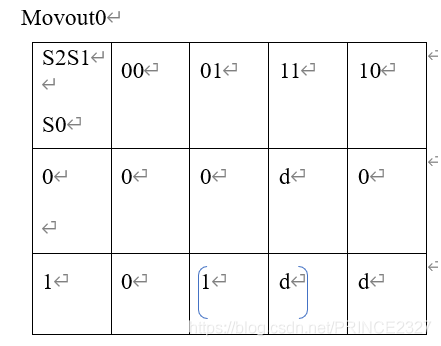

(注:此处仍然采用最小成本法) 可有:Movout1=S1’S0 (注:此处仍然采用最小成本法) 可有:Movout0=S1S0

(注:此处仍然采用最小成本法) 可有:Movout0=S1S0