浅析MOS管导通过程及RC吸收电路设计要点 |

您所在的位置:网站首页 › mos管驱动电阻并联二极管作用 › 浅析MOS管导通过程及RC吸收电路设计要点 |

浅析MOS管导通过程及RC吸收电路设计要点

|

MOS管导通过程

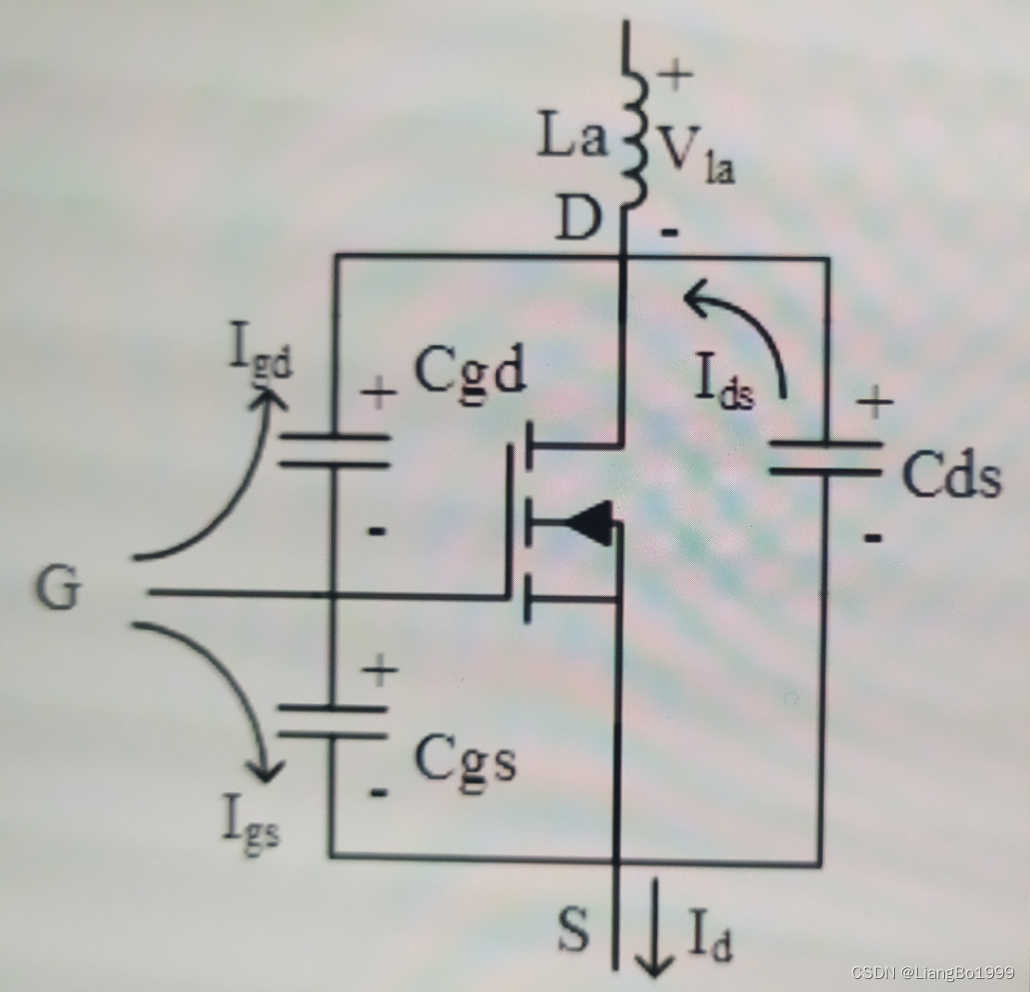

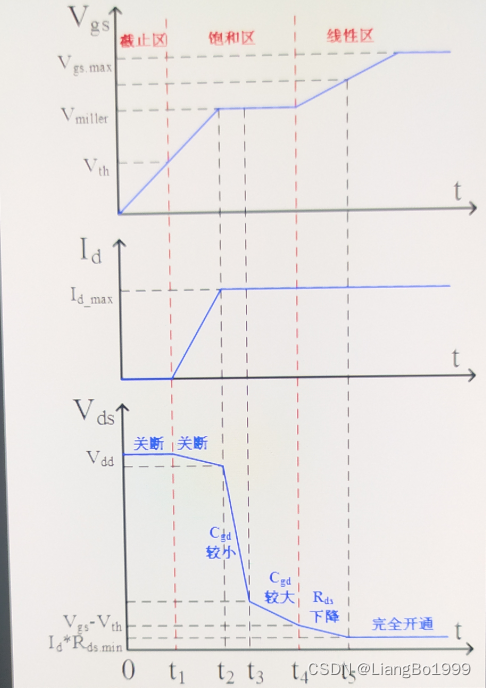

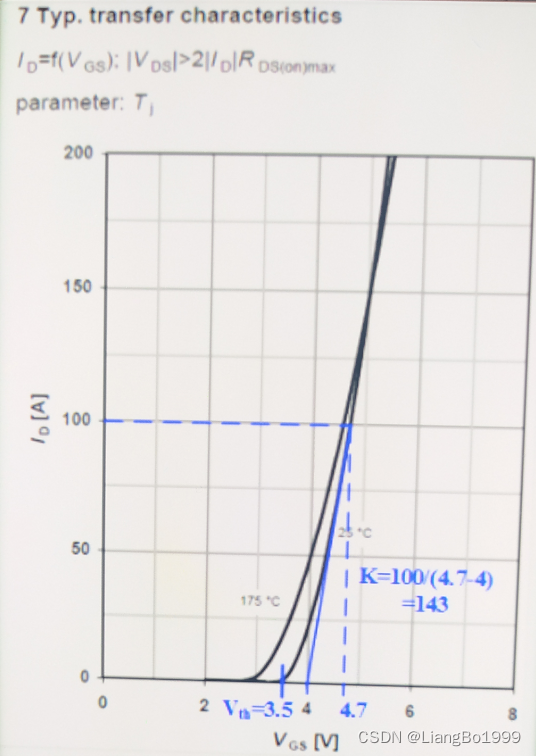

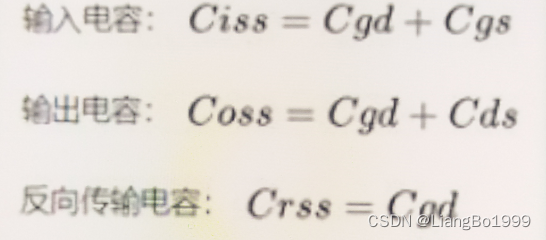

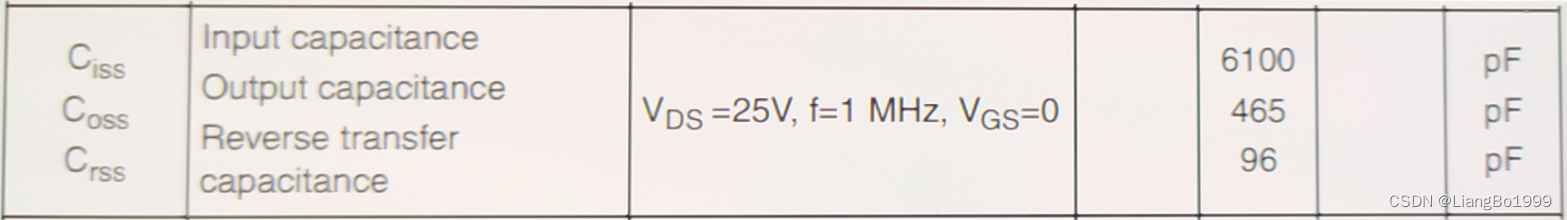

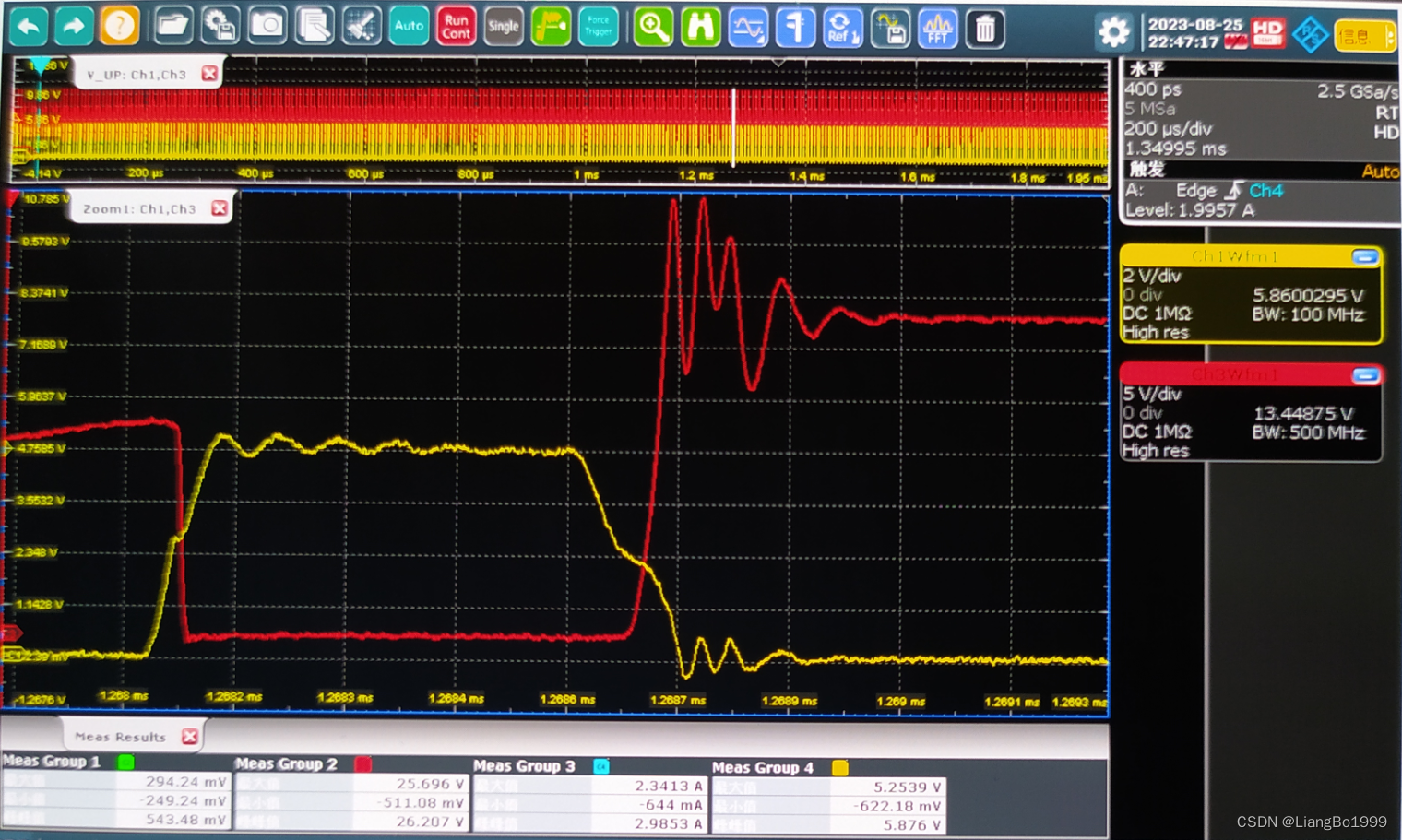

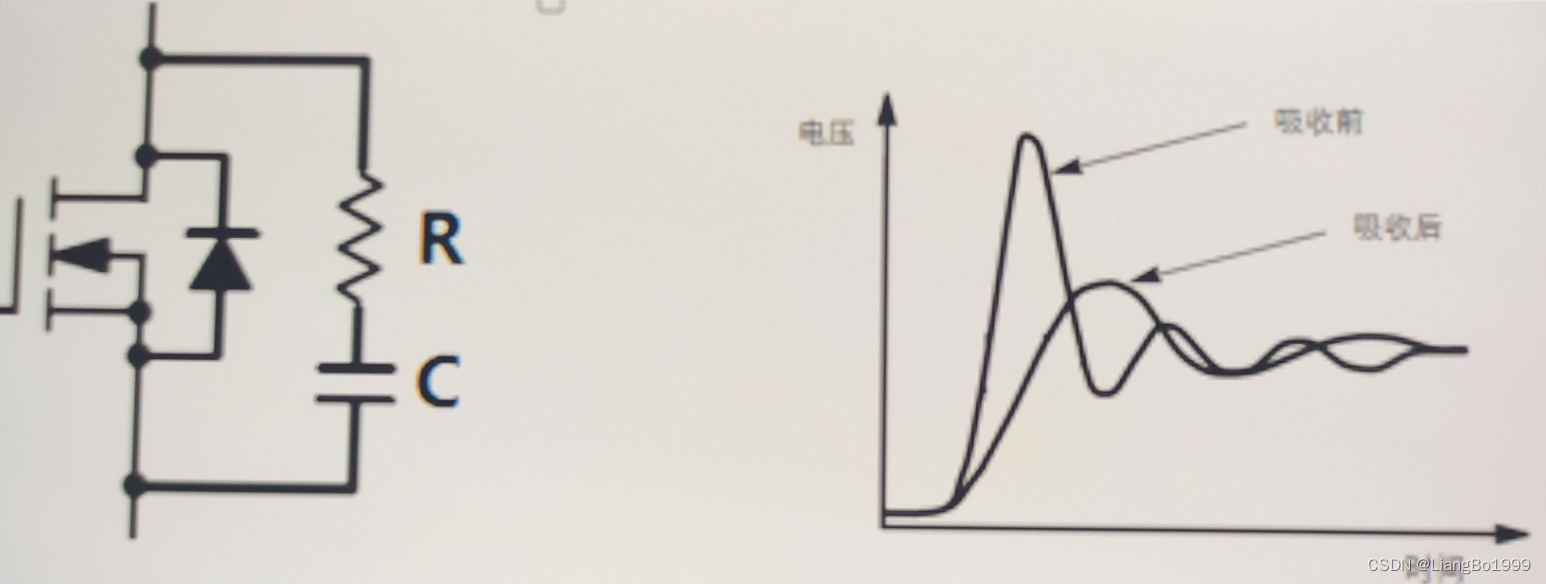

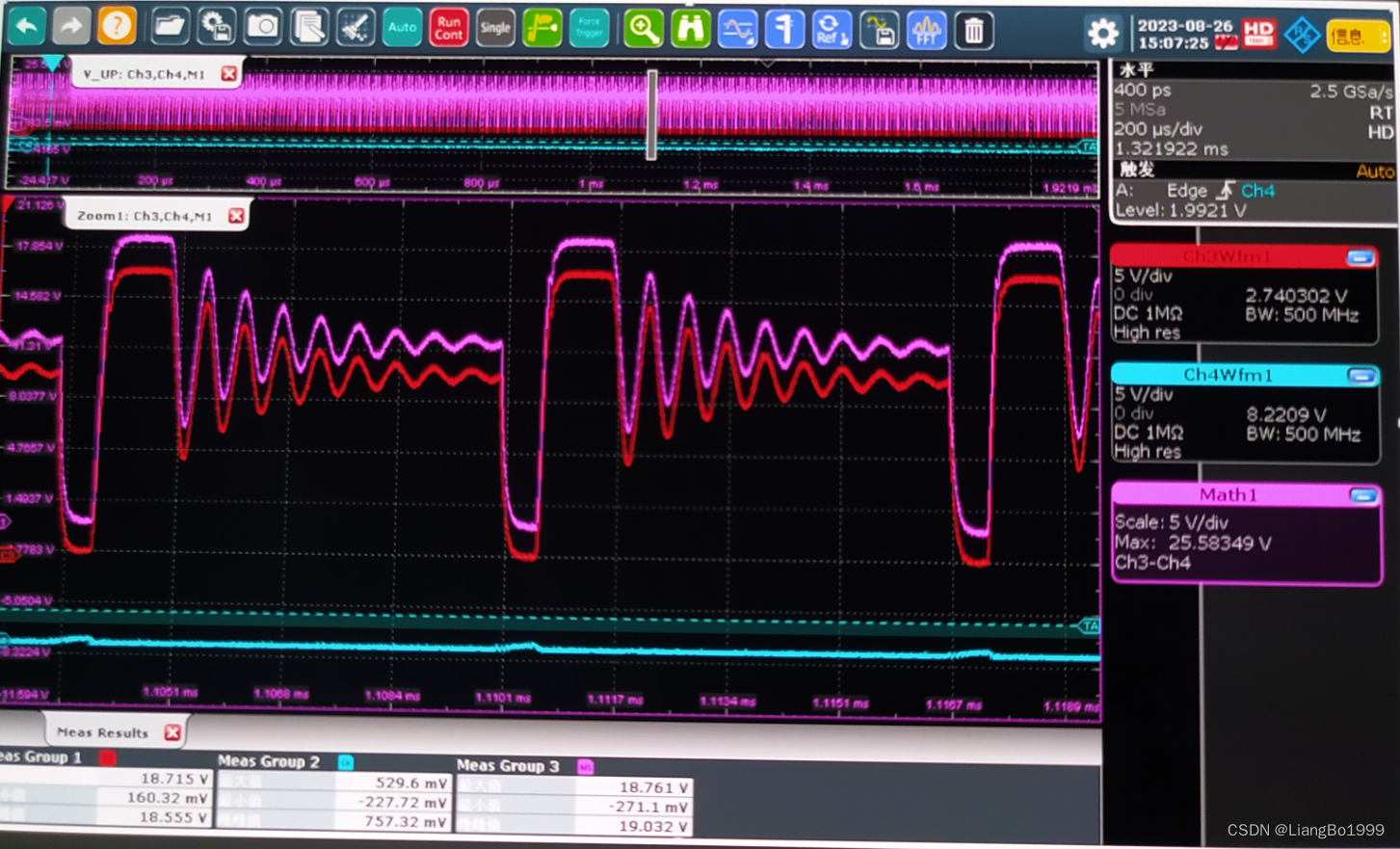

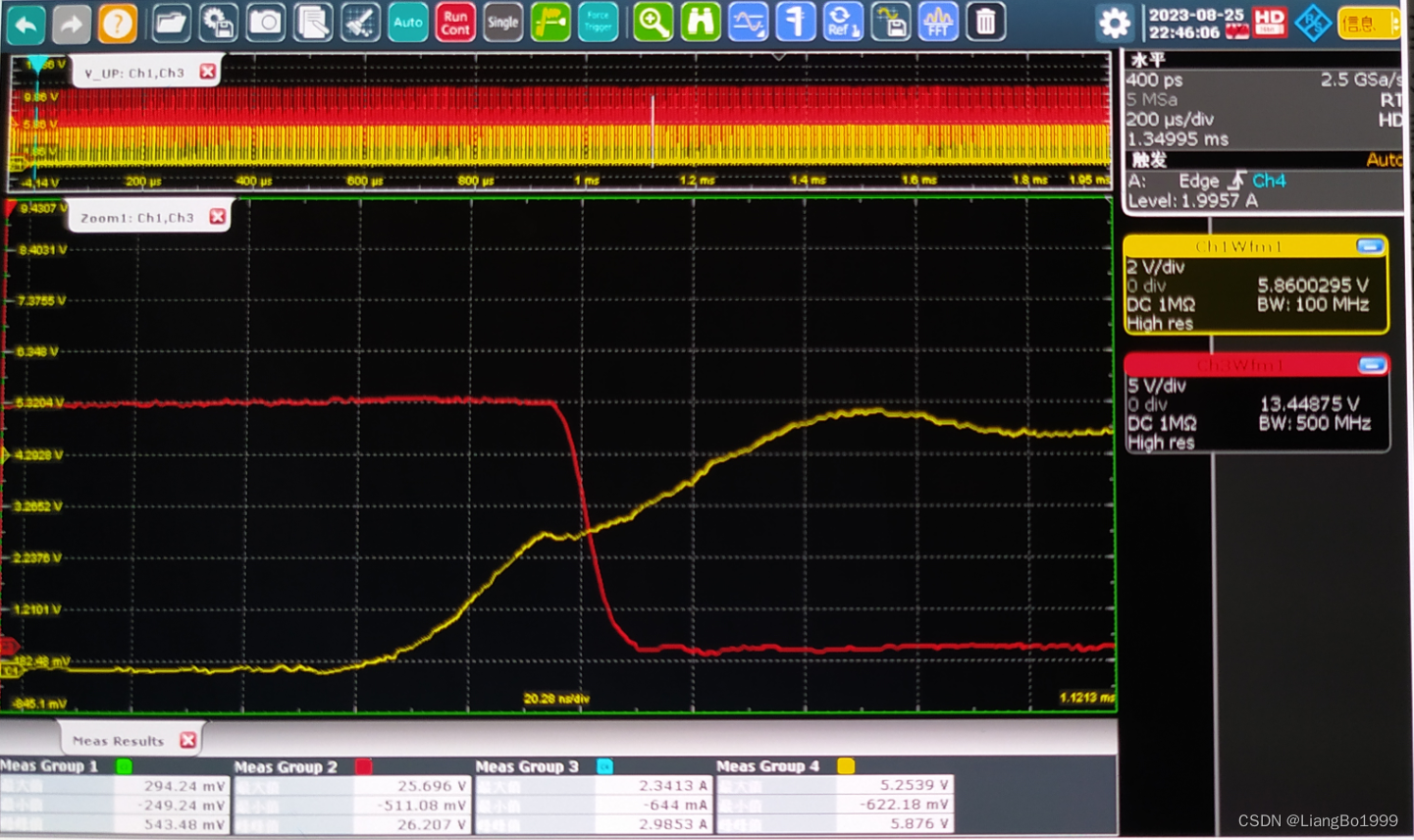

上图为MOS管寄生参数的等效电路图,La为MOS外部的杂散电感,Cgd、Cgs为MOS寄生电容 1、0到t1过程 门极驱动电流ig为Cgs充电,Vgs上升,Vds和Id保持不变,因为在此阶段MOS处于截止区。 2、t1到t2过程 t1时刻,Vgs上升至门极开启电压Vth,MOS开始导通,漏极电流Id从0上升至Id_max后维持恒定,Id_max电流的大小由电路工作状态决定。在Id上升的过程中,Vds略有压降,这是MOS的D极和S极上的杂散电感La在Id上升时产生了感应电压导致的。在t2之前,由于Vds大于Vgs,因此Cgd电容被充电,电压上正下负,门极电流Ig仅对Cgs充电,因此Vgs继续上升。 3、t2到t4过程 t2时刻漏极电流Id达到最大值,开始进入米勒平台。米勒平台就是Vgs在一端时间内几乎不变的一个平台。MOS从t1时刻开始导通,会先进入饱和区,此时MOS具有转移特性——栅源电压Vgs控制漏极电流Id的特性,如下图所示: 即Id=f(Vgs),可以近似为Id=Gm*(Vgs-d),其中Gm是跨导,定义为Gm=Delta Id/Delta Vgs。在转移特性下,若Id不变,则Vgs不变。 下面分析内在过程。从t1开始,Vgs >Vth开始导通(MOS进入饱和区),由转移特性可知,Vgs增大时,Id对应地增大。到t2时刻,Vgs继续增大一个Delta Vgs时,由转移特性,MOS沟道电流Ich也会增大一个Delta Ich(其中Ich=Id+Ids)。但由于Id达到最大值无法继续增大,因此增量Delta Ich由Cds放电提供——Delta Ich=Delta Ids=CdsDelta Vds,所以Vds电压降低。而Vds减小会导致Vgd减小,从而导致Cgd放电——Igd=Cgd(Delta Vgd/Delta t),因此门极电流Ig向Cgd分流,Igs就会减小,Vgs就无法继续上升,形成了一个负反馈,最终Vgs动态地维持在米勒平台附近,而Cds和Cgd持续放电,Vds持续降低。 该过程中Vds下降不单调,这是因为Cgd的容值是变化的,且当Cgd容值较大时,Vds下降较慢。从上述分析中可知,当Vgs动态维持在米勒平台附近时,沟道电流的增量Delta Ich是有限的,所以可以认为Igd=Cgd*(Delta Vgd/Delta t)也是有限的,当Cgd较大时,Delta Vgd/Delta t就会较小,即Vds的变化率较小,Vds下降较慢。 4、t4到t5过程 t4时刻,Vds降低至Vgs-Vth,此时Vgs>Vds,门极电流Ig同时给Cgs和Cgd充电,因此Vgs开始继续上升(脱离米勒平台),MOS进入线性区,即 Vds=IdRds。随着Vgs上升,Rds会降低至最小值Rds.min,此时Vds降低至最低值IdRds.min,此时MOS完全开通。 查阅多个规格书发现Cgs远大于Cgd 实测波形 由上图可知VDS存在明显震荡,在MOS关断时候产生电压尖峰的原因主要有以下3种: 1、变压器的漏感过大; 2、驱动电路设计不合理造成MOS管的导通过快; 3、初级吸收电路设计不合理难以吸收关断时造成的尖峰; 因此需使用RC吸收电路 由下图可知:在DS间加RC后VDS震荡明显减轻 关于RC吸收电路的设计: (1)去掉开关器件两端所有吸收电路,用示波器测量波形,记录这时的谐振频率,记为fo。 (2)在开关器件两端并联电容C,使这时的谐振频率为原频率的一半。(使用不同容值电容多次试验) (3)计算出吸收电阻:R=1/(6.28foC/3) (4)计算吸收电阻功率:P=CV2Fw(V为C两端的电压峰值,Fw为开关器件两端的开关频率) |

【本文地址】

今日新闻 |

推荐新闻 |