基于FPGA的FIR低通滤波器verilog实现,包含testbench和滤波器系数计算matlab程序 |

您所在的位置:网站首页 › matlab低通滤波器参数设计 › 基于FPGA的FIR低通滤波器verilog实现,包含testbench和滤波器系数计算matlab程序 |

基于FPGA的FIR低通滤波器verilog实现,包含testbench和滤波器系数计算matlab程序

|

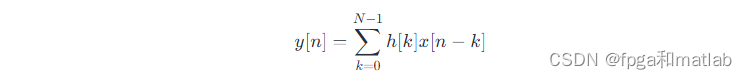

目录 1.FIR滤波器基础 2.滤波器系数计算(Matlab) 3.核心verilog程序 4.仿真结论 基于FPGA(Field-Programmable Gate Array)的FIR(Finite Impulse Response)低通滤波器实现,是数字信号处理领域中的一项重要技术应用。它利用可编程逻辑器件的灵活性,高效地实现数字滤波功能。FIR滤波器因其稳定性好、线性相位特性以及易于实现等优点,在数字信号处理领域有着广泛应用。下面将从FIR滤波器的基本概念、设计原理、系数计算、Verilog实现以及测试平台(testbench)的设计等方面进行详细介绍, 1.FIR滤波器基础FIR(Finite Impulse Response)低通滤波器是一种数字信号处理领域中常用的滤波器类型,其特点是具有有限长度的冲击响应。这意味着,对于任何输入信号,FIR滤波器的输出只依赖于输入信号的最近的N个样本,其中N是滤波器的阶数或长度。相比于IIR(Infinite Impulse Response)滤波器,FIR滤波器通常更容易实现线性相位特性,并且总是稳定的。 FIR滤波器是一种在数字信号处理中广泛使用的滤波器,具有有限的脉冲响应。这意味着它对输入信号的响应在有限时间内归零,与无限脉冲响应(IIR)滤波器形成对比,后者的响应理论上可以持续无限长时间。 FIR滤波器的输出y[n]是输入序列x[n]与滤波器系数h[k]的卷积之和,即

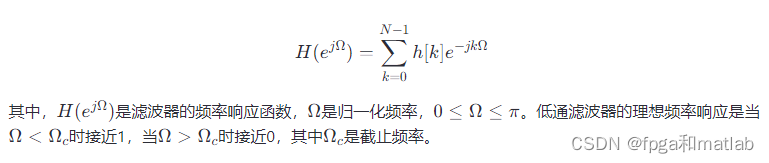

其中,N是滤波器的阶数,h[k]是滤波器的系数,k是系数索引,n是时间索引。 低通滤波器允许低频信号通过,而抑制高频信号,其频率响应满足

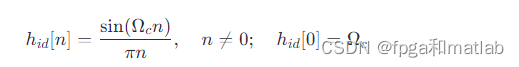

FIR滤波器系数的计算可以使用多种设计方法,如窗函数法、频率采样法、最小平方误差法等。以窗函数法为例,步骤如下: 确定滤波器规格:选择截止频率Ωc,过渡带宽度,通带和阻带纹波等。选择窗函数:常见的有矩形窗、汉明窗、海明窗等,窗函数的选择会影响滤波器的过渡带陡峭度和旁瓣衰减。计算理想冲击响应:对于低通滤波器,理想冲击响应hid[n]为

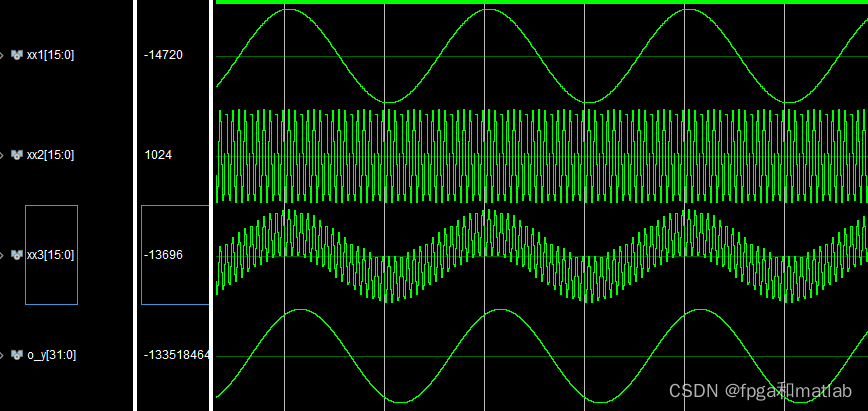

以窗函数设计为例,设计步骤如下: 确定滤波器规范:指定截止频率、通带纹波、阻带衰减等。选择窗函数:如矩形窗、汉明窗、布莱克曼窗等,窗函数类型影响滤波器性能。计算理想冲击响应:对于低通滤波器,理想冲击响应为 sinc 函数的截断。应用窗函数:理想响应乘以窗函数,得到实际滤波器系数。设计FIR滤波器的方法有很多,包括但不限于窗函数设计法、频率采样设计法、 Parks-McClellan算法(也称为最优化等波纹设计法)等。在MATLAB中,可以使用如fdatool GUI工具或者命令行函数(如fir1, fir2, designfilt等)来设计FIR滤波器,这些工具允许用户指定所需的滤波器参数,并自动计算出滤波器系数。 一旦设计完成,滤波器系数会被应用于输入信号,通常采用卷积操作来实现滤波过程。在硬件实现上,如FPGA或单片机中,这些系数会被转化为查找表(LUT)或其他硬件结构来加速处理速度。 3.核心verilog程序 `timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2023/09/12 19:28:25 // Design Name: // Module Name: sim // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module TEST(); reg i_clk; reg i_rst; wire signed [31:0]o_y; initial begin i_rst = 1; #15; i_rst = 0; end initial begin i_clk = 0; forever #5 i_clk = ~i_clk; end //使用DDS模拟测试信号 wire [15 : 0] m_axis_data_tdata1; dds_compiler_0 dds_compiler_01 ( .aclk(i_clk), // input wire aclk .aresetn(~i_rst), // input wire aresetn .m_axis_data_tvalid(), // output wire m_axis_data_tvalid .m_axis_data_tdata(m_axis_data_tdata1) // output wire [15 : 0] m_axis_data_tdata ); wire signed[15:0]xx1 = {m_axis_data_tdata1[7],m_axis_data_tdata1[7:0],7'd0}; wire [15 : 0] m_axis_data_tdata2; dds_compiler_1 dds_compiler_12 ( .aclk(i_clk), // input wire aclk .aresetn(~i_rst), // input wire aresetn .m_axis_data_tvalid(), // output wire m_axis_data_tvalid .m_axis_data_tdata(m_axis_data_tdata2) // output wire [15 : 0] m_axis_data_tdata ); wire signed[15:0]xx2 = {m_axis_data_tdata2[7],m_axis_data_tdata2[7:0],7'd0}; wire signed[15:0]xx3 =xx1+xx2; FIR_filter U1( .i_clk(i_clk), .i_rst(i_rst), .i_x(xx3), .o_y(o_y) ); endmodule up4088 4.仿真结论

从仿真结果可知,正弦信号中的高频分量被成功滤除。 |

【本文地址】

今日新闻 |

推荐新闻 |