(超级详细教程)cadence从原理图到版图layout,DRC、LVS、PEX、RVE后仿真AMS完整流程+SAR ADC项目 |

您所在的位置:网站首页 › layout图层设置 › (超级详细教程)cadence从原理图到版图layout,DRC、LVS、PEX、RVE后仿真AMS完整流程+SAR ADC项目 |

(超级详细教程)cadence从原理图到版图layout,DRC、LVS、PEX、RVE后仿真AMS完整流程+SAR ADC项目

|

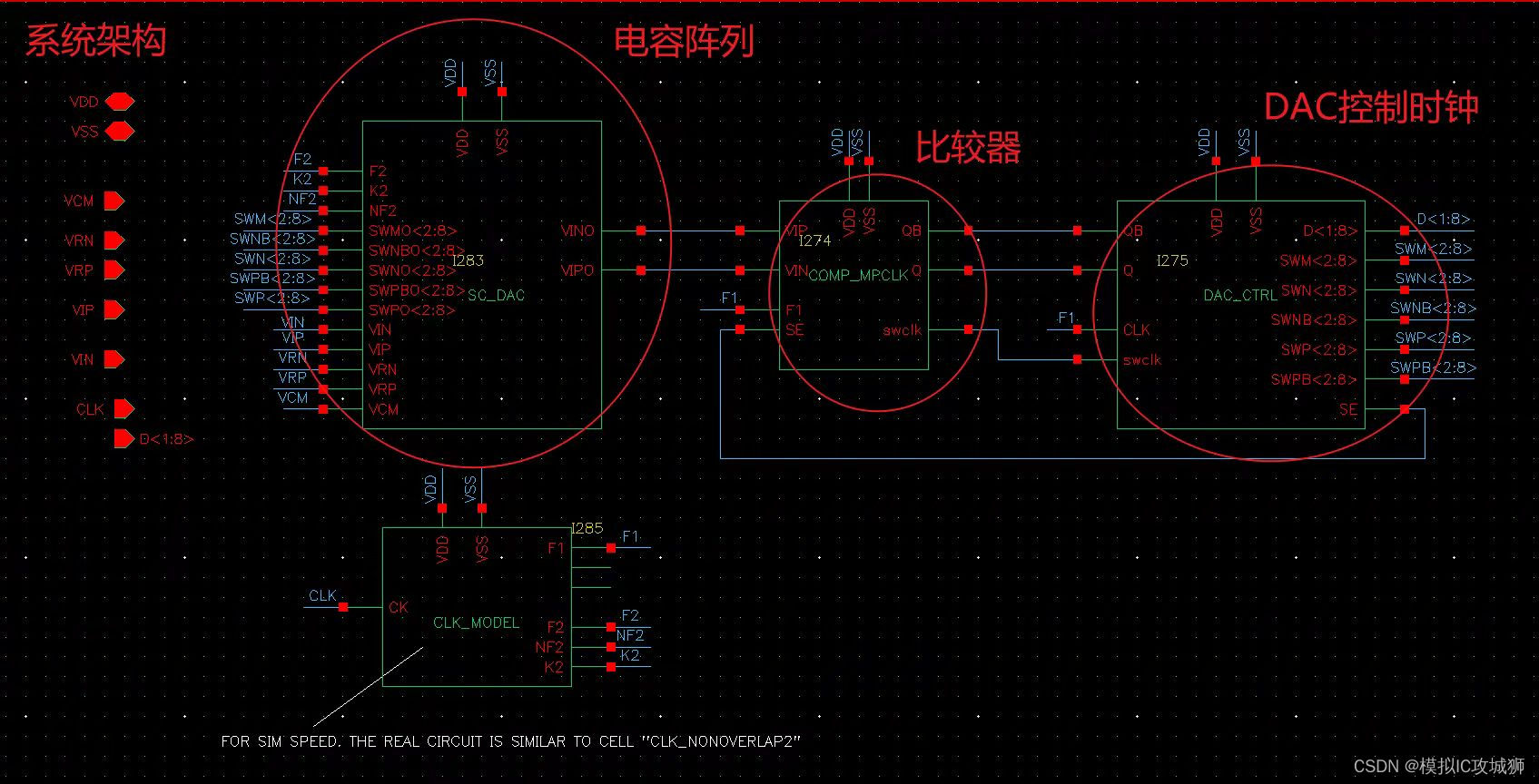

cadence从原理图到版图layout,DRC、LVS、PEX、RVE后仿真AMS完整流程+SAR ADC项目

SAR ADC详细介绍传送门(点这里!!!)

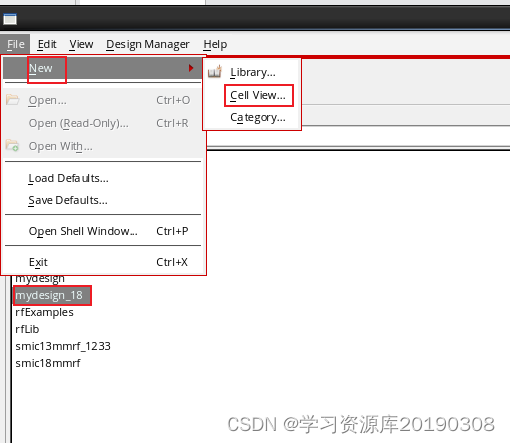

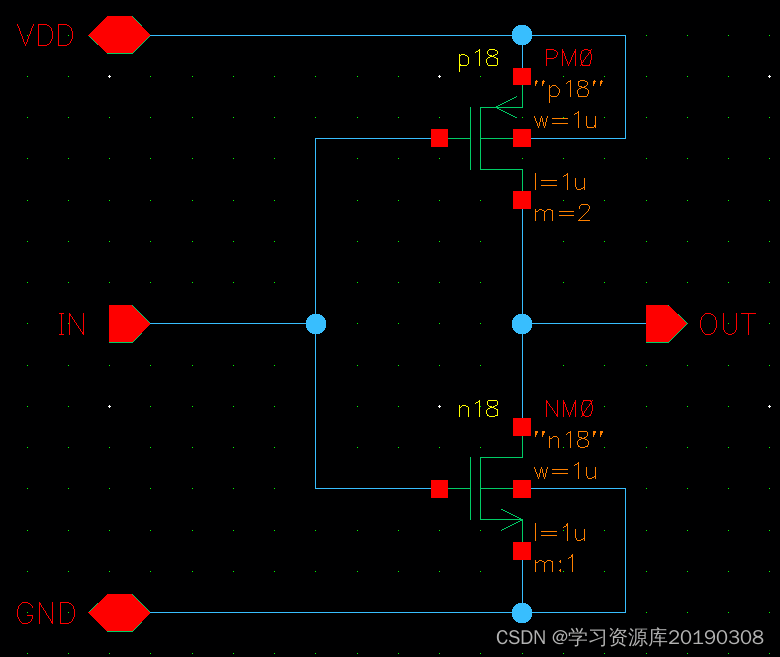

以反相器为例 一、原理图绘制(这里先略过)

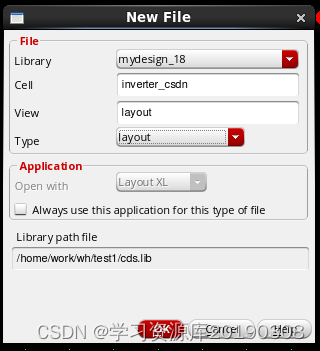

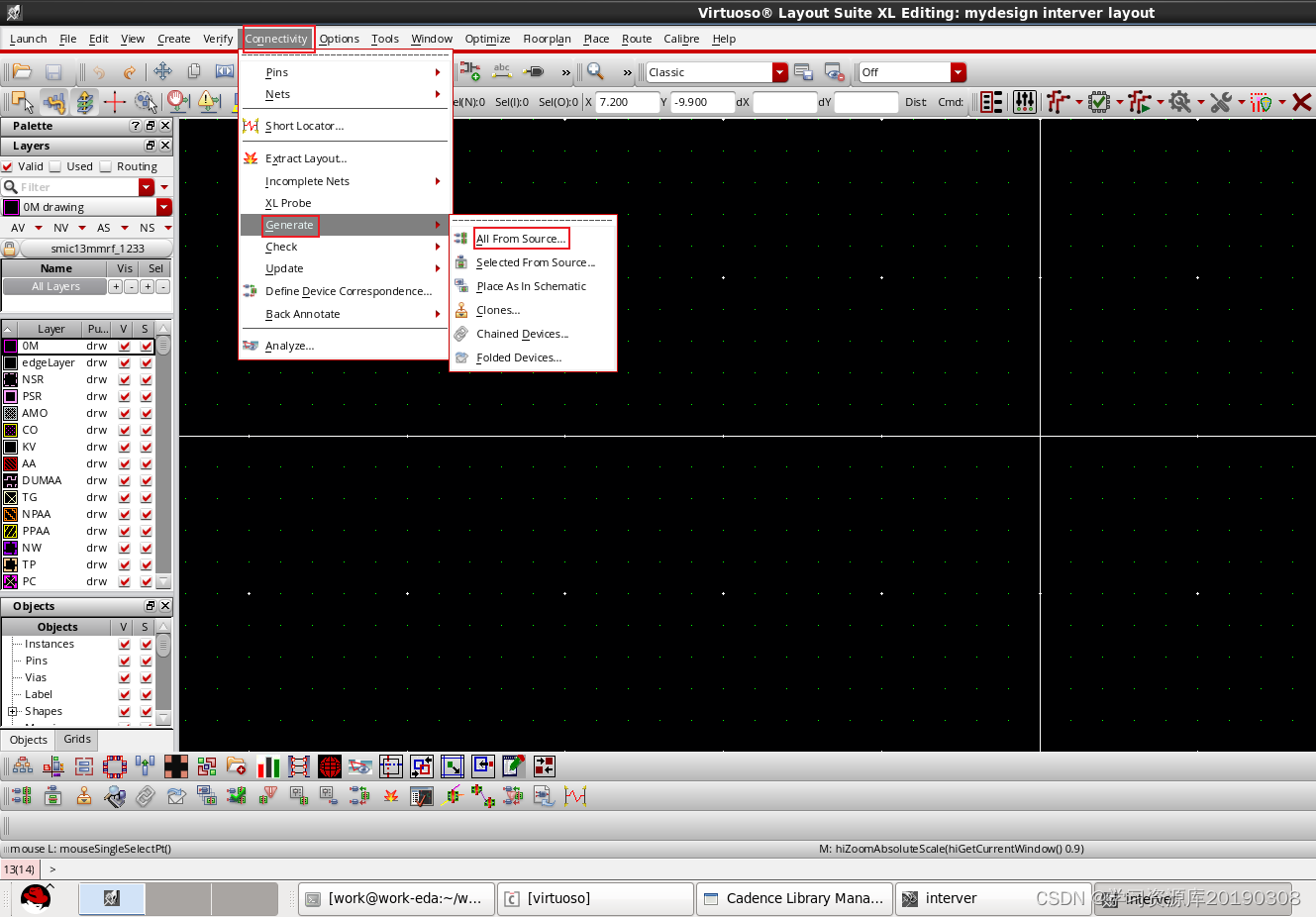

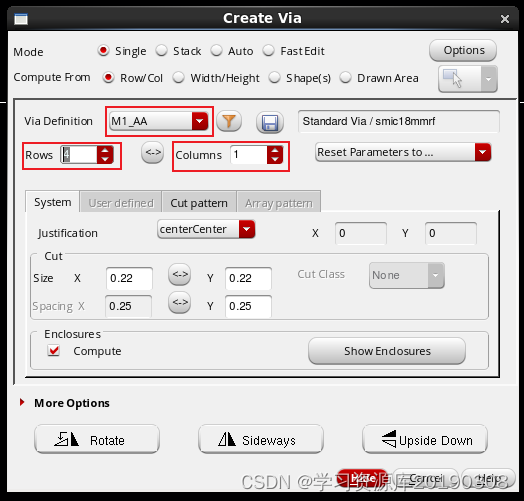

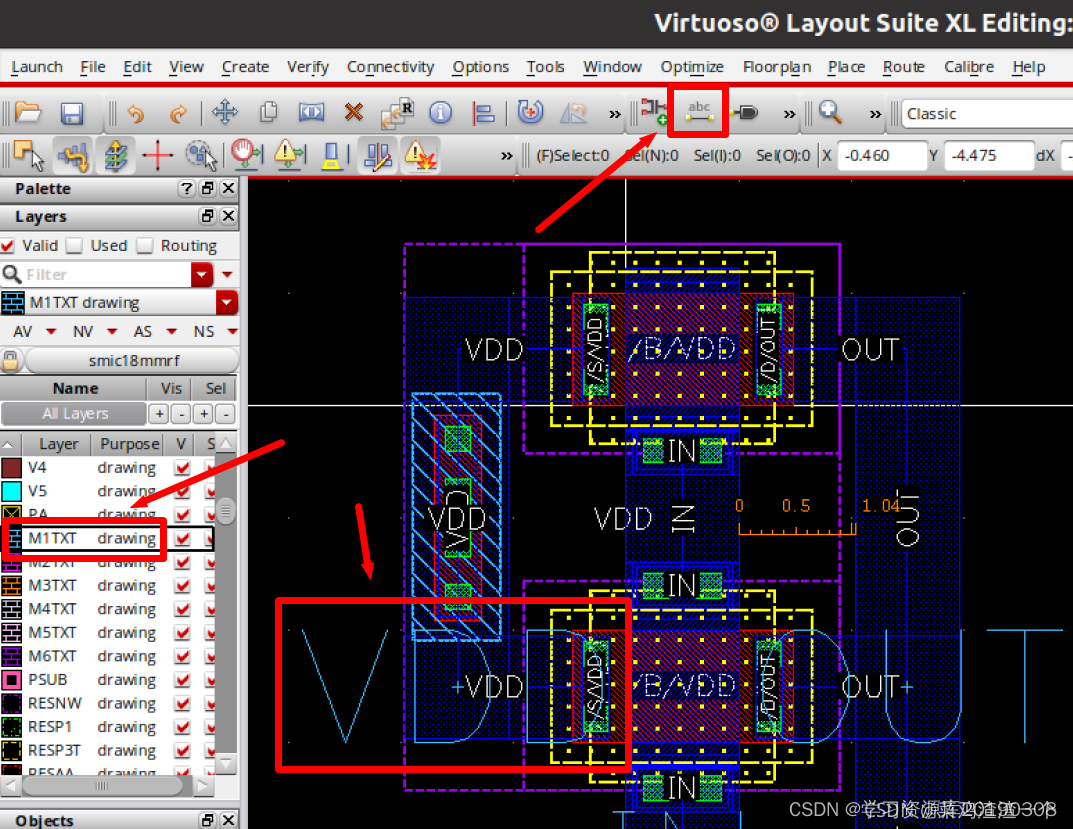

其中,p18和n18使用的库是smic18mmrf,注意绘制完电路图后将VIN、VOUT、VDD、GND设置为引脚(注意名称大写) 在画好的电路原理图中,如下图点击 如图,选择OK 弹出layout界面后。如图操作,即可导入原理图中使用器件 常用快捷键如下 按o添加过孔,M1_AA表示过孔连接M1金属层和AA有源区(active),选择一列四行 绘制出VDD的过孔

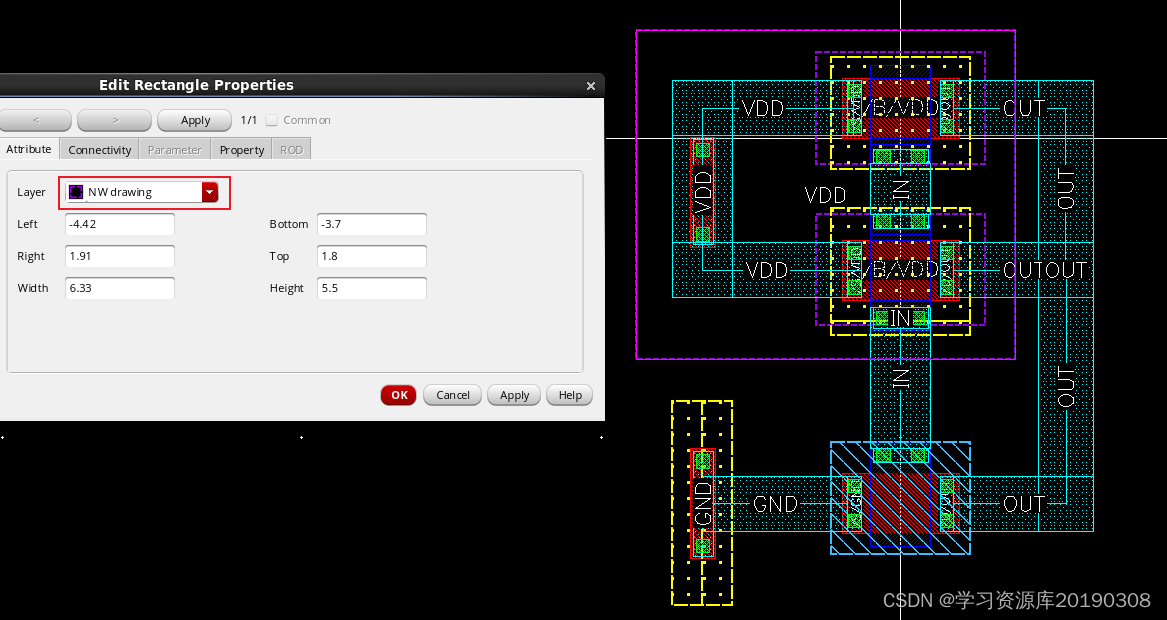

接下来进行布线,把相同名称的节点连接在一起,如图,注意,图中蓝色为M1层 因为PMOS器件需要建立在Nwell中,所以将上方的两个PMOS器件用紫色的NW drawing层覆盖

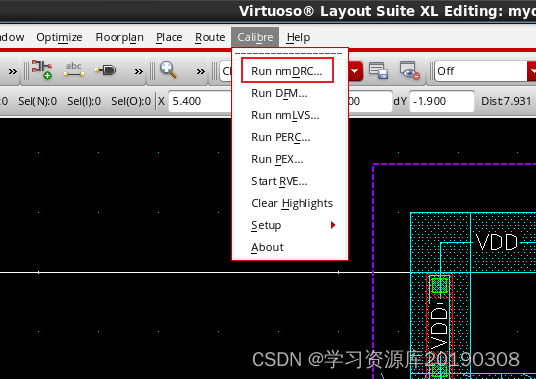

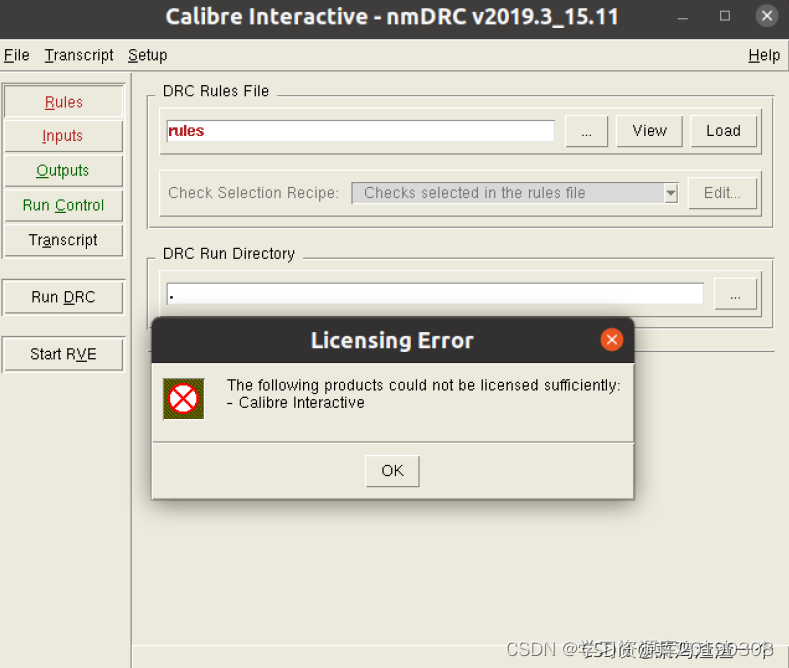

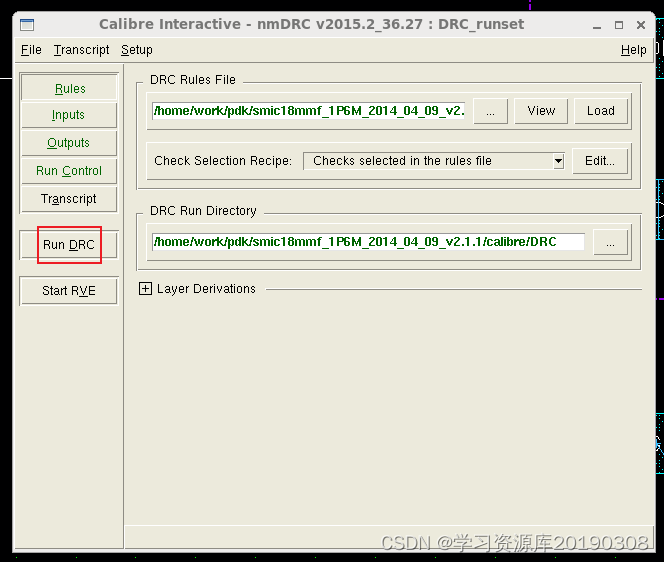

至此,版图完成 在版图界面打开DRC 注意,如果在这一步出现License的错误,如下图,请点击下方的链接,查看解决方法。 Cadence Virtuoso IC617中常见的报错和警告的解决方法 导入规则文件

然后点击RUN即可

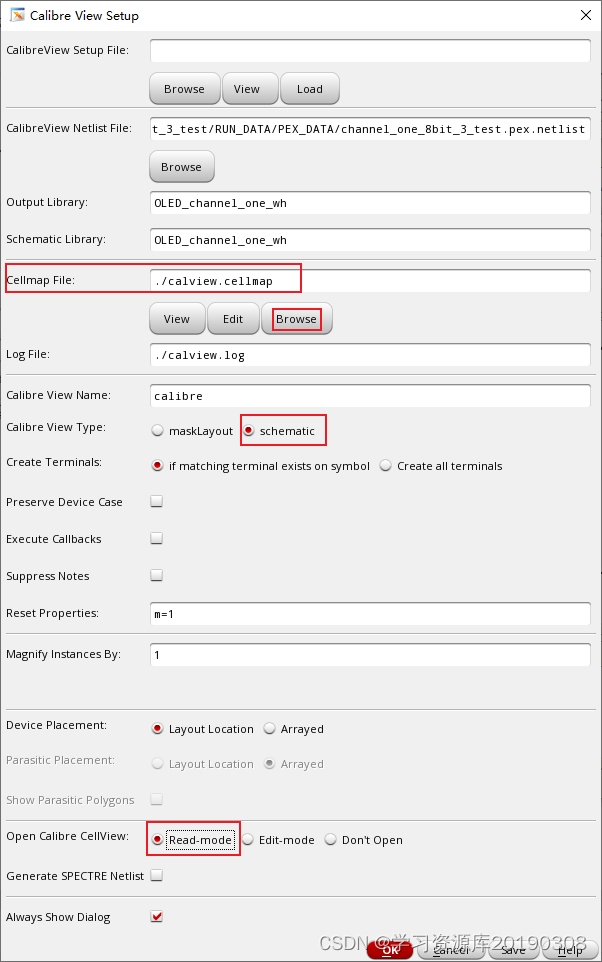

选择电源和接地 点击RUN即可 之后会跳出界面 需要选择自己的Cellmap File ,后缀为 .cellmap ,此外其它选项需改动的都在红色框标出

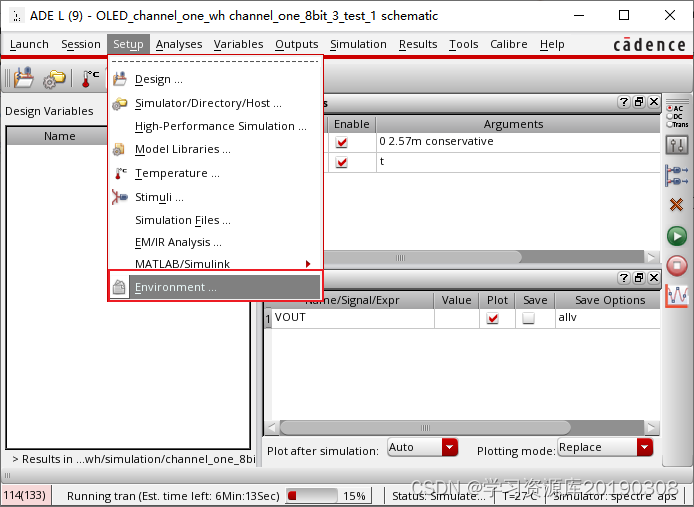

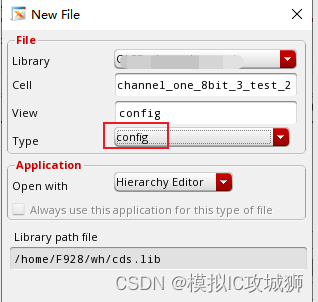

——直接使用前仿中用到的ADE L界面 选择Environment ——利用config配置后仿 (此方法需要将整体电路图封装成一个symbol,并加入输入输出激励,好处是可以分别设置各个模块是否使用前仿或者后仿,可以对某一模块单独进行后仿) 在library manager中,新建cell view 选择config 选择需要仿真的原理图,点击下方的Use Template,选择spectre,点击OK

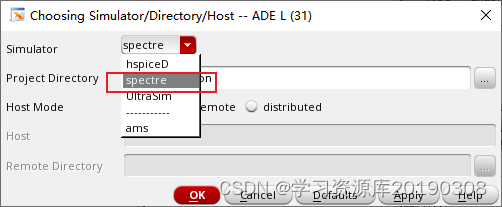

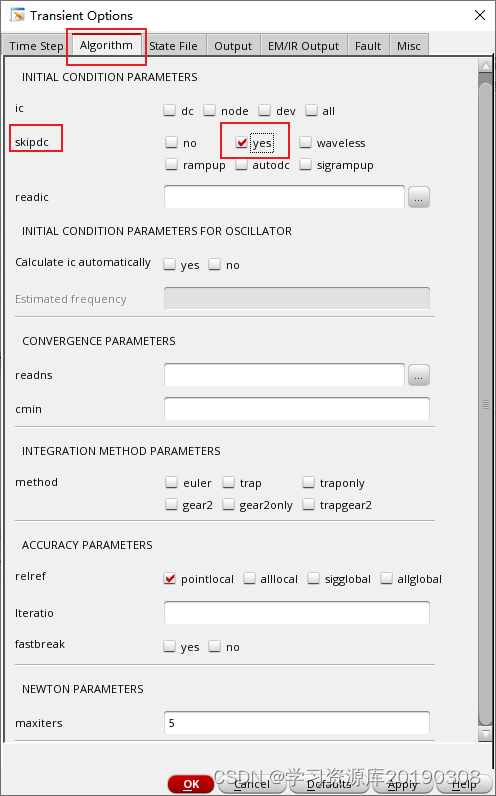

注意: 每次更改一下shematic,需要在config窗口即Virtuoso@Hierarchy Editor窗口点一下菜单栏第七个按钮—recompute the hierarchy,重新上传下数据,然后才能进行ADEL仿真,同时,注意检查下,ADEL窗口的Setup→Simulator/Directory/Host…下的Simulator选项必须要选择spectre,这个点必须注意,应为有的时候应为系统配置会默认为ams,导致仿真不能正常进行(我就遇到过,查了半天,哈哈哈) 仿真前确认是否为后仿真 方法一:在ADEL窗口,simulation→netlist→create/recreate→弹出netlist网表,下拉到最后,看是否include所加的后仿真寄生网表“/home/…/caliber/pex/SAR_ADC.pex.netlist”,如果有,则表示是后仿真,否则,需要检查是否哪一步设置有误,后仿真只能保存模块外部信号,不能保存内部信号 方法二:在ADEL窗口,simulation→Output Log→弹出log页,找到Circuit inventory即电路详细列表,可看到列表包括capacitor:36168,resistor:32623,实际电路中并没有这么多电阻电容,说明提取的仿真网表中包括寄生电容、电阻,是后仿真 如果出现cadence 后仿真不收敛的问题 ERROR (SPECTRE-16080): No DC solution found (no convergence). 解决方法:SKIP DC (跳过DC仿真) 操作: 将skip dc勾选上就可以了 (1)版图对电路进行寄生提取(pex),在路径/home/…/calibre/pex下会生成svdb文件,该文件包含提取的寄生信息,值得注意的是,多个模块的寄生提取放在同一路径下,svdb文件会覆盖,建议在/home/…/calibre/pex路径下建立不同的block来存放不同模块的寄生文件,方便调用 (2)进入电路的shematic,Calibre→Start RVE→打开Calibre RVE对话框,最上方的Database选择对应路径下该模块电路的svdb文件,比如:/home/…/calibre/pex/SAR_ADC/svdb,Database Type选择PEX,点ok→打开Calibre RVE窗口,左边的Result中选择Parasitics,双击,会显示寄生列表,选择对应的net查看对应的C+CC值即可,或者双击该net名,下方会弹出详细的寄生电阻/电容列表,进行查看,也可点对点计算寄生电阻

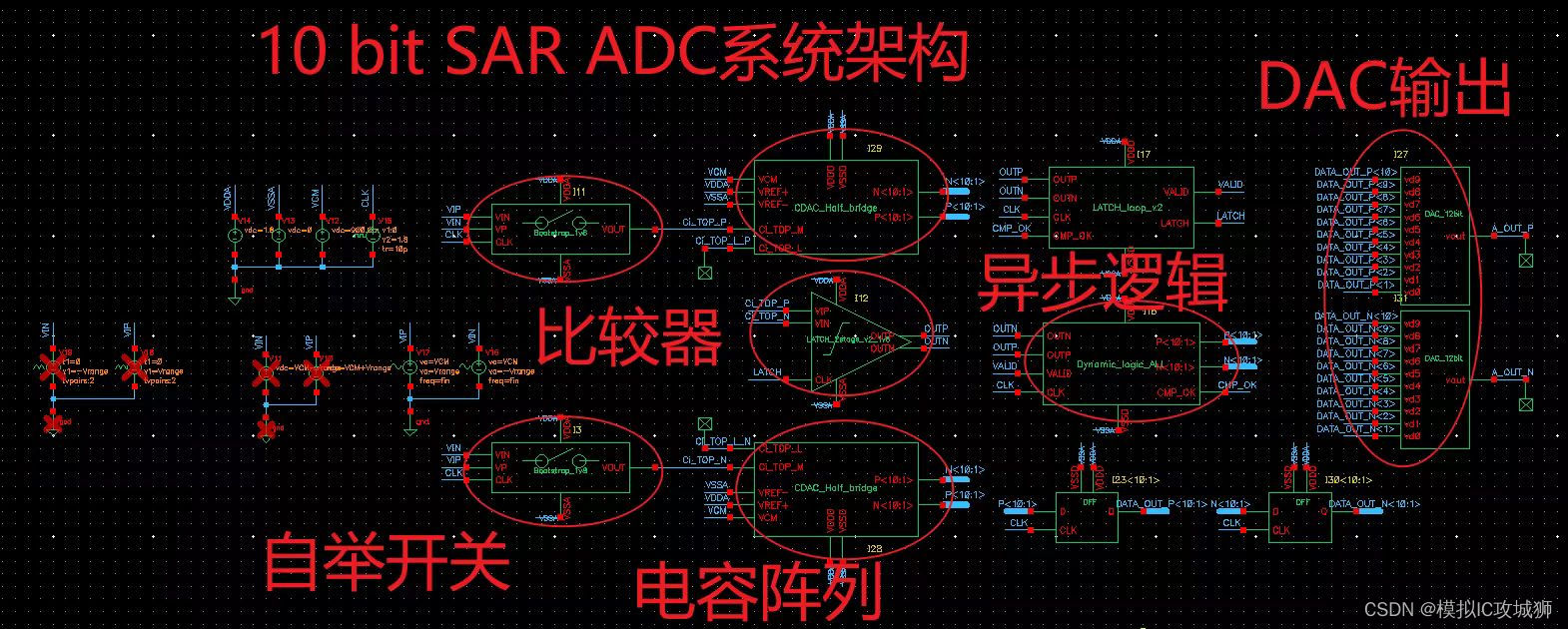

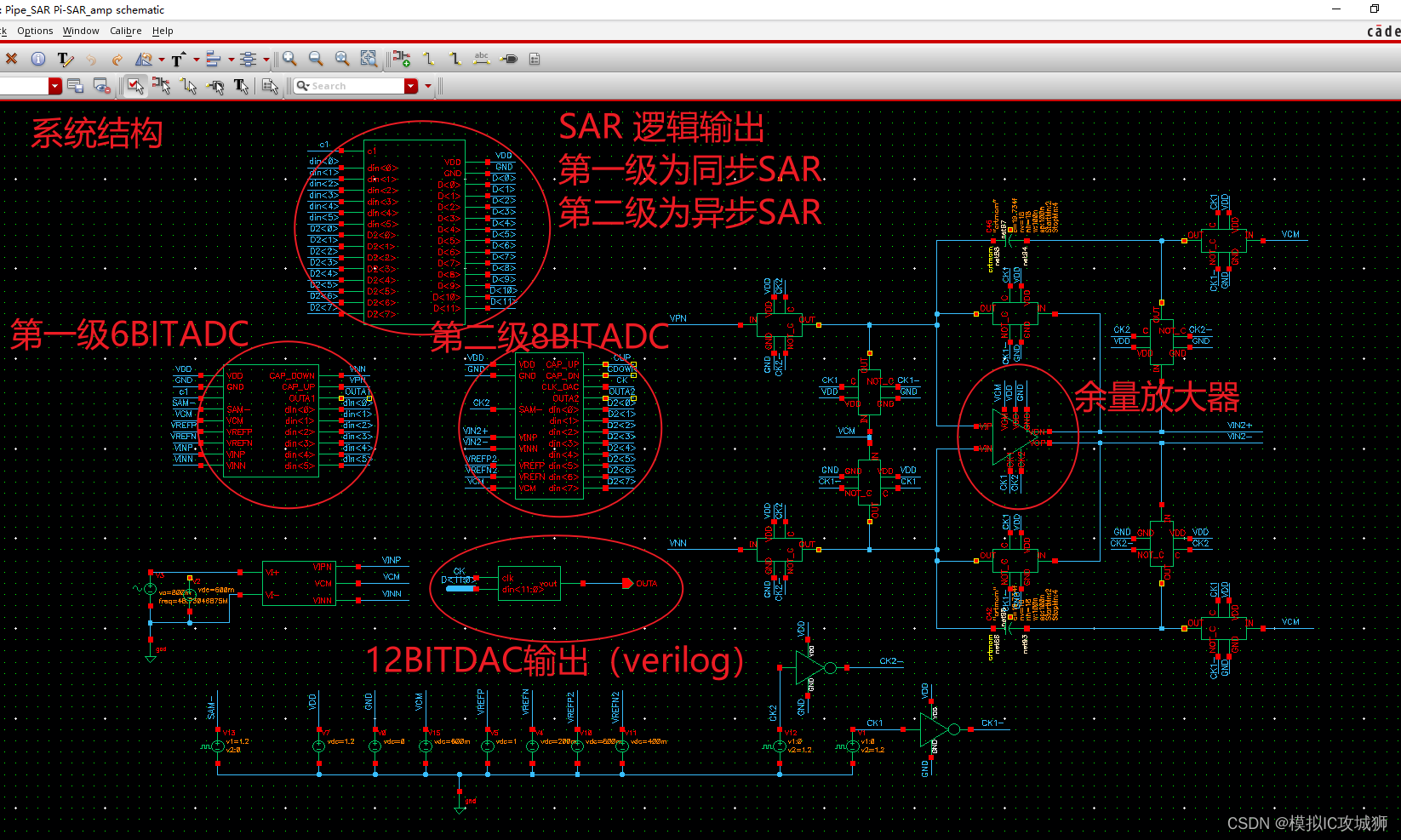

https://blog.csdn.net/qq_38496973/article/details/107901610 九、几个已经完成的SAR ADC项目几个完成的SAR ADC项目教程+Bandgap LDO+Buck DCDC项目教程 设计文档详细,适合初学者入门 SAR ADC详细介绍传送门(点这里!!!)目录 一、10bit 20MHz SAR ADC 二、12bit 100MHz Pipelined混合SAR架构 ADC 三、李福乐老师8bit SAR ADC 四、cadence入门教程 五、1.8V LDO电路 ➕1.2V bandgap电路 六、Buck DCDC项目教程 9.1、10bit 20MHz SAR ADC(WX:didadidadidida313,备注:CSDN 10bit SAR ADC)10bit SAR ADC 设计,smic18工艺,有工艺库,有效位数ENOB为9.8 常用栅压自举开关Bootstrap,Vcm_Based开关时序,上级板采样差分CDAC阵列,两级动态比较器,比较器高速异步时钟,动态sar逻辑,10位DFF输出,10位理想DAC还原做DFT。 包括详细仿真文档,原理介绍,完整电路图,仿真参数已设好,可直接使用,在自己的电脑上就可以运行仿真。适合入门SAR ADC的拿来练手 12bit 100MHz pipelined ADC 设计 65nm工艺,电源电压1.2V,ENOB=11.6 结构: 栅压自举开关 CDAC 两级动态比较器 第一级6位SAR ADC 余量放大器 第二级8位SAR ADC 同步和异步SAR logic都有 清华大学李福乐8bit SAR ADC设计 结构: 分段式电容阵列 经典两级动态比较器 工艺库+电路+设计文档; 工艺库和电路均转成OA版本,可直接导入 送李老师的课件,包含详细设计思路 有matlab代码,FFT,计算ENOB SNDR SFDR SNR THD 适合入门SAR ADC的拿来练手 |

【本文地址】

今日新闻 |

推荐新闻 |

如图,选择OK

如图,选择OK

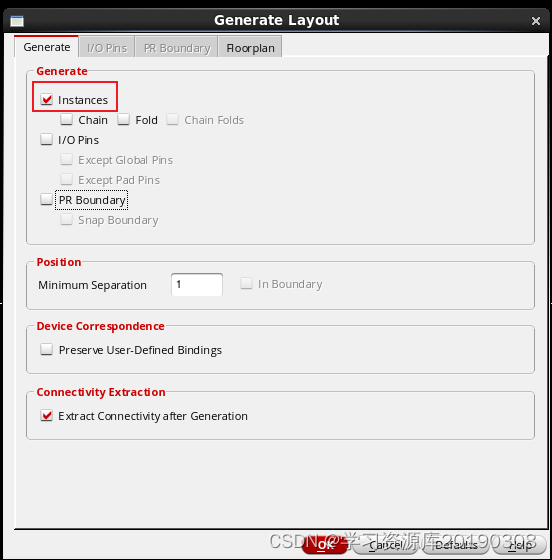

勾选Instances即可,点击OK

勾选Instances即可,点击OK

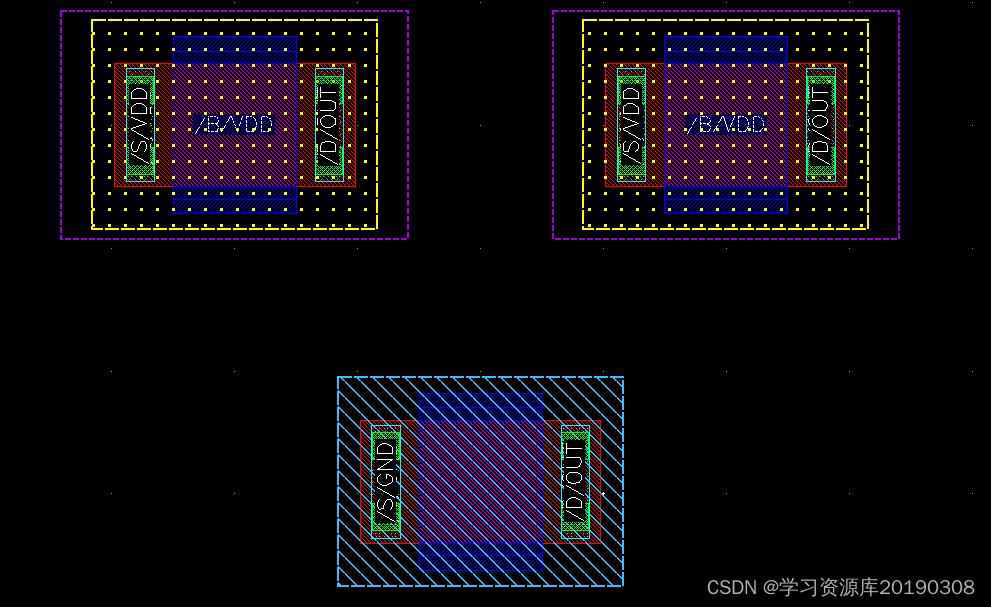

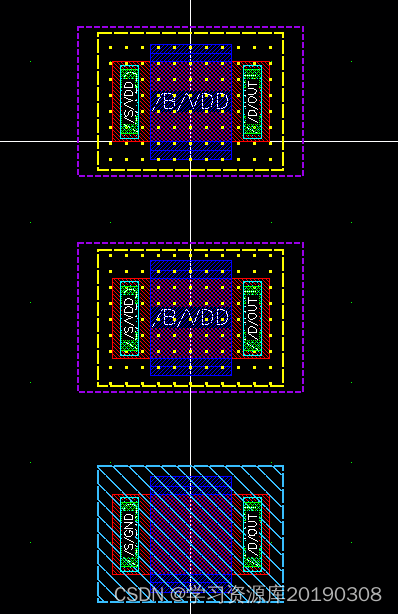

shift+F,显示器件细节

shift+F,显示器件细节

将器件移动到白色十字线附近

将器件移动到白色十字线附近

生成红框中四个过孔

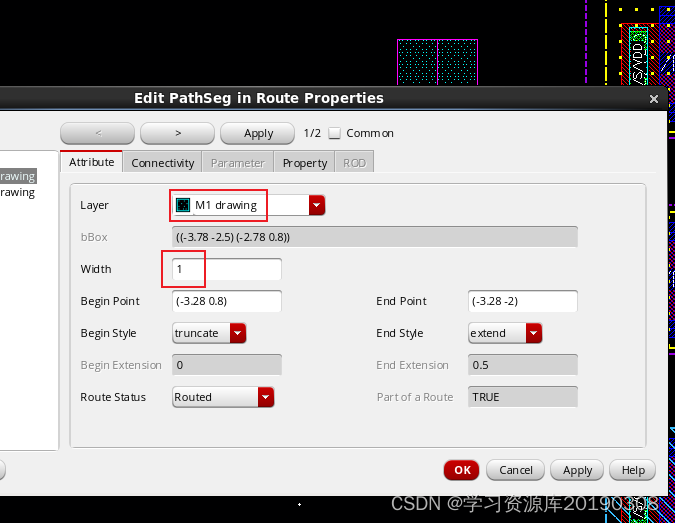

生成红框中四个过孔  给过孔覆盖金属层,按P键划线,画完之后按Q键修改宽度(注意过孔与金属层之间的间距不能太小)

给过孔覆盖金属层,按P键划线,画完之后按Q键修改宽度(注意过孔与金属层之间的间距不能太小)

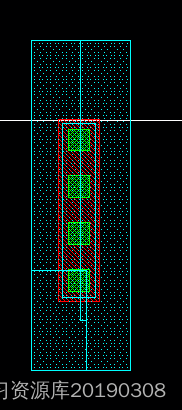

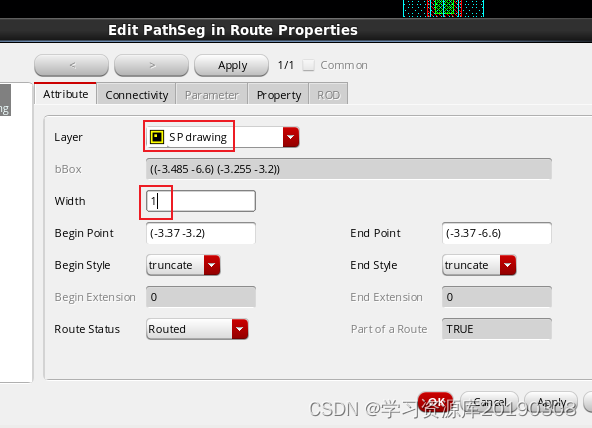

同理绘制出GND的过孔(注意GND过孔需要覆盖SP drawing)

同理绘制出GND的过孔(注意GND过孔需要覆盖SP drawing)

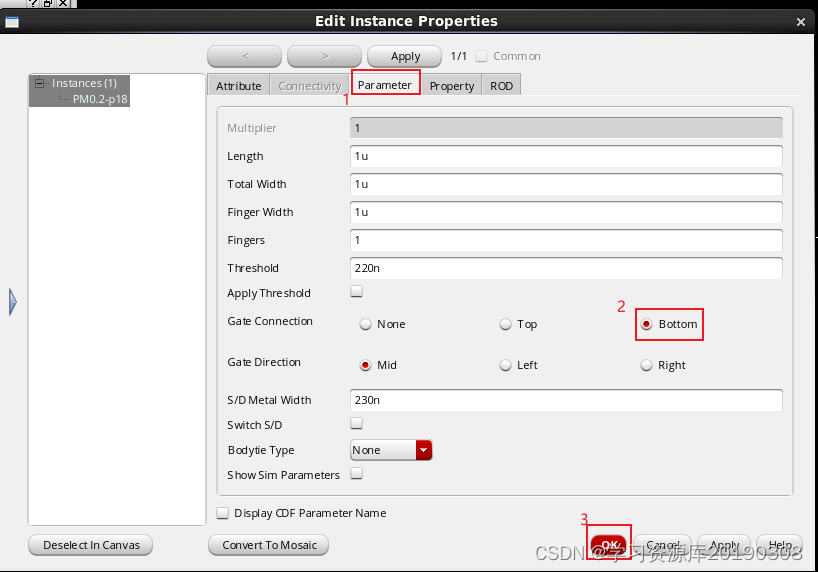

给cmos器件添加过孔,选中一个PMOS器件,按Q,然后如下图操作

给cmos器件添加过孔,选中一个PMOS器件,按Q,然后如下图操作  即可在PMOS下方生成过孔

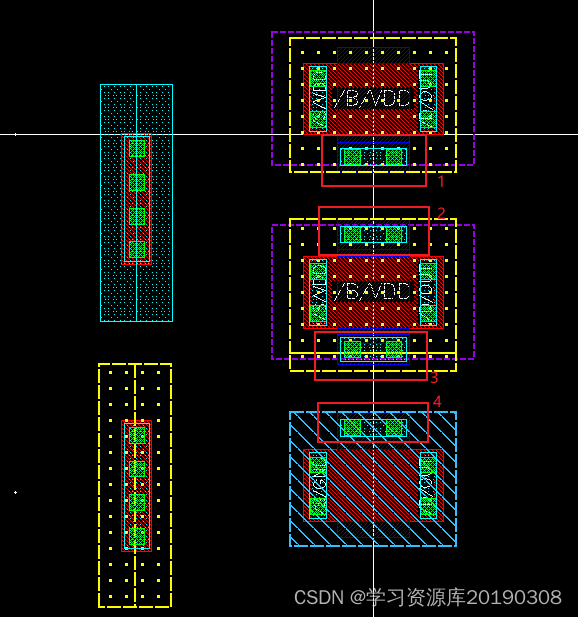

即可在PMOS下方生成过孔  同样方法绘制出1234四个过孔,其中2过孔需要自己按O键生成,方法同上

同样方法绘制出1234四个过孔,其中2过孔需要自己按O键生成,方法同上

全部变绿之后,点击 Run DRC

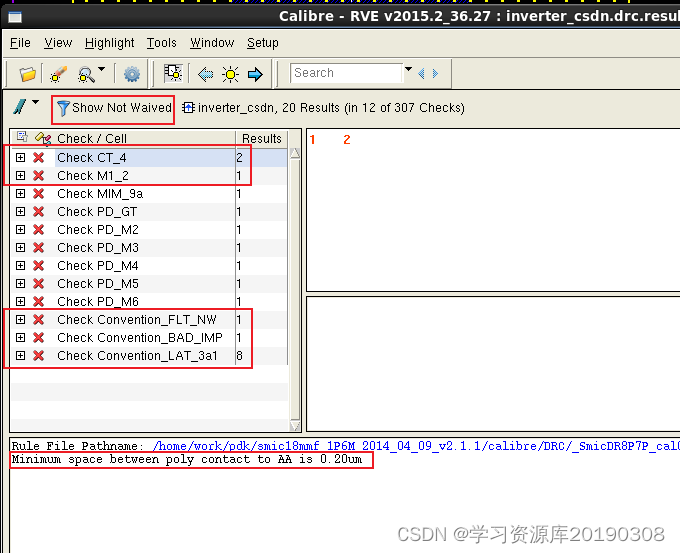

全部变绿之后,点击 Run DRC  筛选错误类型,检查版图错误并修改(密度问题不用解决,指电路密度稀疏)

筛选错误类型,检查版图错误并修改(密度问题不用解决,指电路密度稀疏)

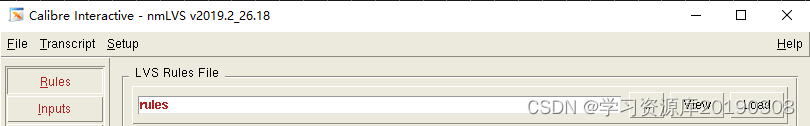

找到自己工艺库中的LVS rules_file

找到自己工艺库中的LVS rules_file  此处选择电源和地

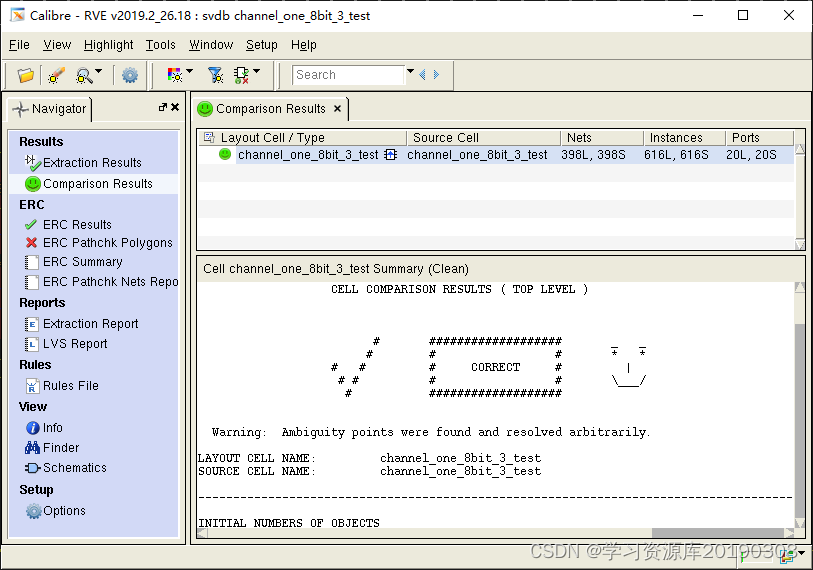

此处选择电源和地 出现笑脸说明全部连接完成,LVS检验通过

出现笑脸说明全部连接完成,LVS检验通过

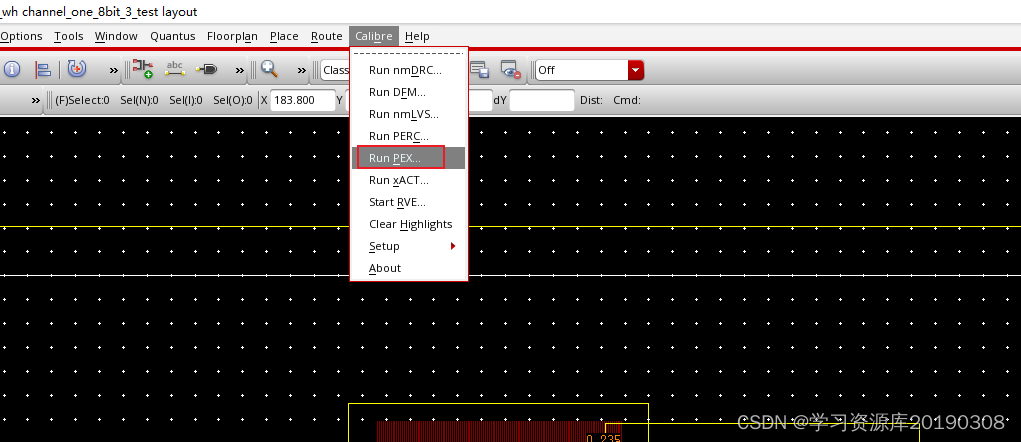

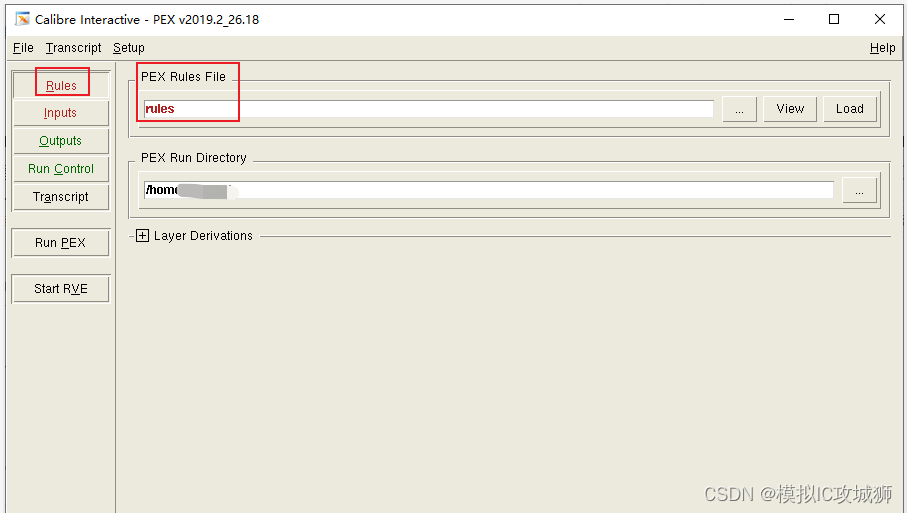

选择自己工艺库的提取寄生参数的rules_file

选择自己工艺库的提取寄生参数的rules_file

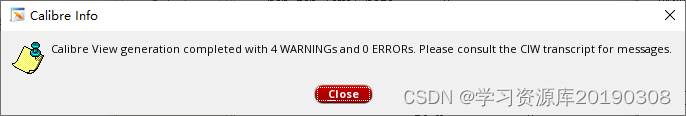

之后会跳出一个框,点击close即可

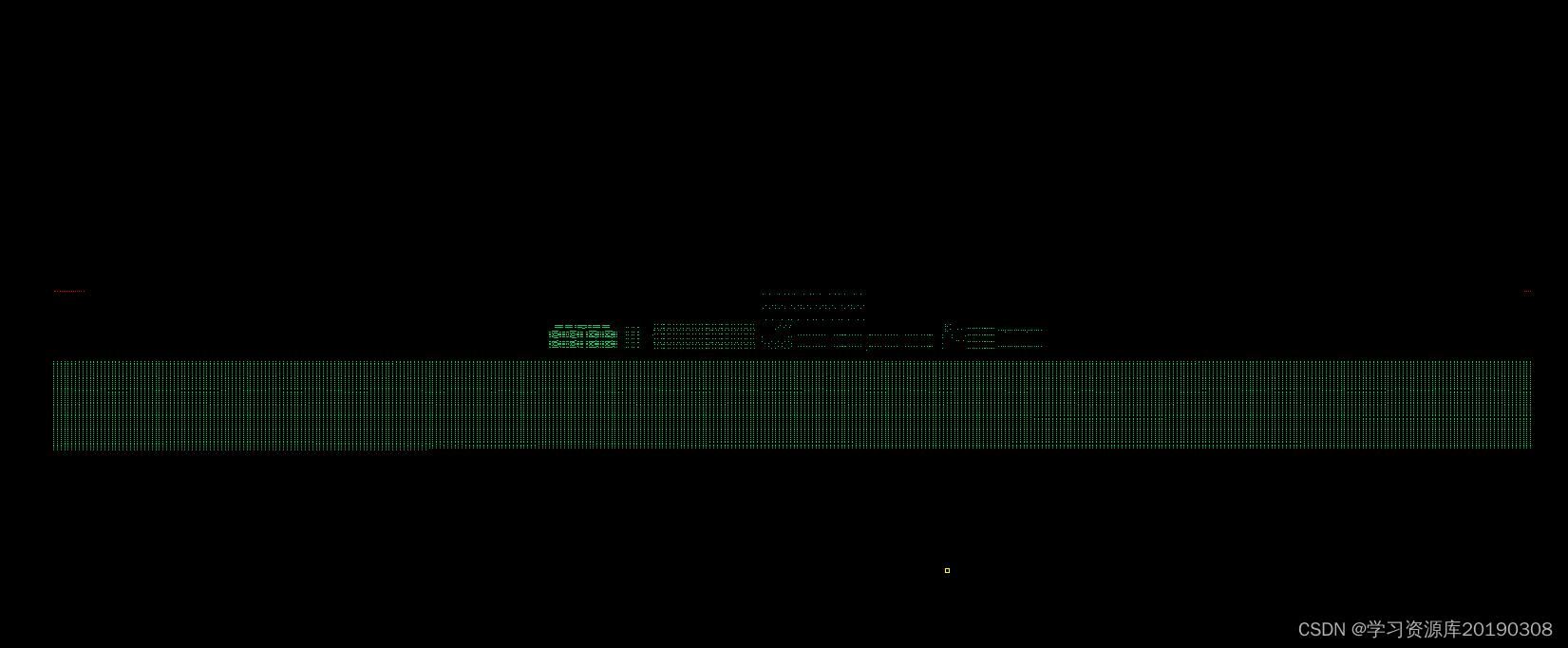

之后会跳出一个框,点击close即可  成功提取之后就会出现绿色的图

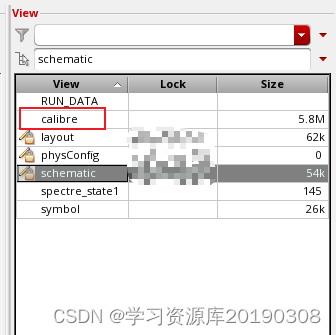

成功提取之后就会出现绿色的图  提取成功之后,在View界面中会出现calibre文件,表示提取成功

提取成功之后,在View界面中会出现calibre文件,表示提取成功

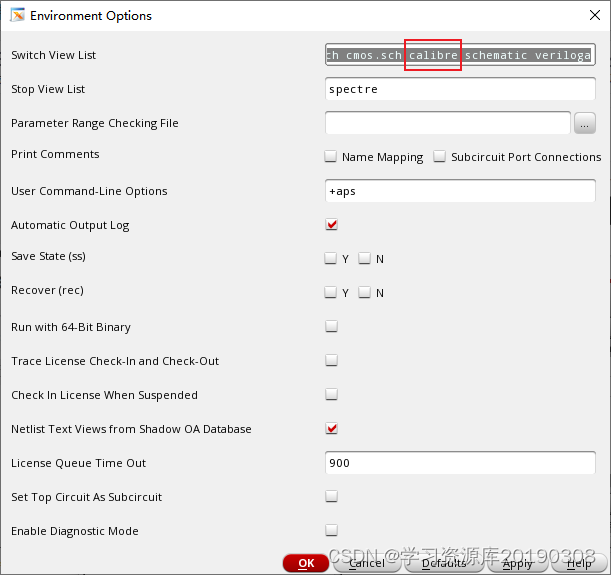

在第一行中加入calibre,点击OK

在第一行中加入calibre,点击OK  然后开始仿真即可,此时进行的就是后仿

然后开始仿真即可,此时进行的就是后仿

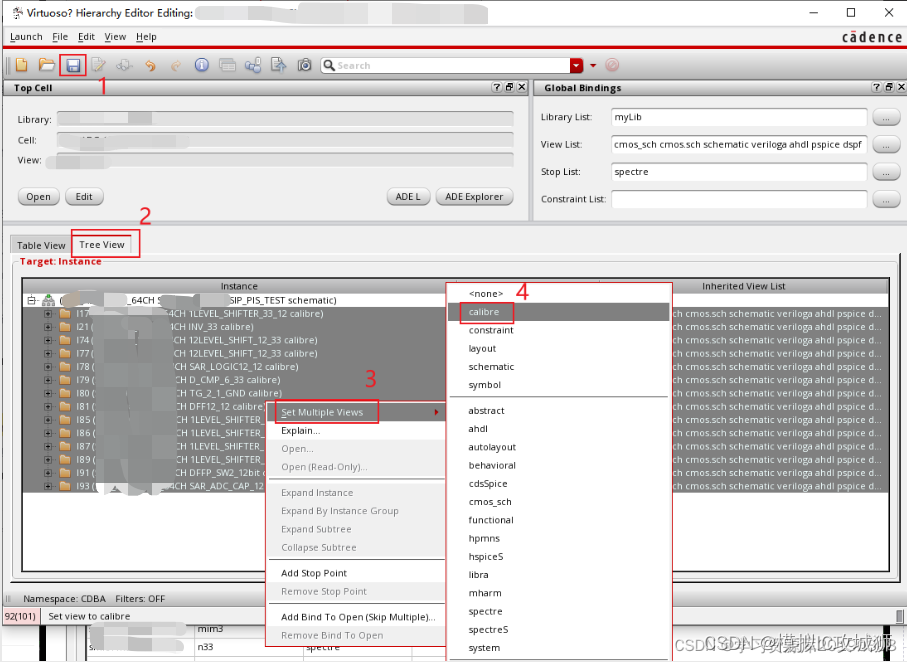

进入config界面后,设置需要进行后仿的器件,选择仿真calibre

进入config界面后,设置需要进行后仿的器件,选择仿真calibre 点击ADE L,即和前仿一样操作,无需设置Environment

点击ADE L,即和前仿一样操作,无需设置Environment