静态时序分析 |

您所在的位置:网站首页 › last和late有关系吗 › 静态时序分析 |

静态时序分析

|

文章目录

基础概念分析模式如何选取path?建立时间的OCV分析保持时间检查的OCV

基础概念

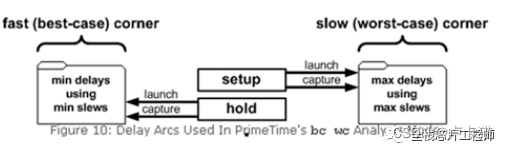

OCV(on-chip variation) 是指在同一个芯片上,由于制造工艺和环境等原因导致芯片上各部分特征不能完全一样,从而造成偏差,对时序分析造成影响。这些偏差对互连线和cell的延时都是有影响的。 由于 OCV 对时钟和数据路径的影响可能不同,时序验证可以通过使发射和捕获路径的 PVT 条件略有不同来模拟 OCV 效应。 STA 可以通过 降额(derate) 特定路径的延迟来包含 OCV 效应,也就是说,通过使这些路径更快或更慢,然后使用这些变化来验证设计的行为。单元延迟或线延迟或两者都可以降额以模拟 OCV 的影响。 time derate(时序增减因子),在芯片生产过程中,由于刻蚀,不同点的温度,金属不均匀,串扰,晶体管沟道长度等影响因素,导致片上各个位置单元延迟不一样。因此我们需要一个缩放因子来让设计更加严格。 timing derate 是计算OCV的一种简单方法,在某单一条件(BC-WC)下,把指定path的delay放大或者缩小一些,这个比率就是derate。 best-case worse-case简称BCWC mode。 需要注意的是:考虑time derate需要在某个单一条件下,比如说BC或者WC条件下,把指定path的延迟再放大或者缩小一点,要么是BC,要么是WC,不要把BC和WC混在一起,再OCV,那样太过于悲观。 分析模式静态时序分析工具提供的3种分析模式分别是: single_modeBC-WCOCV mode(AOCV, POCV)如下图,BC-WC模式下,setup check的检查都在worst-case下计算,而hold check的检查都在best-case下计算 对于setup Analysis: Launch lock : late pathData path : late pathCapture clock : early path对于hold Analysis: Launch lock : early pathData path : early pathCapture clock : late path 建立时间的OCV分析

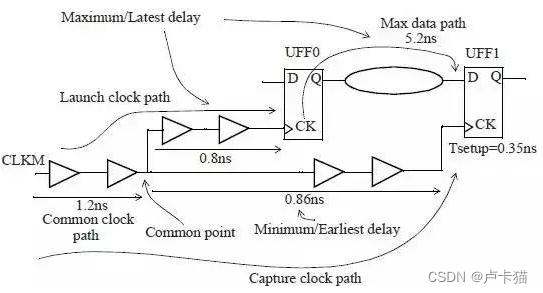

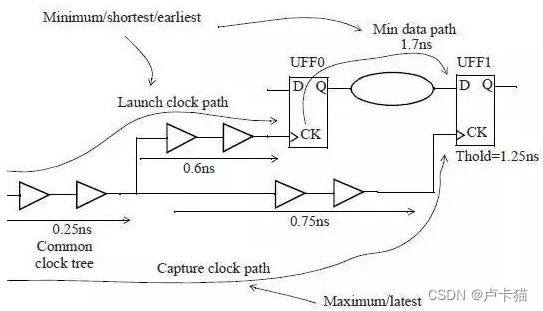

对于不同工艺,derate数值一般由实际工程经验总结而来 launch clock path = (1.2+0.8)*1.0 = 2.0 max data path = 5.2 * 1.0 =5.2 capture clock path = (1.2 + 0.86) *0.9 = 1.854 所以最小时钟周期 T = 2.0 + 5.2 -1.854 + 0.385= 5.731可以看出timing derate以后,会降低整个design的工作频率 保持时间检查的OCV如果芯片上的PVT条件不同,则当发起时钟路径和数据路径具有导致延迟最小的OCV条件(即最早的发起时钟),且保持时钟路径具有导致延迟最大的OCV条件(即最晚的捕获时钟)时,保持时间检查的最差情况就会发生。 |

【本文地址】

今日新闻 |

推荐新闻 |

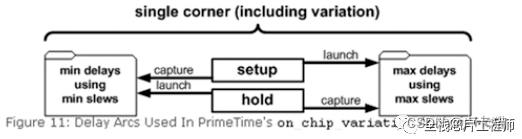

如下图,OCV模式下,setup/hold check的检查在worst-case/hold check下有交叉,具体分析流程见下面介绍。

如下图,OCV模式下,setup/hold check的检查在worst-case/hold check下有交叉,具体分析流程见下面介绍。

数据到达时间 即data path和launch clock path需要使用-late 选项,使得路径变慢 数据要求时间 即capture clock path需要使用 -early 选项,加快路径延迟 setup check一般工作在WC PVT条件下,因此不需要在late path 上,即lauch clock path以及data path上再加time derate, 因为在WC条件下,launch clock path 以及data path上的延迟已经是所有条件下最差的delay了,没有必要再加大延迟,但是WC条件下capture clock path 上的delay肯定不是最小的,因此需要加快。 所以上面的timing path做setup check,time derate只需要这样设置:

数据到达时间 即data path和launch clock path需要使用-late 选项,使得路径变慢 数据要求时间 即capture clock path需要使用 -early 选项,加快路径延迟 setup check一般工作在WC PVT条件下,因此不需要在late path 上,即lauch clock path以及data path上再加time derate, 因为在WC条件下,launch clock path 以及data path上的延迟已经是所有条件下最差的delay了,没有必要再加大延迟,但是WC条件下capture clock path 上的delay肯定不是最小的,因此需要加快。 所以上面的timing path做setup check,time derate只需要这样设置: 数据到达时间 即data path和launch clock path需要使用-early 选项,使得路径变快 数据要求时间 即capture clock path需要使用 -late选项,使得路径变慢 实际上Hold check一般在BC条件下,因此,launch clock path与data path不需要再进一步减小delay,因为已经是最小delay,但是BC条件下的capture clock path需要derate,可以使用如下设置

数据到达时间 即data path和launch clock path需要使用-early 选项,使得路径变快 数据要求时间 即capture clock path需要使用 -late选项,使得路径变慢 实际上Hold check一般在BC条件下,因此,launch clock path与data path不需要再进一步减小delay,因为已经是最小delay,但是BC条件下的capture clock path需要derate,可以使用如下设置