数电实验 |

您所在的位置:网站首页 › jk触发器输出端波形 › 数电实验 |

数电实验

|

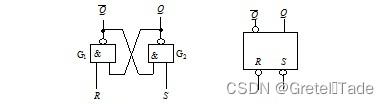

目录 触发器概述 1.基本RS触发器 2.同步触发器 (1)RS同步触发器 (2)D触发器 3.边沿触发器 (1)JK触发器 (2)T触发器 JK触发器的转换 (1)JK触发器转换为D触发器 (2)JK触发器转换为T触发器 触发器概述基本要求 有两个稳定的状态(0、1),以表示存储内容能够接收、保存和输出信号。现态和次态 现态: On触发器接收输入信号之前的状态次态: O(n+1)触发器接收输入信号之后的状态分类 按电路结构和工作特点: 基本、同步、边沿按逻辑功能分:RS、JK、D和T(T')其他: TTL和 CMOS,分立和集成下面我会一一详细讲解,并且通过Quartus II作出电路图进行仿真测试。 1.基本RS触发器基本RS触发器的触发方式: 、 或RD、SD端的输入信号直接控制。 (电平直接触发) 基本RS触发器,也有人叫它RS锁存器,用于实现“记忆”电路状态/数据功能的东西 。 样式如下:

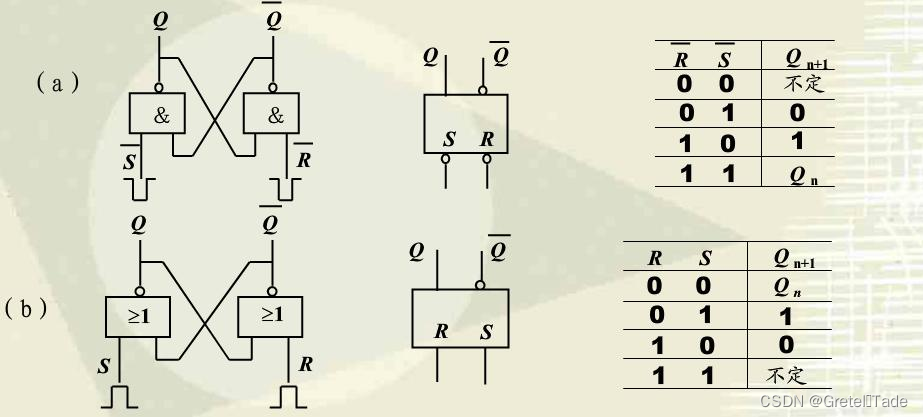

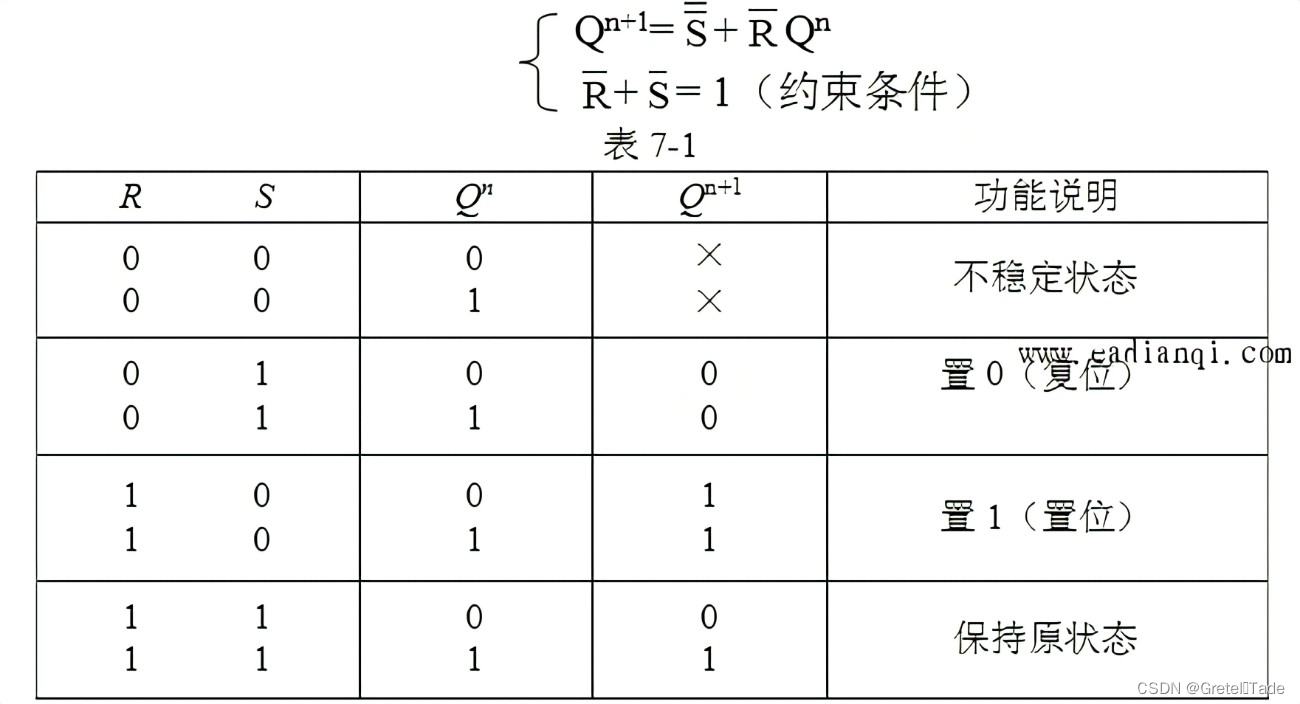

详细看此链接:https://www.zhihu.com/question/52484126/answer/551394736 RS触发器的结构与功能表:

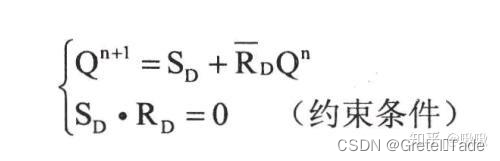

a是通过与非门来实现的,b是通过或非门去实现的,功能是一样的。 RS基本触发器的表达式:

Quartus II 作出创建block文件,作出电路图,如下所示:

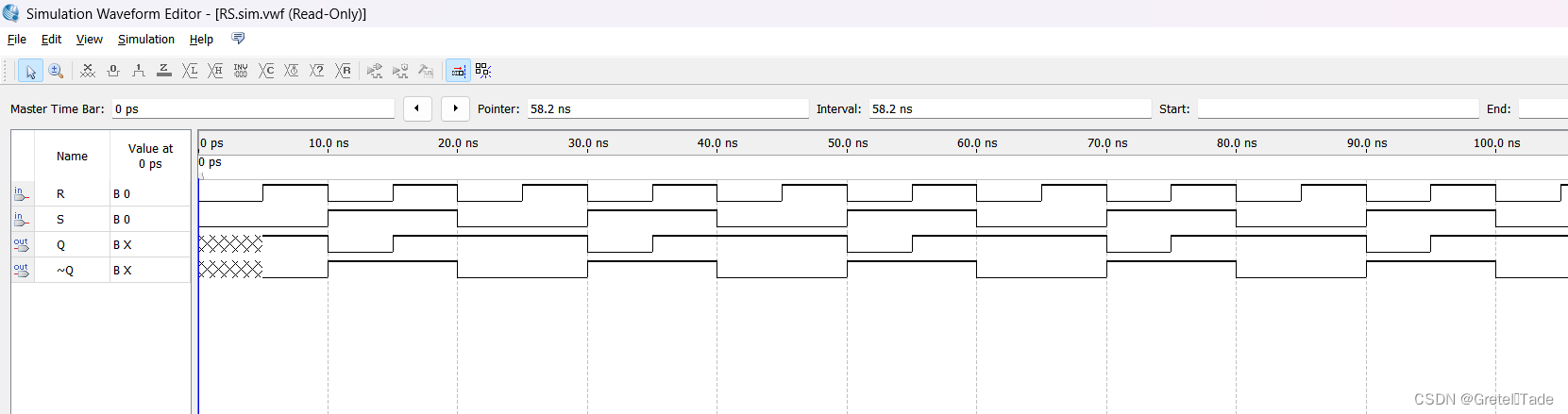

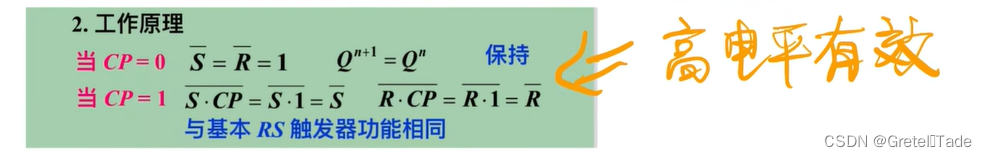

仿真结果: 我们可以去一一对比,仿真无误。 2.同步触发器同步触发器(时钟触发器或钟控触发器):具有时钟脉冲CP控制的触发器。 CP:控制时序电路工作节奏的固定频率的脉冲信号,一般是矩形波。 同步:因为触发器状态的改变与时钟脉冲同步。 (1)RS同步触发器不同于基本RS基本触发器的是,同步RS触发器多了个电平脉冲控制,比如高电平有效的时候,S和R控制开关才会有效(效果是跟RS基本触发器一样的,即功能表一样),其他情况下是不管怎么去拨都是无效的。

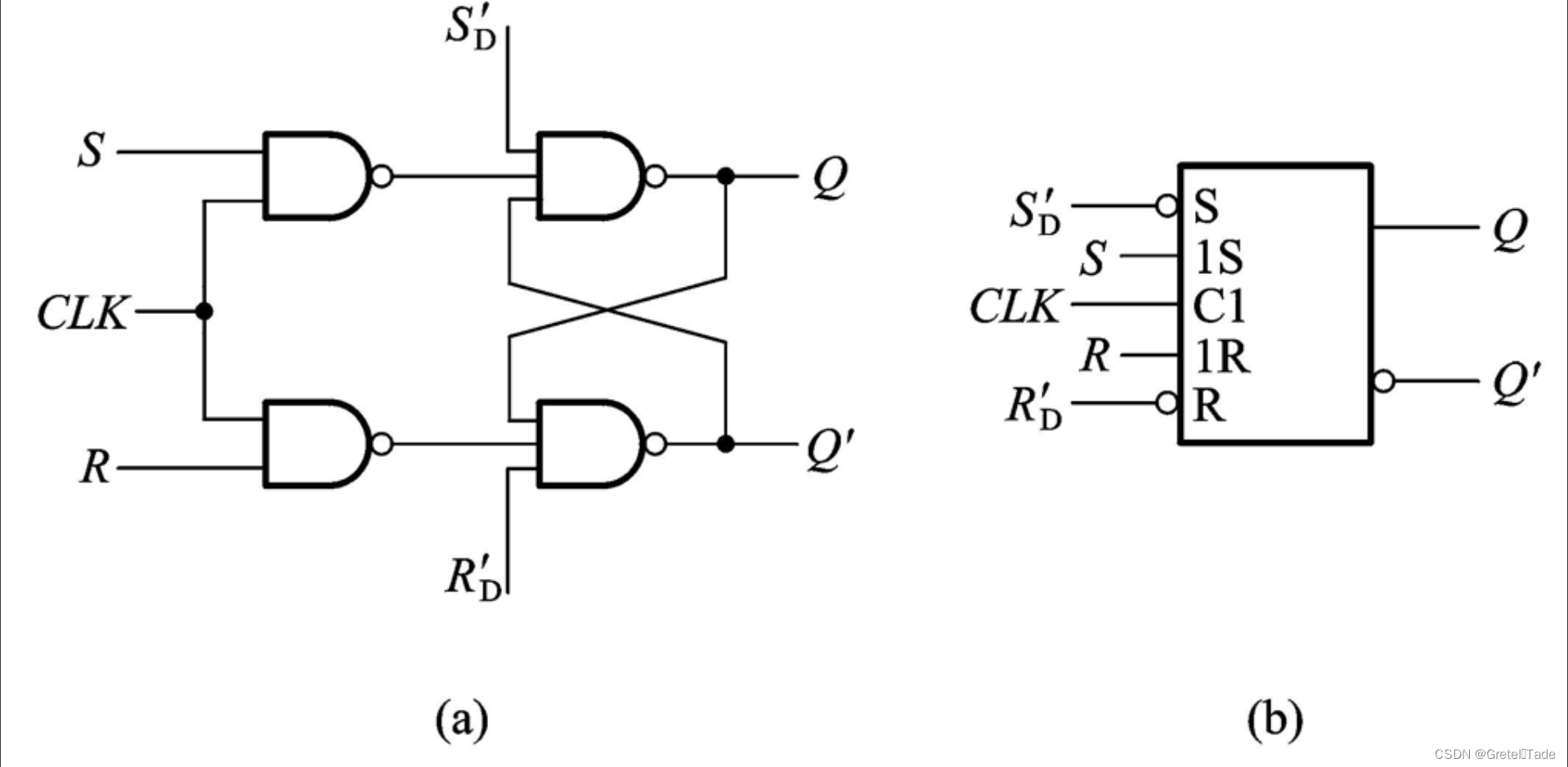

结构如下:

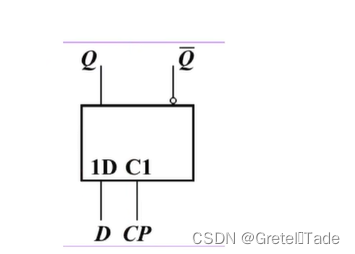

表达式和真值表如下: D触发器是一种高电平有效的触发器,D触发器很简单,也就是前面RS同步触发器把R和S连接到一起的功能就是D触发器了,其样式如下:

电路结构: 功能表如下:

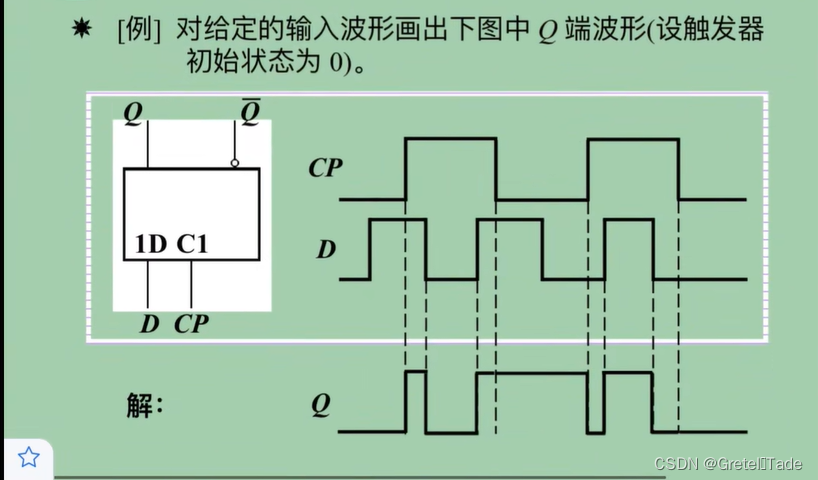

特征方程: Q(n+1) = D Q(n+1)是下一个状态 看一道例题:

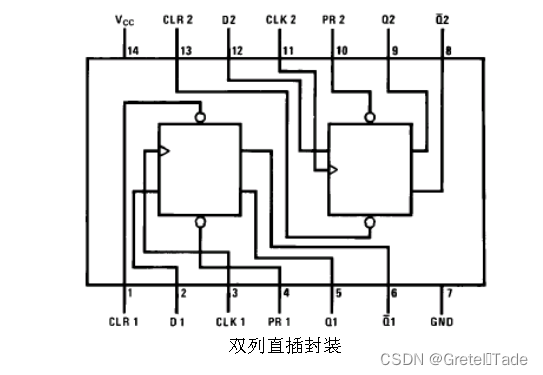

在数电实验中,D触发器的功能芯片是74LS74芯片,其管脚图如下:

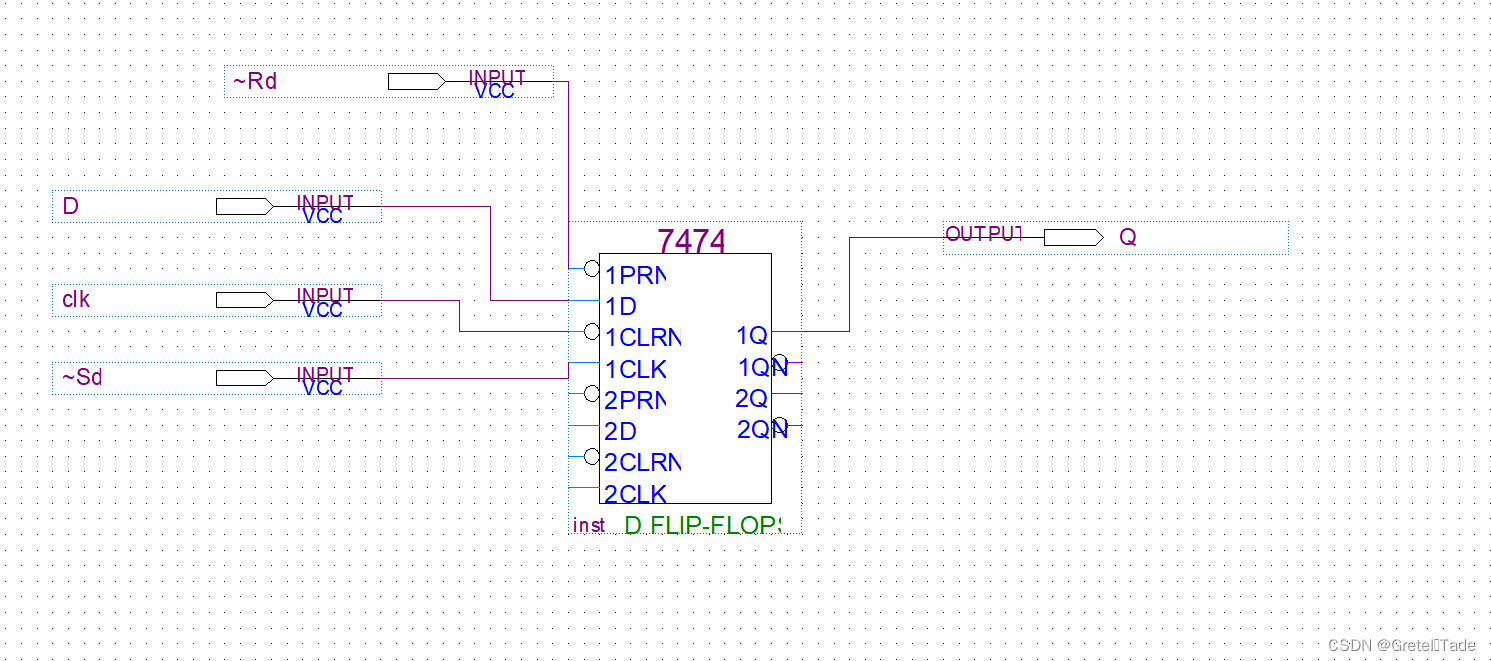

D1 是表示设置的值 CLK是表示脉冲信号 CLR1和PR是表示初始值的设定 Quartus II 作出创建block文件,作出电路图,如下所示:

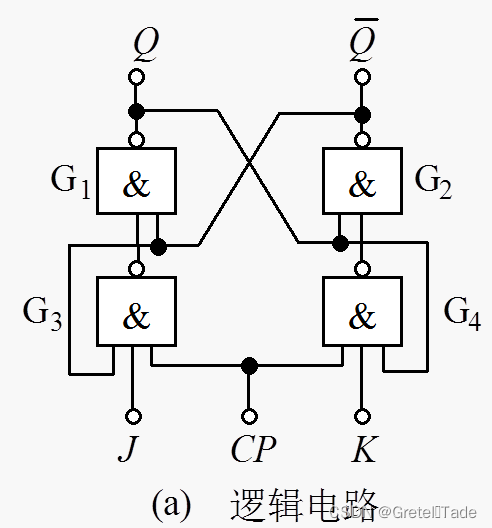

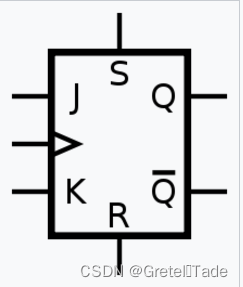

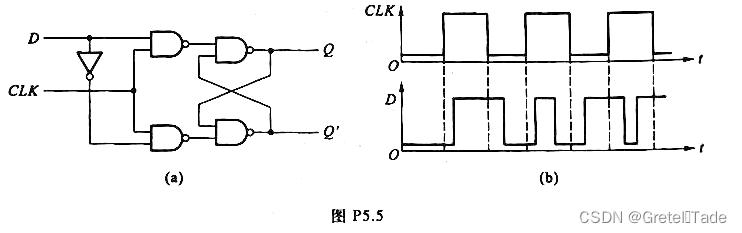

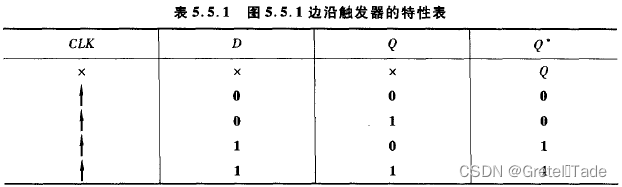

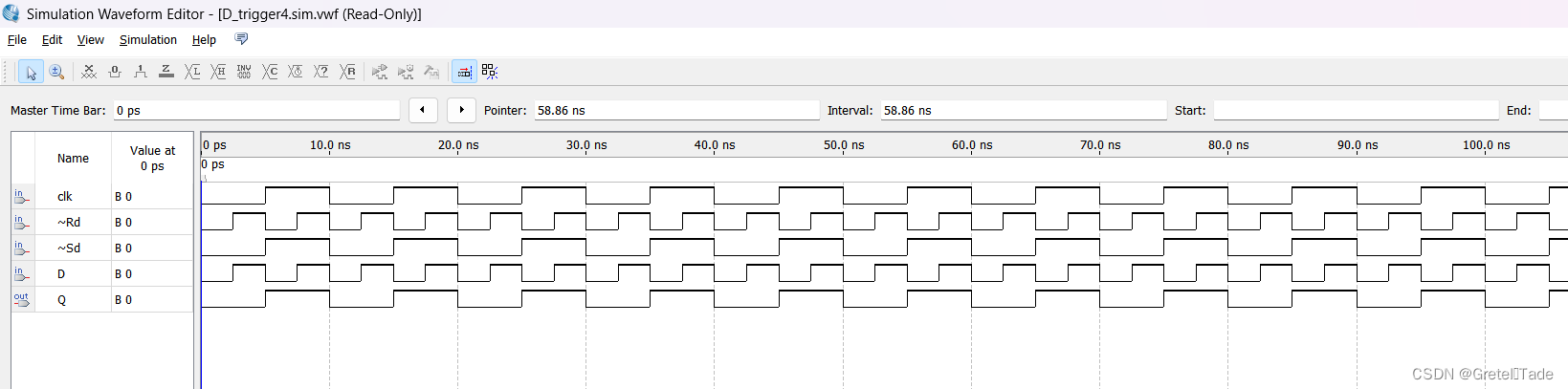

仿真结果: 存在问题: 时钟电平触发方式会出现空翻。同步触发器在CP=1期间,触发器发生两次或两次以上翻转的现象称为空翻。在数字电路中,为保证电路稳定可靠地工作,要求一个CP脉冲期间,触发器只能动作一次。 解决方法: 边沿触发器 3.边沿触发器为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于 CLK 信号下降沿(或上升沿)到达时刻输入信号的状态。而在此之前和之后输人状态的变化对触发器的次态没有影响。为实现这一设想,人们相继研制成了各种边沿触发(edge-triggered)的触发器电路。 边沿触发器分类比较多,常见的分为D边沿触发器,JK触发器,T触发器和T'触发器。这里我重点去讲的就是JK触发器和T触发器。至于D边沿触发器的相关效果跟上面的同步触发器是差不多一样的,唯一不同的是D边沿触发器在有效的脉冲信号是不会去进行空翻的。 (1)JK触发器JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能。在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。 JK触发器是一种低电平有效的触发器。 电路结构:

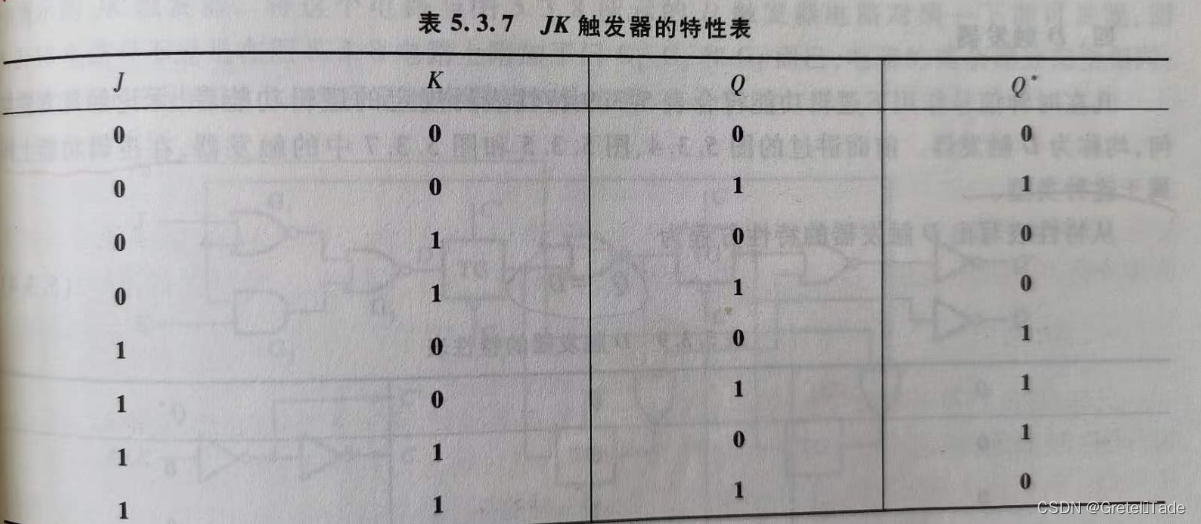

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0 。 真值表如下:

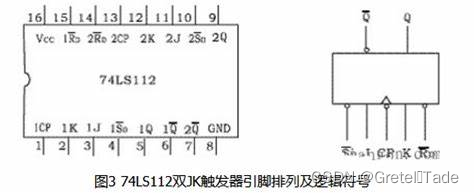

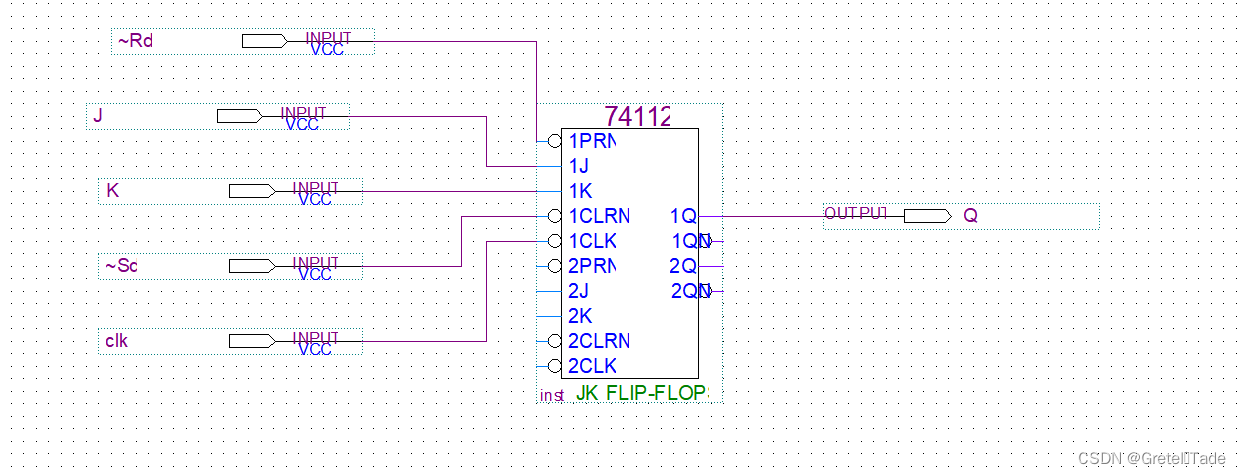

特征方程 : Q(n+1) = JQ(n)'+K'Q(n) Q(n+1)是下一个状态,Q(n)是上一个状态 在数电实验中,JK触发器的功能芯片是74LS112芯片,下面我通过Quartus II 去对其电路进行仿真测试。 管脚图如下:

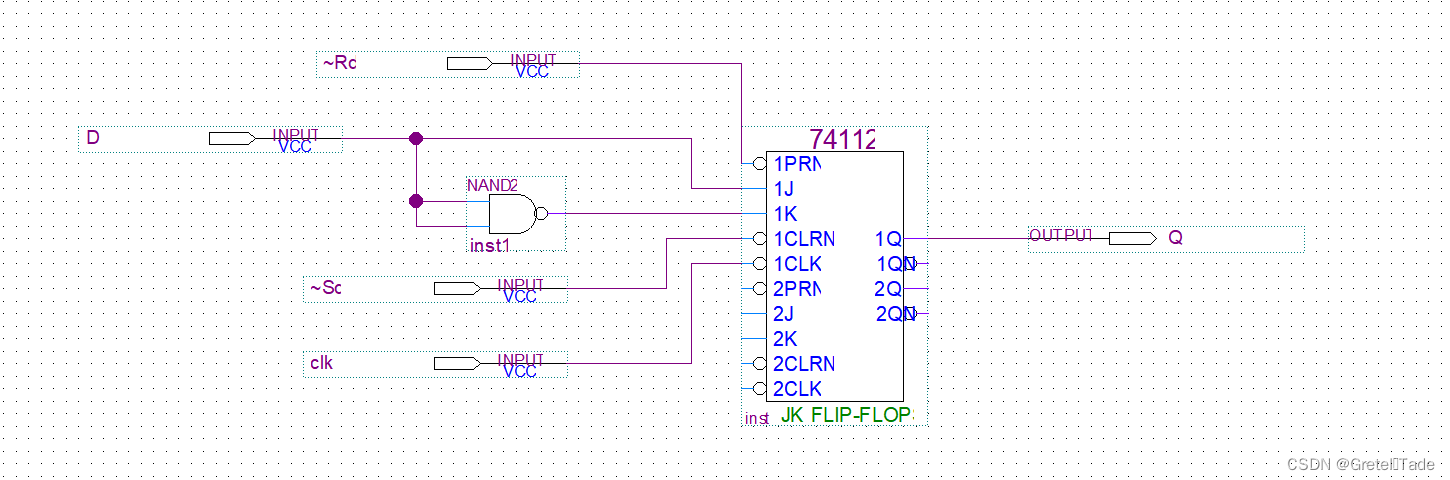

JK是表示设定的值 CLK是表示脉冲信号 ~S和~R是表示初始值的设定 Quartus II 作出创建block文件,作出电路图,如下所示:

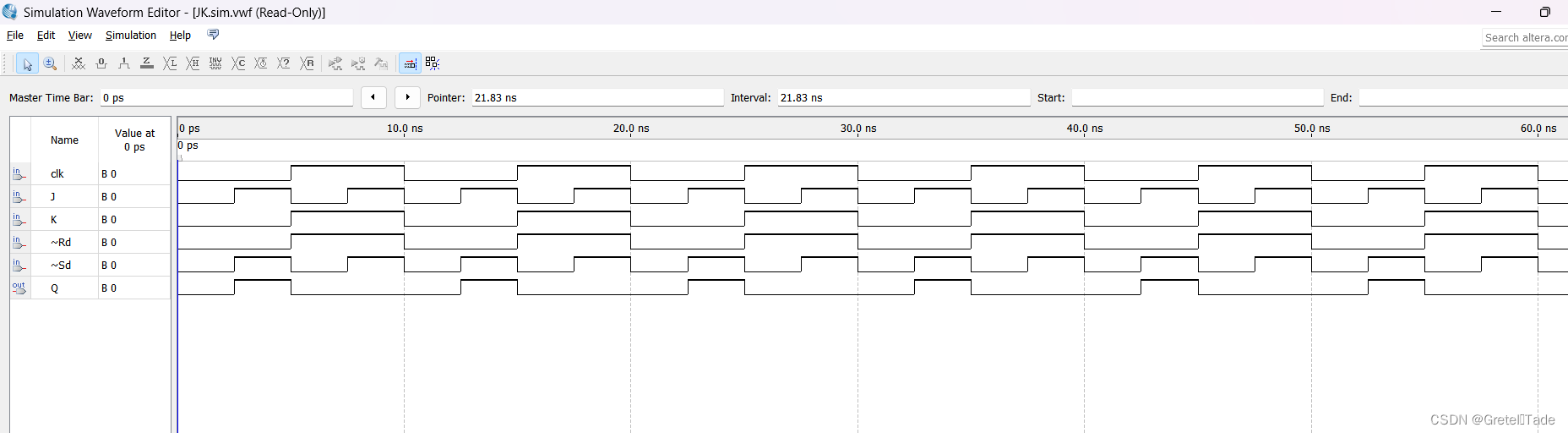

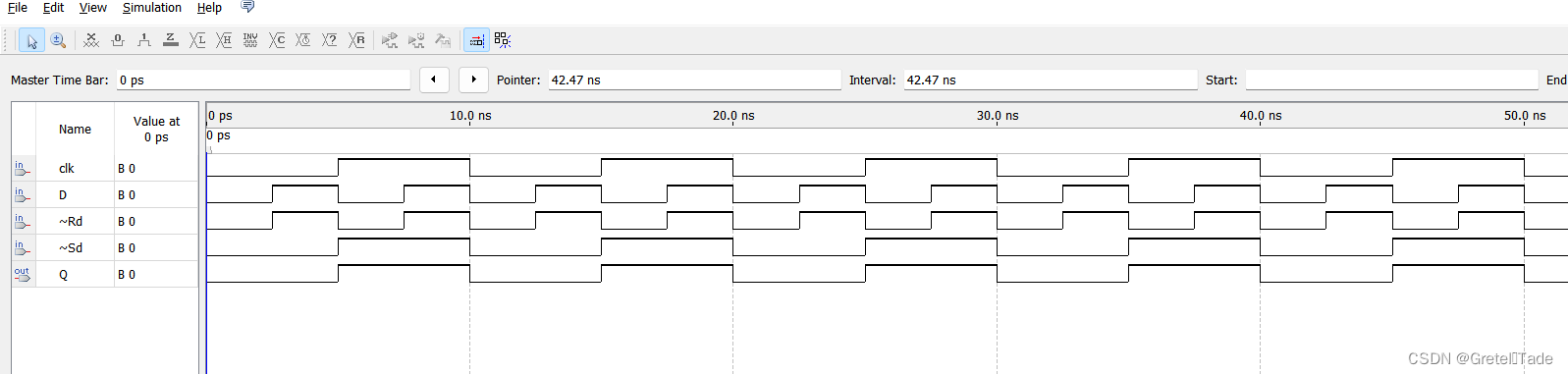

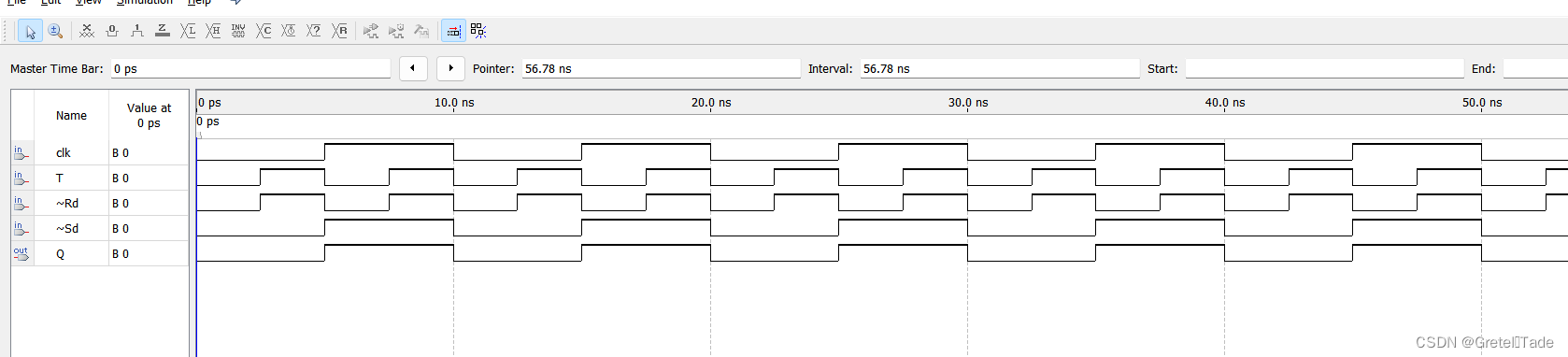

仿真结果如下:

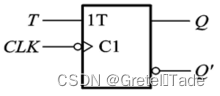

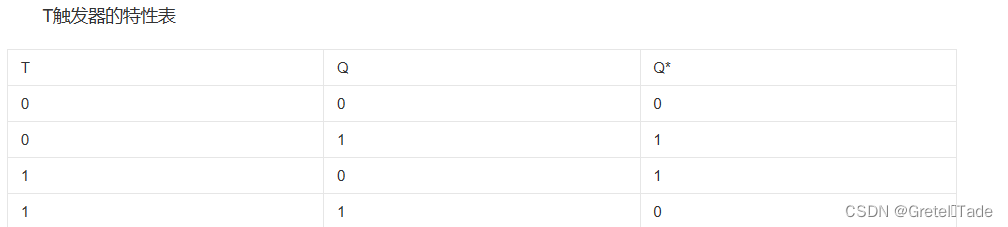

T触发器是在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的触发器,即当T=0时能保持状态不变,当T=1时一定翻转的电路。

功能表:

特征方程: Q(n+1) = T Q(n) ' +T ' Q(n) = T⊕Q(n) 其中Q(n)为现态,Q(n+1)为次态 JK触发器的转换 (1)JK触发器转换为D触发器JK触发器特征方程 : Q(n+1) = JQ(n)'+K'Q(n) 特征方程: Q(n+1) = D 其中Q(n)为现态,Q(n+1)为次态 根据上面两个触发器的特征方程,我们可以对JK触发器的特征方程去进行修改和限制,使得JK触发器的特征方程变为D触发器的特征方程,修改如下: J=D K=D' Q(n+1) = JQ(n)'+K'Q(n) = DQ(n)'+DQ(n) = D 其中Q(n)为现态,Q(n+1)为次态 Quartus II 作出创建block文件,作出电路图,如下所示:

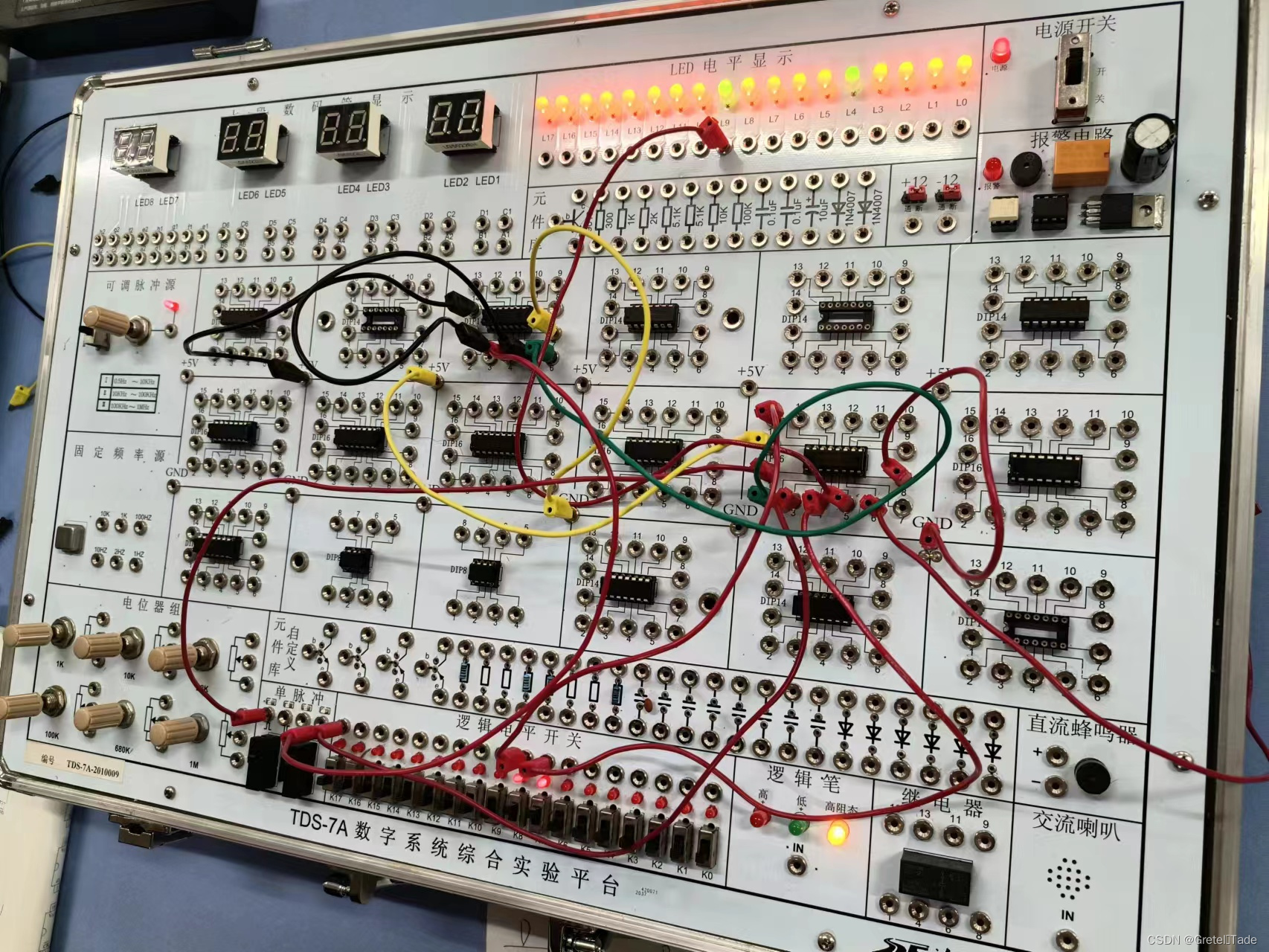

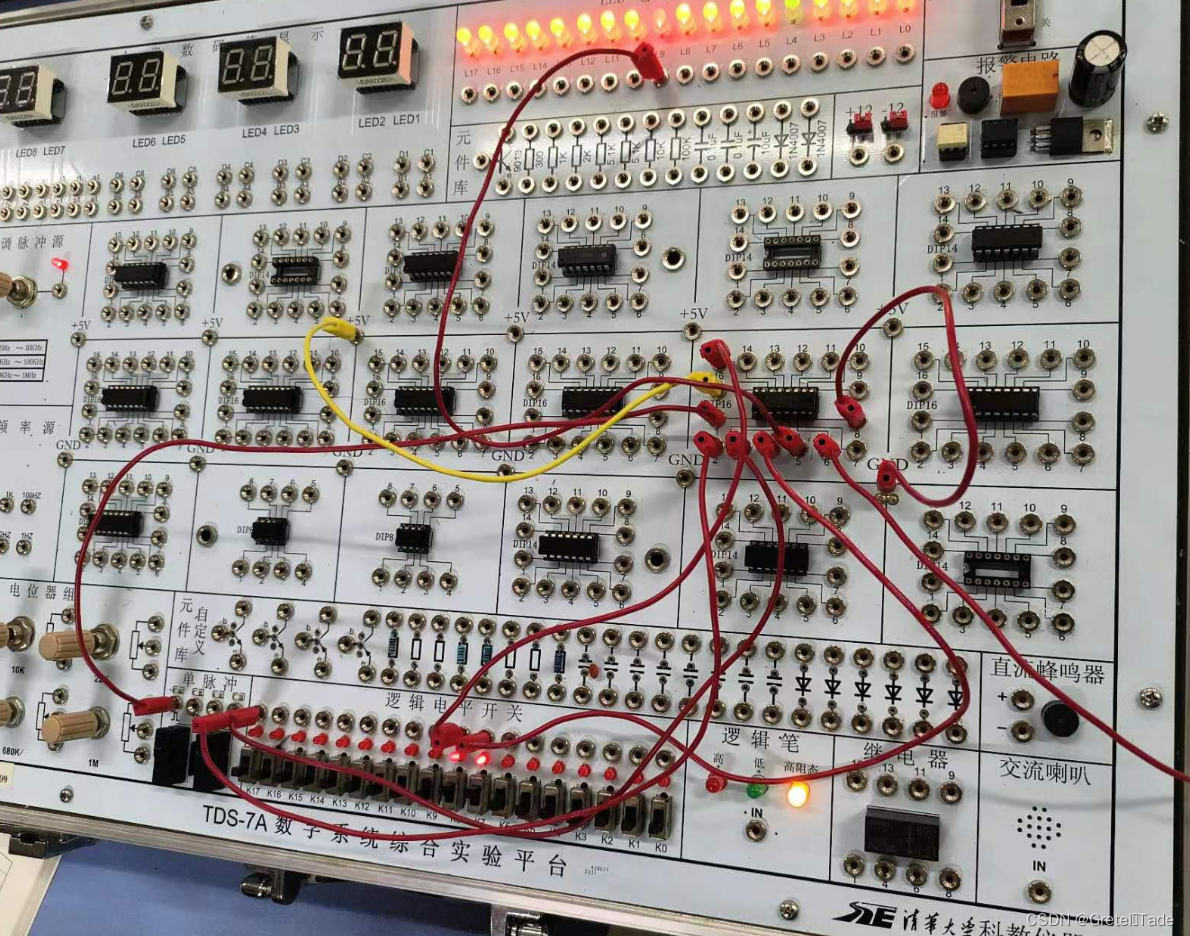

仿真结果如下: 实际电路板的连接图:

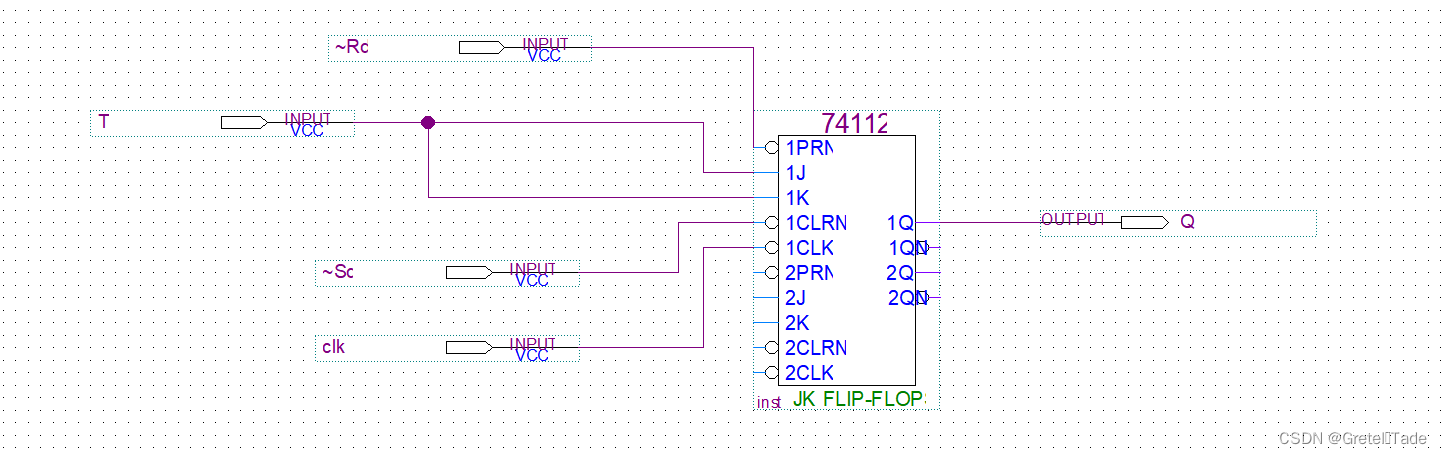

JK触发器特征方程 : Q(n+1) = JQ(n)'+K'Q(n) T触发器特征方程: Q(n+1) = T Q(n) ' +T ' Q(n) = T⊕Q(n) 其中Q(n)为现态,Q(n+1)为次态 根据上面两个触发器的特征方程,我们可以对JK触发器的特征方程去进行修改和限制,使得JK触发器的特征方程变为T触发器的特征方程,修改如下: J=K=T Q(n+1) = JQ(n)'+K'Q(n) = TQ(n)'+T'Q(n) = T⊕Q(n) 其中Q(n)为现态,Q(n+1)为次态 Quartus II 作出创建block文件,作出电路图,如下所示: 仿真结果如下:

电路板连接图:

以上就是本次实验的内容,喜欢的给个关注吧! 分享一张壁纸: |

【本文地址】

其实对于D触发器一直都会出现相关的问题。

其实对于D触发器一直都会出现相关的问题。