常用通信接口电气特征(七):LVDS |

您所在的位置:网站首页 › i2c的时钟是单向还是双向 › 常用通信接口电气特征(七):LVDS |

常用通信接口电气特征(七):LVDS

|

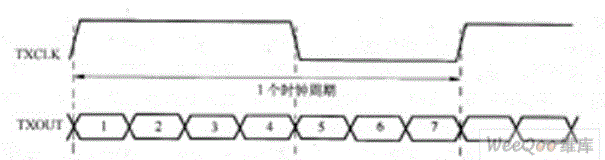

LVDS ( Low-Voltage Differential Signaling),即低电压差分信号,属于平衡传输信号,低功耗—低误码率—低串扰—低抖动—低辐射。在高速系统内部、系统背板互连和电缆传输应用中,驱动器、接收器、收发器、并串转换器/串并转换器以及其他LVDS器件的应用正日益广泛。 LVDS接口是LCD Panel通用的接口标准,大多用在7寸以上尺寸的显示屏上。以8-bit Panel为例,包括5组传输线,其中4组是数据线,代表Tx0+/Tx0-… Tx3+/Tx3-。还有一组是时钟信号,代表TxC+/TxC-。相应的在Panel一端有5组接收线。如果是6-bit Panel则只有3组数据线和一组时钟线。一般14PIN、20PIN、30PIN为LVDS接口。 在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出驱动电路(LVDS发送器),和液晶面板侧的LVDS输入接口电路(LVDS 接收器)。在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟都采用差分信号对的形式进行传输,所谓信号对,只是LVDS接口电路中,每一个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。  五通道LVDS发送芯片(DS90C385)包含了四个数据信号(其中包括RGB,数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。五通道LVDS发送芯片主要用于驱动8bit液晶面板;十通道LVDS发送芯片(DS90C387)包含八个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和两个时钟信号发送通道。十通道LVDS发送芯片主要用于驱动8bit液晶面板。 LVDS发送芯片在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不是常见的8bit数据。 五通道LVDS发送芯片(DS90C385)包含了四个数据信号(其中包括RGB,数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。五通道LVDS发送芯片主要用于驱动8bit液晶面板;十通道LVDS发送芯片(DS90C387)包含八个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和两个时钟信号发送通道。十通道LVDS发送芯片主要用于驱动8bit液晶面板。 LVDS发送芯片在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不是常见的8bit数据。  在LCD液晶屏中,需要输出到显示屏的信号是并行的图像信号和控制信号,而LVDS信号是串行传输的,所以在发送端需要将并行数据转换为串行数据。以8bit RGB显示屏接口为例,每个显示周期需要传输8bit的R信号,8bit的G 信号,8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。而每对LVDS信号线在一个TX周期里只能传输7BIT数据,所以需要4 对数据线,外加一对时钟线。LVDS并串转换如下图所示: 在LCD液晶屏中,需要输出到显示屏的信号是并行的图像信号和控制信号,而LVDS信号是串行传输的,所以在发送端需要将并行数据转换为串行数据。以8bit RGB显示屏接口为例,每个显示周期需要传输8bit的R信号,8bit的G 信号,8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。而每对LVDS信号线在一个TX周期里只能传输7BIT数据,所以需要4 对数据线,外加一对时钟线。LVDS并串转换如下图所示:  上图中的每一组对线称为一个Pair,4组数据线加一对时钟线称为一个Channel,LVDS发送器总是将一个像素数据映射到(remapping)一个Channel的一个发送周期(TX CLK)中。 如果是6BIT 显示屏,则并行数据有21位(18位RGB加3位控制信号),因此LVDS 接口每个Channel只需要 3对数据线和一对时钟线。 如果是10BIT 显示屏,则并行数据有33位(30位RGB 加3位控制信号),因此LVDS 接口每个Channel需要 5对数据线和一对时钟线。 通常,LVDS接口的时钟为20MHz 到85MHz,因此对于输出像素时钟低于85MHz的信号,只需一个Channel就可以;而对于输出像素时钟高于85MHZ的信号,比如1080P/60HZ的输出,像素显示时钟为148.5MHz,就不能直接用一个Channel传输,而是将输出的像素按顺序分为奇像素和偶像素,将所有的奇像素用一组LVDS 传输,所有的偶像素用另外一组LVDS 传输。也就是说,需要两个Channel来传输1080P/60HZ 的信号。对于像素显示时钟更高的信号,比如1080P/120HZ显示,则需要4个Channel来传输。两Channel、4Channel的像素分配。 VDS信号传输分为DE MODE和SYNC MODE,DE mode需连接DE信号(data enable有效数据选通),SYNC mode还需连接HS(HSYNC行同步)、VS(VSYNC场同步)。SYNC mode在现在的panel中已很少使用,一般都使用DE模式。 传输速率:标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。 LVDS驱动器能以超过155.5Mbps的速度驱动双绞线对,距离超过10m。对速度的实际限制是:①送到驱动器的TTL数据的速度;②媒质的带宽性能。 双工类型:一般为单工,不支持双工。但特殊设计能实现半双工。 上图中的每一组对线称为一个Pair,4组数据线加一对时钟线称为一个Channel,LVDS发送器总是将一个像素数据映射到(remapping)一个Channel的一个发送周期(TX CLK)中。 如果是6BIT 显示屏,则并行数据有21位(18位RGB加3位控制信号),因此LVDS 接口每个Channel只需要 3对数据线和一对时钟线。 如果是10BIT 显示屏,则并行数据有33位(30位RGB 加3位控制信号),因此LVDS 接口每个Channel需要 5对数据线和一对时钟线。 通常,LVDS接口的时钟为20MHz 到85MHz,因此对于输出像素时钟低于85MHz的信号,只需一个Channel就可以;而对于输出像素时钟高于85MHZ的信号,比如1080P/60HZ的输出,像素显示时钟为148.5MHz,就不能直接用一个Channel传输,而是将输出的像素按顺序分为奇像素和偶像素,将所有的奇像素用一组LVDS 传输,所有的偶像素用另外一组LVDS 传输。也就是说,需要两个Channel来传输1080P/60HZ 的信号。对于像素显示时钟更高的信号,比如1080P/120HZ显示,则需要4个Channel来传输。两Channel、4Channel的像素分配。 VDS信号传输分为DE MODE和SYNC MODE,DE mode需连接DE信号(data enable有效数据选通),SYNC mode还需连接HS(HSYNC行同步)、VS(VSYNC场同步)。SYNC mode在现在的panel中已很少使用,一般都使用DE模式。 传输速率:标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。 LVDS驱动器能以超过155.5Mbps的速度驱动双绞线对,距离超过10m。对速度的实际限制是:①送到驱动器的TTL数据的速度;②媒质的带宽性能。 双工类型:一般为单工,不支持双工。但特殊设计能实现半双工。

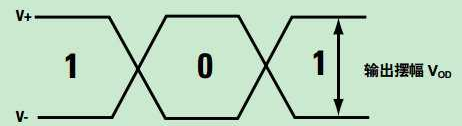

电平类型及范围:LVDS电平,LVDS传输信号为电流驱动信号,终端匹配电阻标准规定为100Ω,由于恒流源为3.5mA,则摆动电平幅度为-350mV350mV。由于偏置电压为1.2V,则差分信号的电压范围为850mV1550mV。 传输线阻抗:终端需要100欧或120欧匹配电阻。 允许并联电容:根据具体速度决定。推荐的最高数据传输速率是655Mbps,而理论上可以达到1.923Gbps。 支持设备数量:有几种应用模式: ① 单向点对点(point to point),这是典型的应用模式。 ② 双向点对点(point to point),能通过一对双绞线实现双向的半双工通信。可以由标准的LVDS的驱动器和接收器构成;但更好的办法是采用总线LVDS驱动器,即BLVDS,这是为总线两端都接负载而设计的。 ③ 多分支形式(multidrop),即一个驱动器连接多个接收器。当有相同的数据要传给多个负载时,可以采用这种应用形式。 ④ 多点结构(multipoint)。此时多点总线支持多个驱动器,也可以采用BLVDS驱动器。它可以提供双向的半双工通信,但是在任一时刻,只能有一个驱动器工作。因而发送的优先权和总线的仲裁协议都需要依据不同的应用场合,选用不同的软件协议和硬件方案。 应用场合:在高速系统内部、系统背板互连和电缆传输应用中,驱动器、接收器、收发器、并串转换器/串并转换器以及其他LVDS器件的应用。 设计要点: 1. 终端放置合适的匹配电阻,一般100欧姆;2. 减少信号通路中阻抗不连续点;3. 通信电缆一定双绞; 4. 驱动器与接收器保持共地。 |

【本文地址】

今日新闻 |

推荐新闻 |

LVDS输出接口分为四个类型:1.单路6位LVDS输出接口;2.双路6位LVDS输出接口;3.单路8位1TL输出接口;4.双路8位1TL输出接口。

LVDS输出接口分为四个类型:1.单路6位LVDS输出接口;2.双路6位LVDS输出接口;3.单路8位1TL输出接口;4.双路8位1TL输出接口。 LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2V。建议接收器的输入电压范围为:0V~+2.4V。 具体芯片的范围有所不同,如常用的DC参数如下:

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2V。建议接收器的输入电压范围为:0V~+2.4V。 具体芯片的范围有所不同,如常用的DC参数如下:  电平变化与逻辑关系:0–1电平表示,,当输出V+=350mA电流,V-=0mA电流–那么输出的为高电平(在接收端的匹配电阻转换为电压值350mv),反之为低电平。

电平变化与逻辑关系:0–1电平表示,,当输出V+=350mA电流,V-=0mA电流–那么输出的为高电平(在接收端的匹配电阻转换为电压值350mv),反之为低电平。