【数字IC/FPGA学习记录】时钟抖动(clock jitter )和时钟偏移( clock skew)是什么意思?CTS (时钟树综合)对 时钟不确定因素(uncertainty) 的影响 |

您所在的位置:网站首页 › fpga的建立时间和保持时间的区别 › 【数字IC/FPGA学习记录】时钟抖动(clock jitter )和时钟偏移( clock skew)是什么意思?CTS (时钟树综合)对 时钟不确定因素(uncertainty) 的影响 |

【数字IC/FPGA学习记录】时钟抖动(clock jitter )和时钟偏移( clock skew)是什么意思?CTS (时钟树综合)对 时钟不确定因素(uncertainty) 的影响

|

题目: 在时钟电路的设计中,存在 jitter (抖动)和 skew(偏移) 问题。请解释: 什么是 jitter,什么是 skew? 在 pre-CTS 的时序约束中,setup 和 hold 的 clock uncertainty 分别由什么组成? 这是我在FPGA探索者微信公众号上浏览到的知识,看懂之后想把它记录下来,加深印象! 回答:

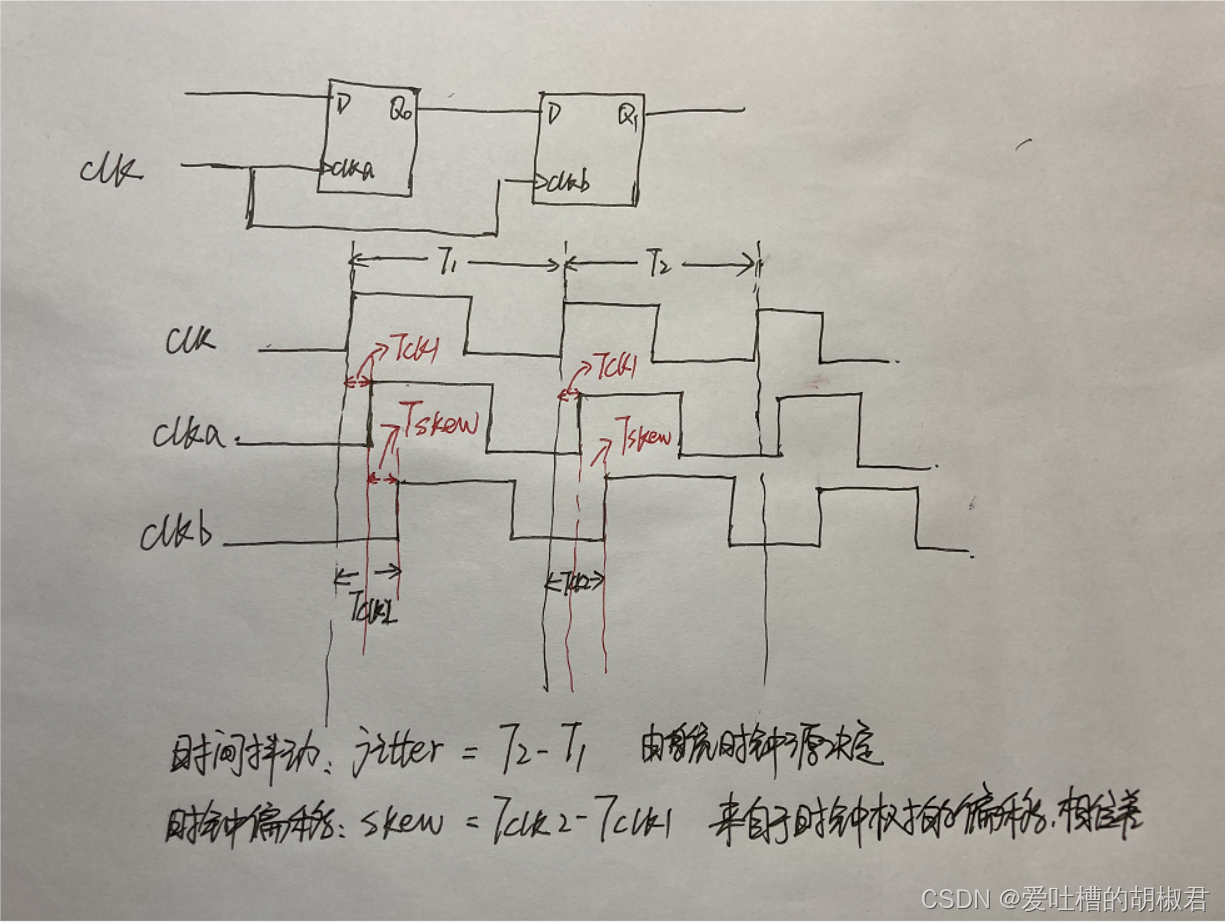

时间抖动:由于时钟在两个周期内存在一定的误差,所以时间抖动为jitter:=T2-T1,这是由系统的时钟源决定的, 解决办法:更换更好的晶振。 时间偏移:时钟在传递的过程中同样也存在一定的误差,第一级触发器的时钟相位偏移为Tclk1,第二级触发器的时钟相位偏移为Tclk2,则传递过程中的误差也就是时钟偏移skew=Tclk2-Tclk1。 解决办法:设置专门的时钟缓冲buffer 在**pre-CTS (前时钟树综合)**的过程中, setup建立时间的不确定性:包含系统时钟的影响(即时间抖动jitter)和**时钟偏移(即skew)**带来的影响。hold保持时间的不确定性只会由**时钟偏移(skew)**决定在**post-CTS (后时钟树综合)**的过程中,时钟树已经被综合,时钟树的偏移已经明确(我是这样理解的,如有不对请大佬指正!) setup建立时间的不确定性包含系统时钟的影响(即时间抖动jitter)带来的影响。 hold保持时间的不受系统时钟影响*,所以已经确定。 |

【本文地址】

在两级触发器中输入信号的时钟和两个寄存器输入的时钟,在实际中一定是有偏差的,如上图所示,在两个时钟周期内

在两级触发器中输入信号的时钟和两个寄存器输入的时钟,在实际中一定是有偏差的,如上图所示,在两个时钟周期内