简谈FPGA比特流结构 |

您所在的位置:网站首页 › fpga对比特流加密 › 简谈FPGA比特流结构 |

简谈FPGA比特流结构

|

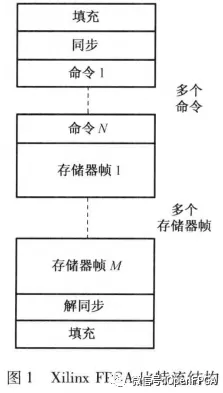

文章来源:OpenFPGA 比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan和Virtex系列。在FPGA上电或随后的FPGA重新配置期间,比特流从外部诸如闪存这样的非易失性存储器中读取,通过FPGA配置控制器的处理,加载到内部的配置SRAM中。 在有些情况下,设计者需要很好地了解FPGA比特流的内部结构。例如,使用FPGA物理实现工具的参数不能访问自定义的低级比特流、实现复杂的配置回溯方案、通过内部配置端口(ICAP)产生用于FPGA重新配置的短命令序列、读配置状态等。遗憾的是,逆向工程和篡改比特流以非法获取专利设计信息也属于这些使用范畴。 比特流格式 Xilinx FPGA的比特流结构如图1所示。

比特流包括以下组成部分:填充、同步字、用于访问配置寄存器的命令、存储器帧和解同步字。 填充 填充的数据是全0或全1序列,被FPGA配置控制器忽略。填充数据用于非易失性存储器中分离比特流。一般使用全1填充较为方便,因为执行擦除后闪存的状态一般也是全1。 同步字 同步字是一个特殊值(0xAA995566),通知FPGA配置控制器处理后续的比特流数据。 解同步字 解同步字通知FPGA配置控制器比特流的末端位置。解同步字之后,所有的比特流数据被忽略,直到遇到下一个同步字。 命令 命令用于读和写FPGA配置控制器寄存器。每个比特流中出现的一些命令,有的是ID-CODE,用于标识比特流属于哪个FPGA器件。帧地址寄存器(FAR)、帧数据寄存器(FDRI)和无操作(NOOP)将被忽略。 存储器帧 存储器帧是配置Xilinx FPGA的比特流基本单元。帧的大小与具体的FPGA系列有关,系列不同,帧的大小也不同。Virtex 6器件的帧有2592位。每个Virtex 6器件具有的帧数不同,从最小7491(对于LX75T)到最大55548(对于LX550T)。帧用于多个逻辑片、IO、BRAM及其他FPGA的配置。每帧都有一个地址,对应于FPGA配置空间的位置。比特流使用FAR和FDRI命令序列来配置帧。 Virtex 6 FPGA配置用户指南包含足够的关于比特流和访问FPGA配置控制器寄存器命令的文档。然而,关于存储器帧的详细文档不仅对于Xilinx FPGA无法获得,而且对于其他供应商的FPGA也是如此。 Xilinx的BITGEN实用程序 BITGEN是Xilinx的实用程序,利用本地电路描述(NCD)格式的布局布线后文件,创建用于FPGA配置的比特流。BITGEN是一个高度可配置的工具,具有100多个命令行选项(在命令行工具用户指南(Xilinx Command Line Tools User Guide,http://www.xilinx.com/support/documentation/sw_manuals/xilinxl 2_2/devref.pdf)中描述)。有些选项用于确定比特流输出格式、启用压缩处理减少比特流大小、提高FPGA配置速度、使用CRC来确保数据完整性、对比特流加密等。 示例 以下示例用于根据差异部分配置的短比特流, 通过脚本语言描述比特流命令。 #!/devl/perl/bin/perl use Switch; # ----------------------------------------------------------------------------- # Copyright (C) 2011 OutputLogic.com # This source file may be used and distributed without restriction # provided that this copyright statement is not removed from the file # and that any derivative work contains the original copyright notice # and the associated disclaimer. # # THIS SOURCE FILE IS PROVIDED "AS IS" AND WITHOUT ANY EXPRESS # OR IMPLIED WARRANTIES, INCLUDING, WITHOUT LIMITATION, THE IMPLIED # WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR A PARTICULAR PURPOSE. # ----------------------------------------------------------------------------- # # A script to parse Xilinx FPGA bitstream in .RBT format # if ($#ARGV < 0) { die "Usage: xilinx_bitstream_parser \n"; } $verbose = 2; open(RBT_FILE," |

【本文地址】

今日新闻 |

推荐新闻 |