Xilinx原语IBUFDS、OBUFDS的使用和仿真 |

您所在的位置:网站首页 › fpga可以仿真吗 › Xilinx原语IBUFDS、OBUFDS的使用和仿真 |

Xilinx原语IBUFDS、OBUFDS的使用和仿真

|

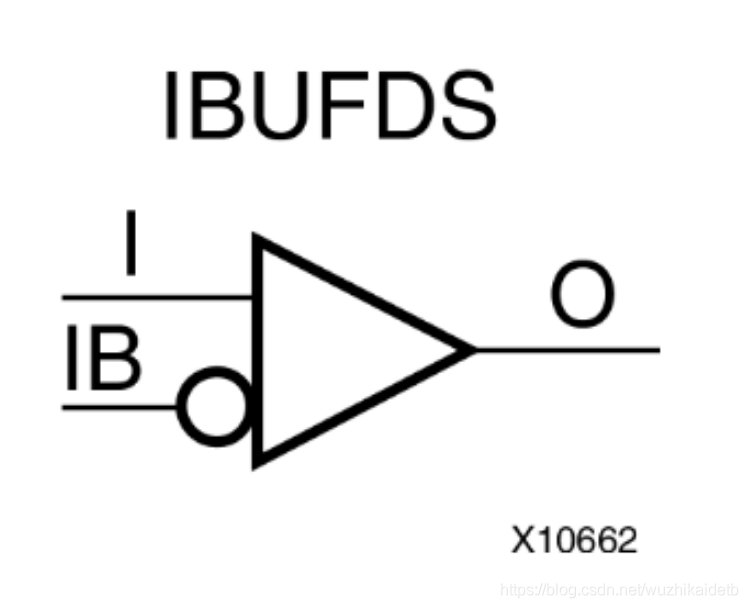

本文转载自:孤独的单刀博客 1、介绍 IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。 2、IBUFDS 2.1、理论 IBUFDS是差分输入缓冲器,支持低压差分信号(如LVCMOS、LVDS等)。在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。一个可以认为是主信号,另一个可以认为是从信号。 IBUFDS原语示意图如下所示:

端口说明如下表:

信号真值表如下:

2.2、仿真 打开VIvado--Tools--Language Templates,搜索“IBUFDS”,可以找到Xilinx提供的模板如下: IBUFDS #( .DIFF_TERM("FALSE"), // Differential Termination .IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE" .IOSTANDARD("DEFAULT") // Specify the input I/O standard ) IBUFDS_inst ( .O(O), // Buffer output .I(I), // Diff_p buffer input (connect directly to top-level port) .IB(IB) // Diff_n buffer input (connect directly to top-level port) ); DIFF_TERM、IBUF_LOW_PWR分别指定差分终端和性能模式,IOSTANDARD指定你需要输出的电平标准。 接下来例化一个IBUFDS原语进行测试,Verilog代码如下: //------------------------------------------------------------------------ //--IBUFDS测试模块 //------------------------------------------------------------------------ //---------------------------------------------------- module IBUFDS_test( input clk , //时钟,50M input rst_n , //复位,低电平有效 input data_p , //输入数据,差分+ input data_n , //输入数据,差分- output out ); //---------------------------------------------------- IBUFDS #( .DIFF_TERM ("FALSE") , // Differential Termination .IBUF_LOW_PWR ("TRUE") , // Low power="TRUE", Highest performance="FALSE" .IOSTANDARD ("DEFAULT") // 选择I/O电平标准,这里选择默认 ) IBUFDS_inst ( .O (out) , // 输出 .I (data_p) , // 差分输入+(需要直接连接到顶层端口) .IB (data_n) // 差分输入-(需要直接连接到顶层端口) ); endmodule 每隔20ns分别随机生成2个1位2进制数据作为差分输入,观察输出,Testbench如下: //------------------------------------------------ //--IBUFDS原语仿真 //------------------------------------------------ `timescale 1ns/1ns //时间单位/精度 //---------------------------------------------------- module tb_IBUFDS_test(); reg clk ; reg rst_n ; reg data_p ; reg data_n ; wire out ; //---------------------------------------------------- IBUFDS_test IBUFDS_test_inst( .clk (clk) , .rst_n (rst_n) , .data_p (data_p) , .data_n (data_n) , .out (out) ); //---------------------------------------------------- initial begin clk = 1'b1; //初始时钟为1 rst_n |

【本文地址】

今日新闻 |

推荐新闻 |