PADS |

您所在的位置:网站首页 › double的转换说明 › PADS |

PADS

|

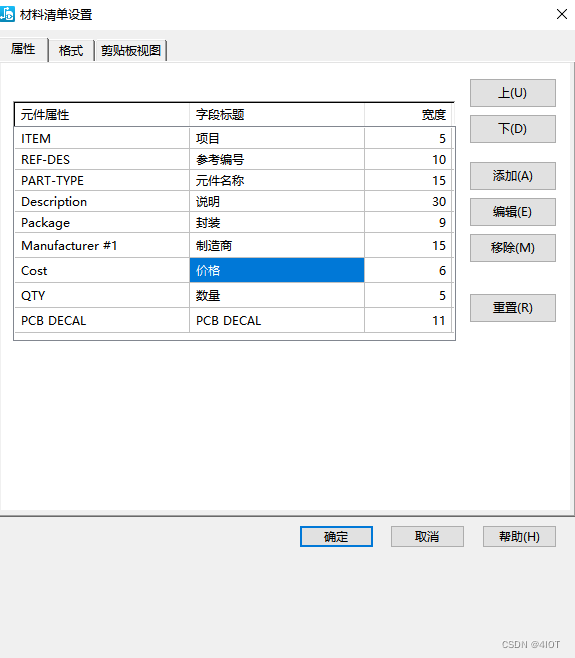

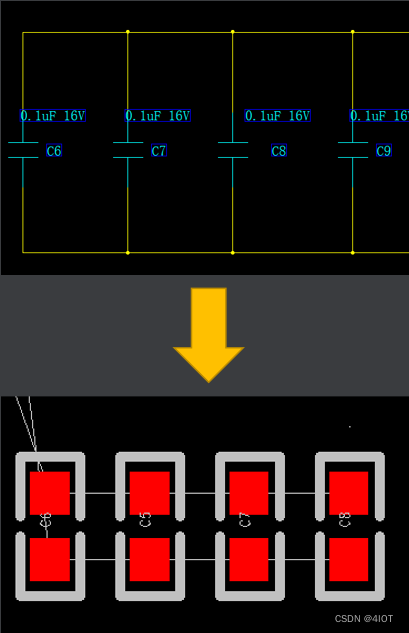

目录 1 材料清单输出 2 元件属性检查 3 材料清单制作 4 原理图生成PDF 4.1PDF文件生成 4.2PDF文件查阅 4.3PDF文件打印 5 PADS转Altium Designer 5 Altium Designer转PADS 5.1 直接导入法 5.2 软件生成法 6 PADS层定义 7 设计规则输出 7.1 PADS对象管理 7.2 PADS规则分类 7.2.1默认规则(优先级最低) 7.2.2类规则 7.2.3 网络规则 7.2.4 组规则 7.2.5 管脚对规则 7.2.6 封装规则 7.2.7 元件规则 7.2.8 条件规则 7.2.9 差分规则 8 PADS默认规则 8.1安全间距 8.2 布线规则 8.3 扇出规则 9 网表输出 9.1 Logic 网表输出 9.2 网表错误报告 9.3 Layout链接 1 材料清单输出属性检查,再剪贴板复制到表格

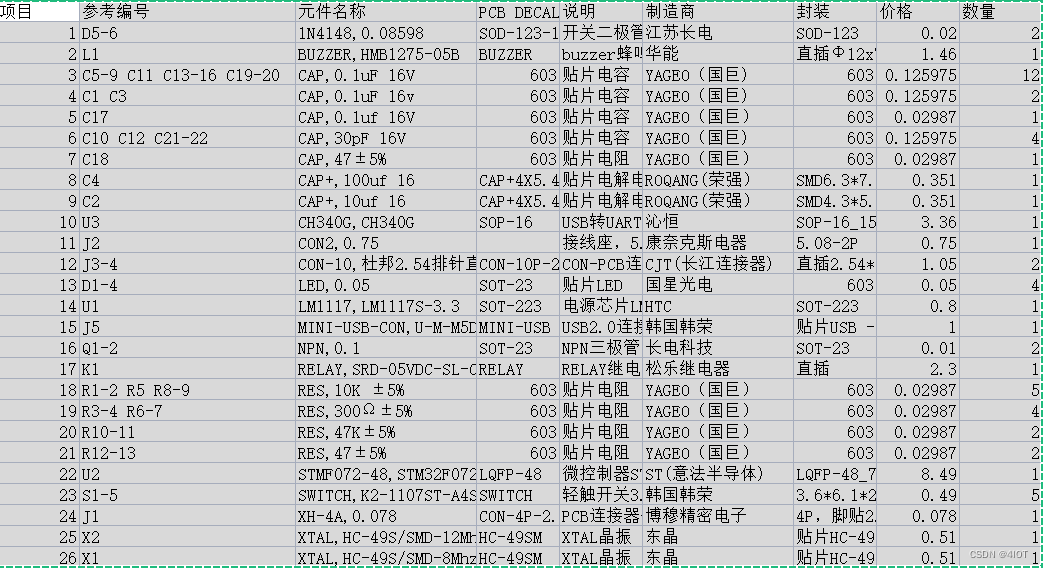

EXCEL中观察 上面表格发现电容没有封装描述,另外元件编号最好从1开始从而重新编号,0603以文本显示出来,参考编号可能也会有误,所以要再次检查。

属性信息查缺补漏 元件信息重新编号 重新报告里面添加内容检查内容,生产表格

元器件价格汇总 添加表格标题 添加边框显示 表格排版

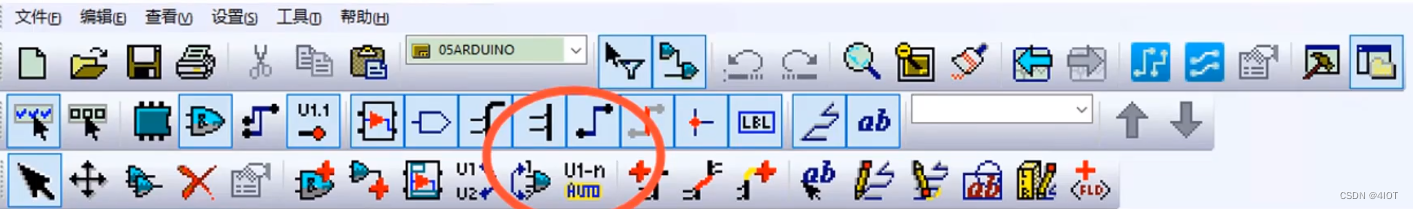

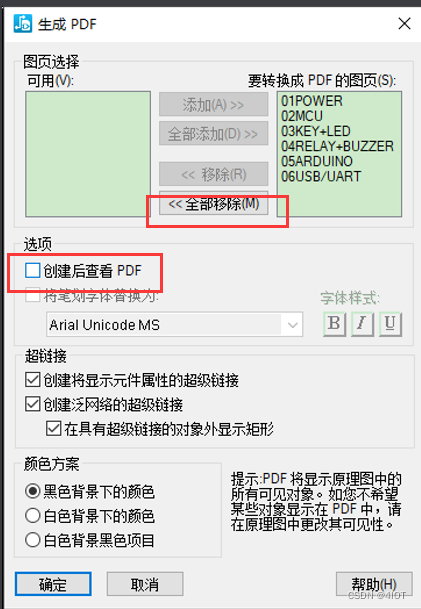

最后输出PDF文件 4 原理图生成PDF 4.1PDF文件生成

中文字体会出现乱码 4.3PDF文件打印上述情况可以用PDF文件打印

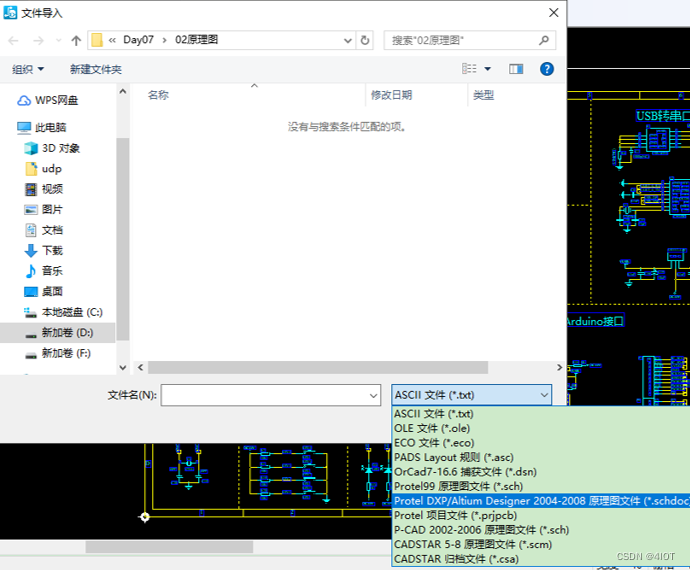

上述的PDF无法跳转和查看属性,不过也是够用了。 5 PADS转Altium Designer到处ASCII码输出

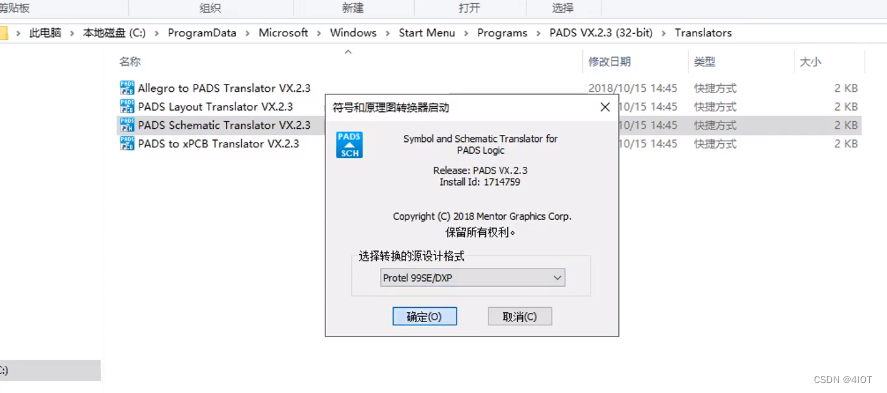

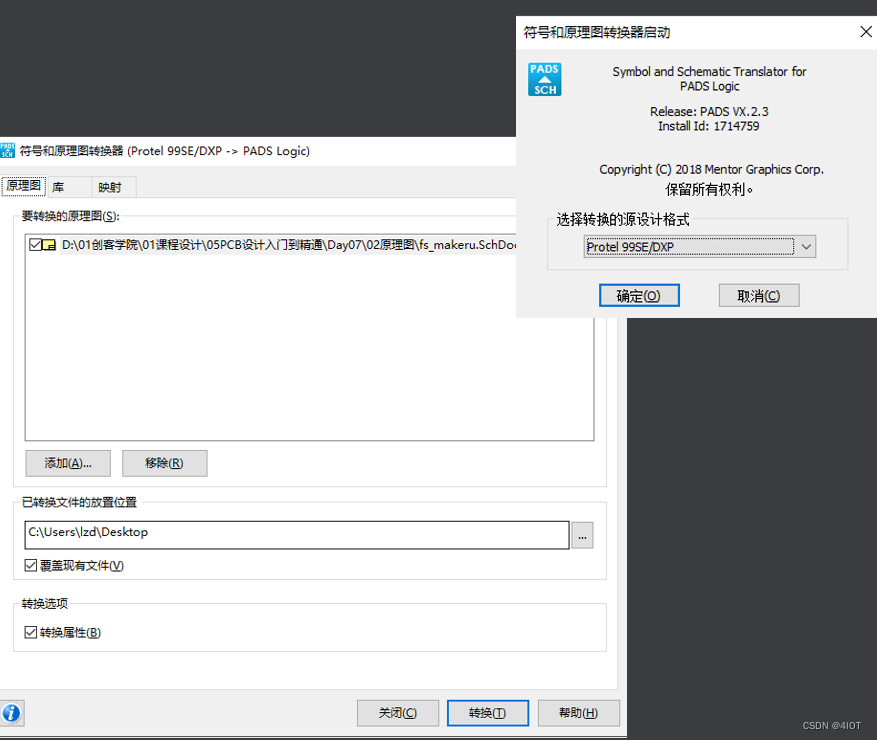

原理图的属性可能会缺失,PCB封装会空,需要二次加工,但是也比新建快很多。 5.2 软件生成法找到转换工具

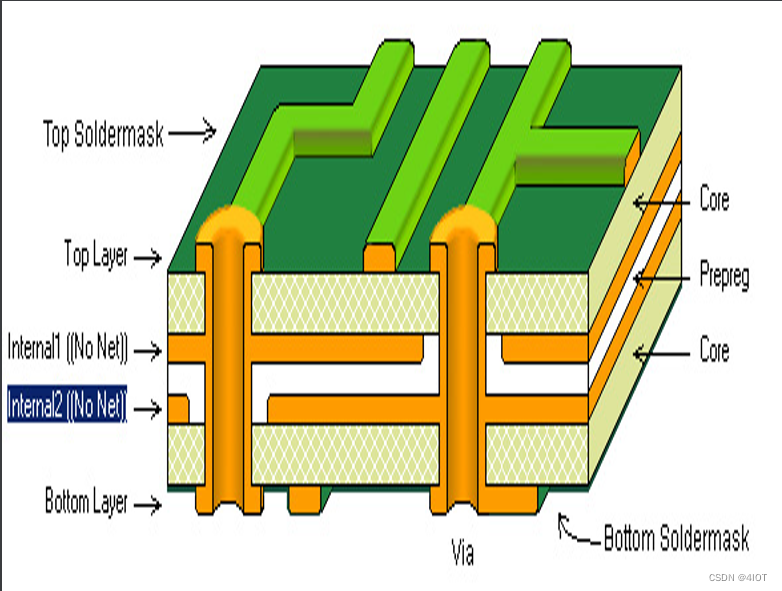

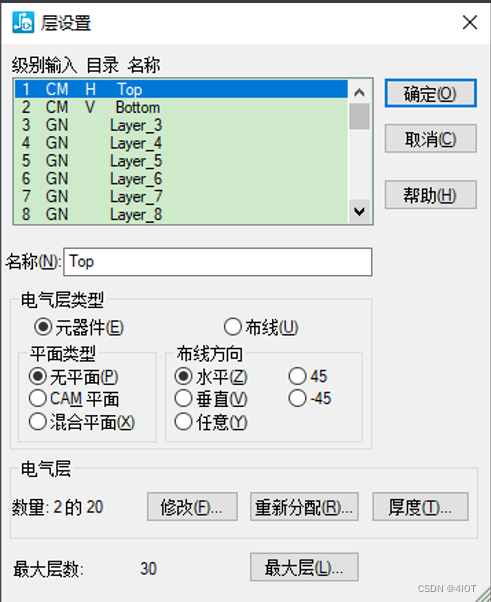

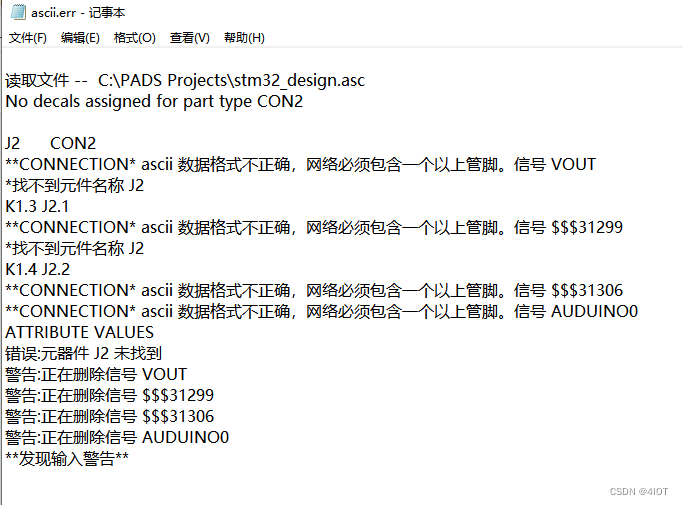

下图是个4层板

以下是PADS中常见的层定义: Top Copper Layer:顶层铜层,即位于电路板最上层的铜箔层,用于布线及器件放置等功能。 Bottom Copper Layer:底层铜层,即位于电路板最下层的铜箔层,同样用于布线及器件放置等功能。 Inner Signal Layers:内部信号层,通常为第三层之后的内层铜箔层,用于信号传输和电源分配等功能。 Power Plane Layers:电源平面层,用于电源分配和噪声抑制等功能。 Ground Plane Layers:地面平面层,用于地面平面填充和EMI抑制等功能。 Soldermask Layers:焊膜层,用于保护铜层免受腐蚀和氧化。阻焊层 Silkscreen Layers:丝印层,用于标识和显示元件名称、值以及其他板级标志。 Drill Layers:钻孔层,包括机械孔、贴片孔、盲孔和埋孔等。 这些层定义可以根据具体的PCB项目需求进行定制和调整。PADS提供了灵活的层管理和设置功能,用户可以根据自己的需要选择使用哪些层,并对其进行特性、顺序和堆叠等设置。同时,为了保证设计的正确性和一致性,在进行任何修改之前,建议先进行详细的层定义和计划,并与设计规范和标准相匹配。 叠层配置

在PADS中,层设置中的无平面、CAM平面和混合平面分别表示不同的铜箔层定义和用途。 无平面:这是一种没有任何铜箔层的板模式,也就是将铜箔全部去掉。无平面模式通常用于单面或双面电路板设计中,其中的信号铜层即为顶层和底层铜层。(多层一般选择) CAM平面:这是一种将内部铜层全部铺满成大块铜,并与电源和地信号相连的铜箔层定义,通常用于电源分配和EMI抑制等应用。CAM平面通常采用连接到最近的电源或地信号的方式来减小串扰和噪声等干扰。 混合平面:这是一种将部分内部铜层做为电源平面,另外一部分做为地面平面,同时也可将其他内部信号层连接到适当的电源或地面层。混合平面通常用于需要抑制EMI、噪声和交叉干扰的多层PCB设计中,能够实现信号完整性仿真、电源管理和EMI分析等功能。 以上三种平面定义的选择和设置都需要结合具体的PCB设计需求和规范进行,以保证设计的正确性和可靠性。如果您需要更深入的了解,建议向PADS官方文档或论坛进行查询和咨询。 修改可以改层数。

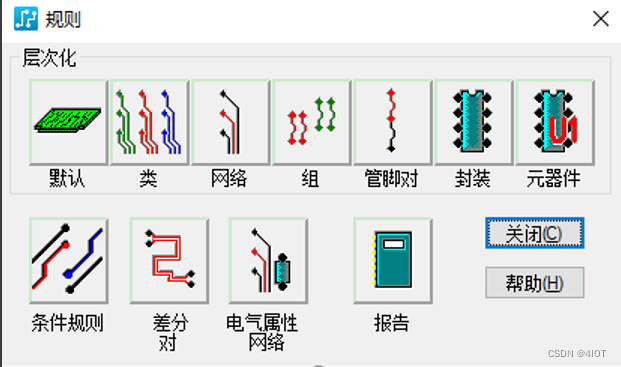

PADS自一开始就提出了“设计即正确”的的概念,它之所以能做到这一点,是因为它有一个实时监控器(设计规则约束驱动器)。PADS Layout预先设置了很多规则,实时监控用户的设计,在违反设计规则时,系统会禁止用户继续操作或是给出警告等。 7.1 PADS对象管理

PCB板上有封装、走线、引脚、过孔、钻孔、丝印、铜皮、板框等很多对象。

PADS对象管理将PCB中涉及到的对象全面归类,分为默认、类、网络、组、管脚对、封装、元器件、条件规则、差分对 9种,每一个对象层均管理属性相同的一类对象。9种优先级电气属性优先级最高,默认的最低。 PADS 将对象组织为一个层次结构,不同层所在的对象表示不同的优先级,上一层设计规则将被下一层设计规则覆盖(即越往下优先级越高),如网络层层与类层对同一个网络设置分别设计不同的设计规则,则PADS系统会按照网络层设置的规则对PCB进行检查。 7.2 PADS规则分类 7.2.1默认规则(优先级最低)

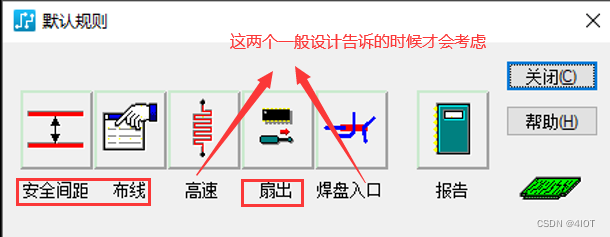

默认规则的意义:默认设计规则具有整体性,如果其他没有进行设置,则当前设计中所有对象的设计规则都是以默认设计规则为准,这是优先级最低的规则设置,一旦其它任何项进行了相同的设置,该规则就会被新的规则覆盖。 7.2.2类规则

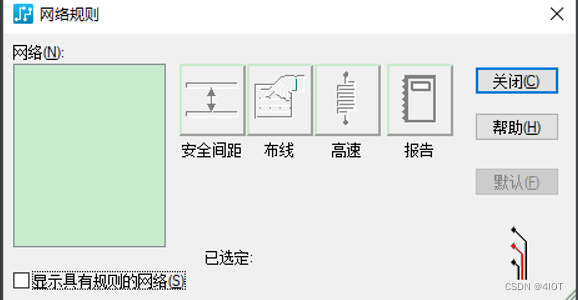

所谓的类,是指一组具有相同电气特性,可以使用相同设计规则的网络。在实际设计中,电源网络和信号网络的设置规则不同,时钟信号网络与一般信号网络不同,通过将这些网络分为不同的类来统一设置 7.2.3 网络规则

类规则设置的对象是一组具有相同设计规则的网络,而网络规则设置的对象是每个单独的网络,就像放大镜一样,网络规则更仔细地对类规则中的每个网络分别进行设置,因此,网络规则的优先级比类规则的优先级高。例如:类规则中电源、地分为一类,那么网络规则中可以只对设置电源。 7.2.4 组规则

对网络连接的元器件管脚进行定位。任何一个网络都会连接一个或多个元器件,那么相应的在一个网络内就会有多个管脚对。所谓管脚对是指两个元件的连接,它可以是某一网络,也可以是某网络的一部分。针对一个网络里,可能连接很多个器件,如芯片管脚走线要间距大一点,但是器件走线要细一点。 7.2.5 管脚对规则

管脚对规则的对象是某一管脚对,而组是一组具有相同设计规则的管脚对集合,可见管脚对规则具有比组设计规则更高的优先级。 7.2.6 封装规则

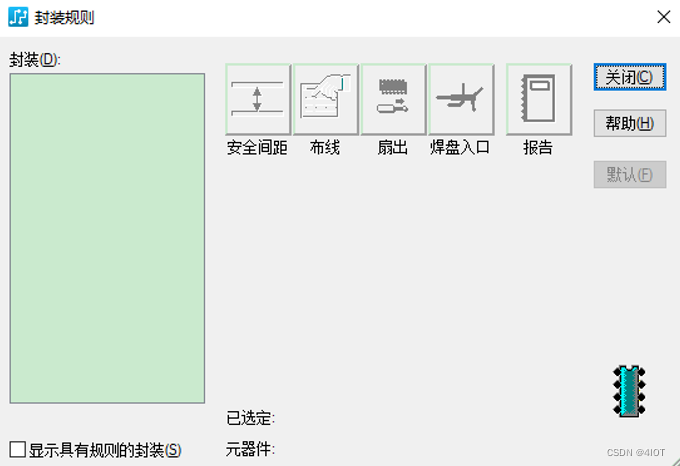

封装规则是针对元件的封装而言的,在一个PCB中,不同封装之间的差异可能很大,因此需要针对不同的封装进行不同的规则设置。如果在封装规则中对某一封装进行了设置,则整个设计中具有相同封装的元件都使用该规则。例如:可以针对0603、0805设计规则。 7.2.7 元件规则

元件规则的设置对象是每一个元件,用户可以设置与一个元件相关的安全间距、布线规则、扇出规则、走线与焊盘关系。例如:0603由电阻、电容,可以只针对0603封装的电容进行设置规则。 7.2.8 条件规则

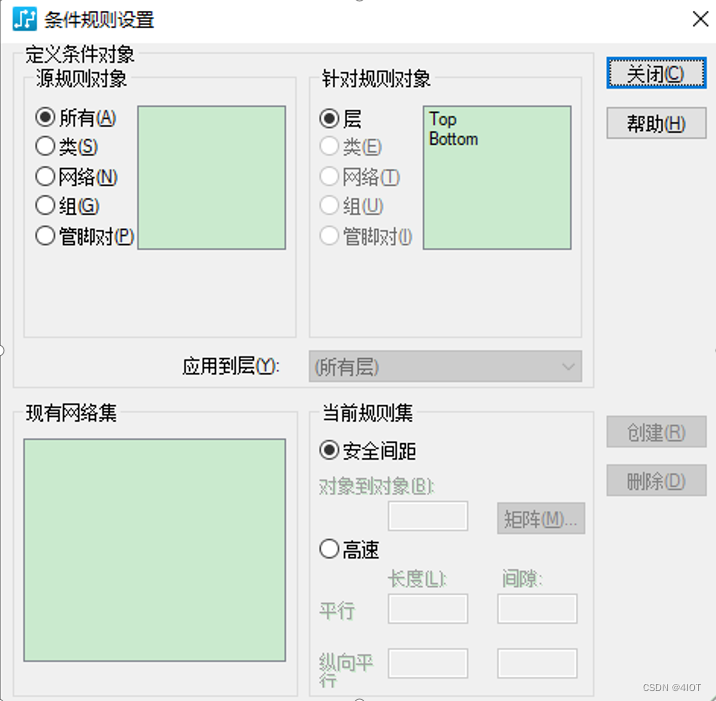

条件规则可以分为两种类型:Design Rules和Constraint Rules。 Design Rules是对PCB设计的基本要求进行限制和约束,以确保电路板的正确性、稳定性和可靠性。例如,它可以规定连线宽度、间距、弯曲半径、堆叠顺序等参数,以及检查电气连接、短路、接地等问题。 Constraint Rules则是对特定元器件或系统功能要求进行限制的规则,可以根据设计需求进行设置。例如,它可以规定某些元器件的安装位置、方向、尺寸等参数,或者约束某些信号线的长度、捷径、时间延迟等限制。 设置好规则后,PADS就会自动检查设计中的元器件、线路、布局等是否符合规则要求,并给出相应的警告或错误提示,帮助用户进行修改和优化设计。 7.2.9 差分规则

差分信号通常用于传输高速和高频信号,如USB、HDMI、PCIe等。利用差值来表示信号的0和1。而PADS中的差分规则就是用来定义差分信号线宽、间距、阻抗等特性的规则。 具体来说,差分规则主要包括两个方面:长度匹配和阻抗匹配。对于长度匹配,PADS会根据差分信号的特性(如速率、波形等)自动计算出要求的差分线长度。对于阻抗匹配,则需要设置差分线宽、间距、线距板子的距离等参数来确定要求的差分阻抗值。 通过设定差分规则,可以确保差分信号尽可能地匹配,减少因长度、阻抗等差异而导致的干扰和损失,从而提高传输质量和稳定性。同时,在PADS中,还可以通过差分信号的视图查看和验证差分规则是否满足要求,进一步优化设计效果。 8 PADS默认规则 8.1安全间距

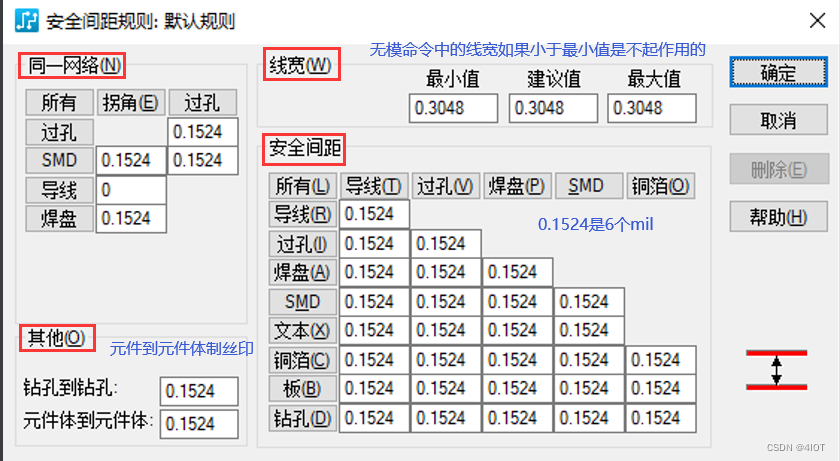

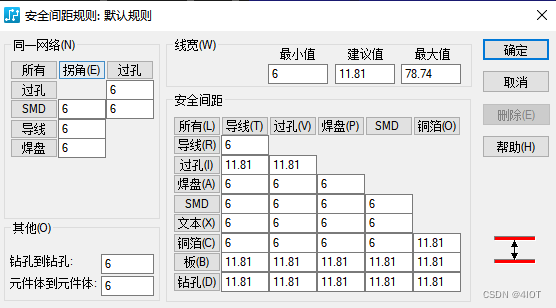

目前国内最小的制版厂商是5mil,要根据制版厂商工艺来设置。 8.2 布线规则

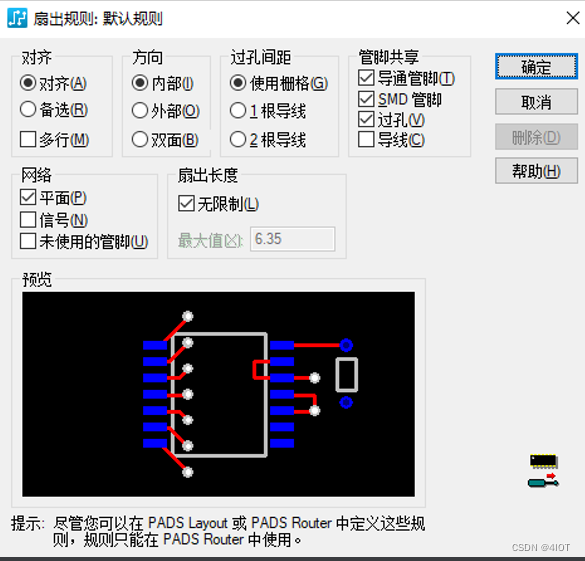

扇出规则(Fanout Rules)是指在PCB设计中,用于控制每个器件引脚上连接的导线数量和宽度,并保持适当的板面积和电气信号完整性。在PCB设计中,每个器件的引脚都需要与其他部件相连,而这些引脚之间的互联,将会带来各种电气特性问题,如全局数据延迟、串扰、耦合等。因此,扇出规则就显得很重要。 PADS的扇出规则可以控制每个引脚的最大连接数、最小线宽、最小间距、最小环距等参数。其中,最大连接数通常是基于多个因素来确定的,例如引脚数量、器件类型、板上连接器的数量和电气特性等。例如,在高速数字电路中,由于引脚之间的串扰问题,通常会限制每个引脚的最大连接数为4个或更少,以保证信号完整性。 除了这些参数外,PADS的扇出规则还可以控制通过特定引脚的导线宽度、避免狭长导线的出现、最小环距等。这些规则可以有效地控制PCB的设计,确保布局合理、电气完整性好,提高了电路的可靠性和稳定性。 需要注意的是,扇出规则是每个引脚独立计算的。在实际设计中,可能需要对其进行手动调整,以满足特定的设计需求和实际情况。因此,在使用PADS进行PCB设计时,应该根据项目要求和具体的器件来调整扇出规则,以得到最优的结果。 最后,实际STM32最小版的2层板进行设置一下,0.3更稳定可靠。在导出PADS-LayOut的时候就具有了设计规则。

在PADS中,安全间距(Safety Spacing)是指在PCB设计中相邻两条导线之间应该留出的最小空隙,以确保电路板的可靠性和稳定性。通常情况下,应该将安全间距设置为符合标准的数值,而具体的数值取决于设计的要求和器件的要求。 将安全间距设置为0.3mm有以下几个好处: 避免短路:如果相邻的两条导线之间的间距太小,就会发生短路等意外情况,从而影响电路的正常运行。将安全间距设置为0.3mm可以有效地避免这种情况的发生。 提高电路板的可靠性:在电子产品中,一些高精度、高速度的信号需要经过复杂的电路处理。如果相邻的导线之间的距离太小,就可能会影响信号传递,甚至导致电路故障。因此,在设计PCB时,合理设置安全间距可以提高电路板的可靠性。 保证电气特性:在高速数字电路中,由于信号延迟、串扰、反射等问题,相邻导线之间的间距需要满足更严格的要求。在这种情况下,将安全间距设置为0.3mm可以确保电气特性满足设计要求。 需要注意的是,在实际设计中,安全间距的具体数值应该根据电路板的要求和器件的要求进行调整,以得到最优的设计方案。 9 网表输出

网表(Netlist)是一种用于描述电路连接关系的格式。在电路设计中,通常需要将原理图转换为网表,以便进行后续的电路仿真、布局和制造。 网表是一种文本文件,其中包含了电路中所有器件的名称、引脚信息和连接信息等。网表格式通常与EDA工具相关,不同的EDA工具会使用不同的网表格式。常见的网表格式有SPICE格式、EDIF格式、Verilog格式、VHDL格式等。 将原理图转换为网表的过程叫做网表提取。网表提取的目的是将原始的电路描述转换为EDA工具可以识别和处理的格式,以支持电路仿真和布局等操作。网表提取的过程中,需要将原理图中的元器件转换成相应的模型,并将它们之间的连线转化为电路中的节点和网。同时,还需要对信号名称、管脚波特率、电源等信息进行解析和转换。 网表提取是电路设计过程中非常重要的环节,它影响到电路仿真和布局等环节的准确性和效率。因此,在进行网表提取时,需要仔细检查和验证,确保生成的网表与原理图一致,并尽可能地优化电路的性能和可靠性。 9.1 Logic 网表输出

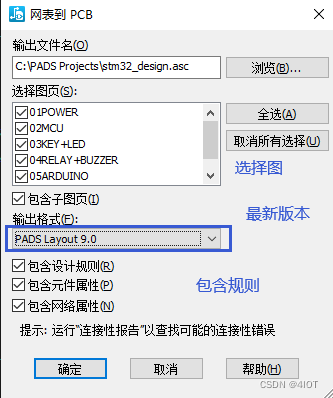

9.2 网表错误报告

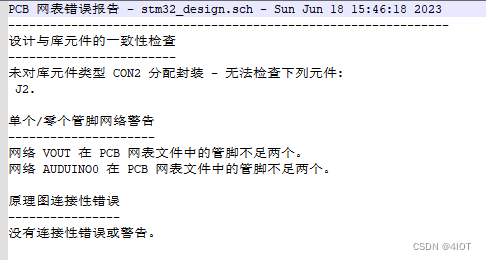

如果有错误,err会提示

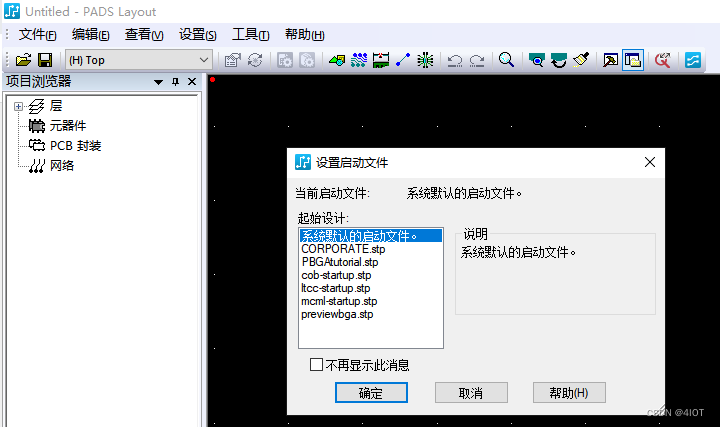

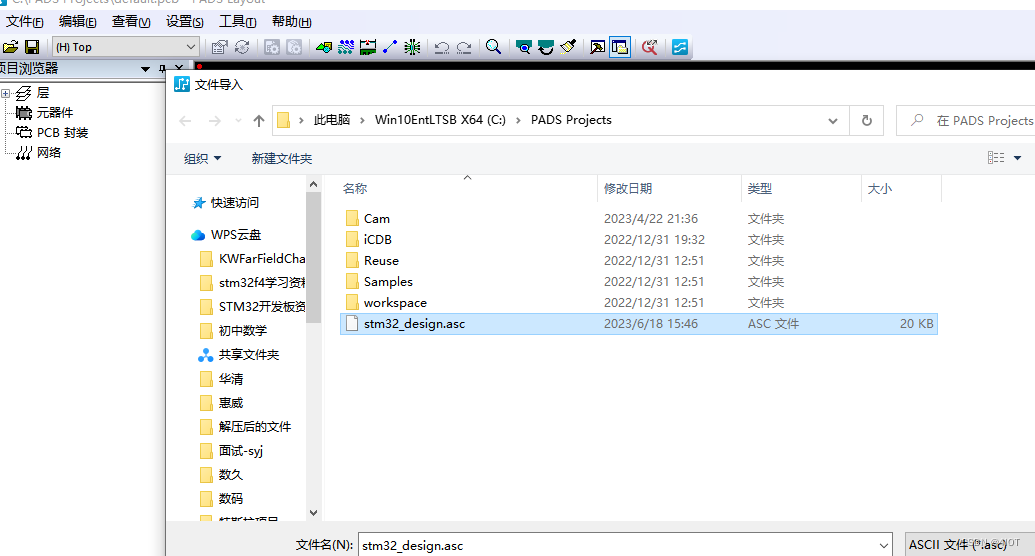

打开Layout,文件,新建启动文件 会提示一些错误

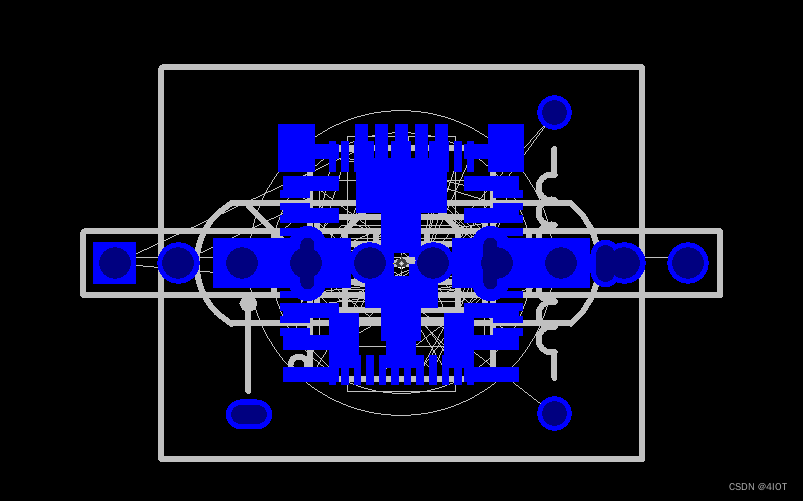

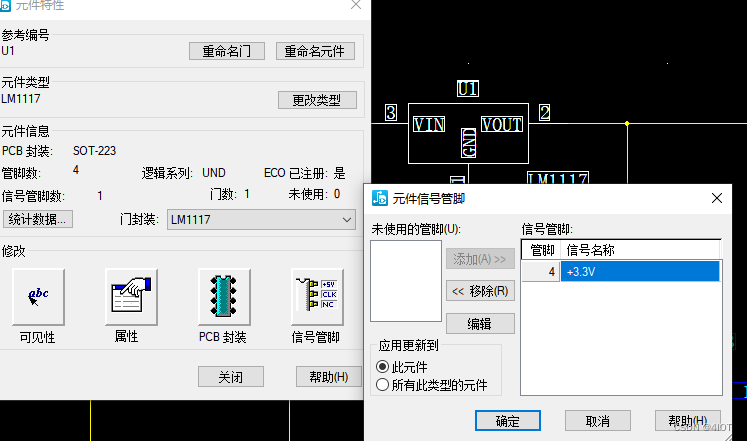

修改错误: VOUT管脚是在设计电源的时候有4个管脚,我们只用了3个,所以VOUT空出来了,2、4是相连的,可以连接到3.3V

改为+3.3V

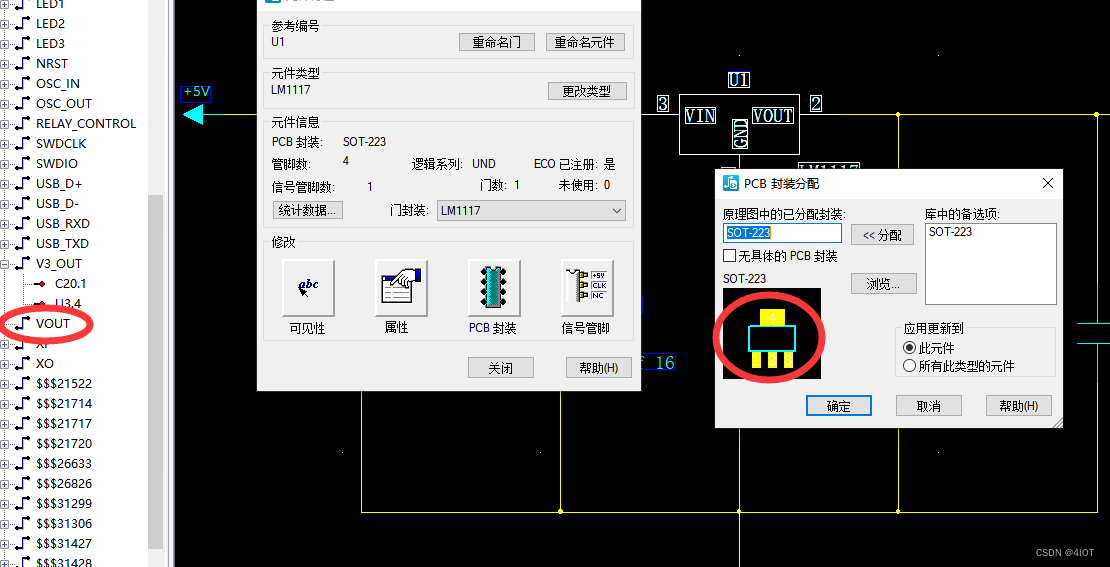

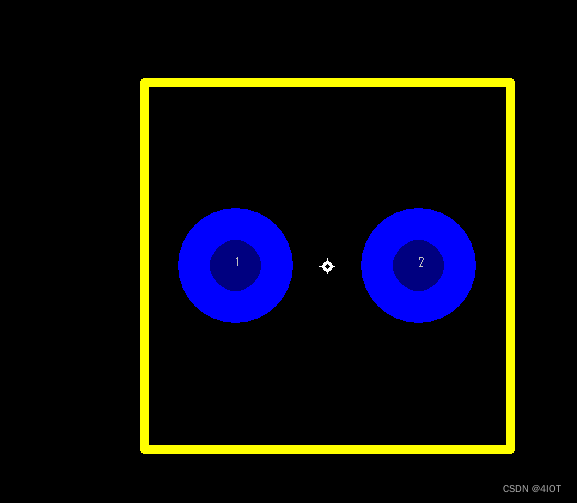

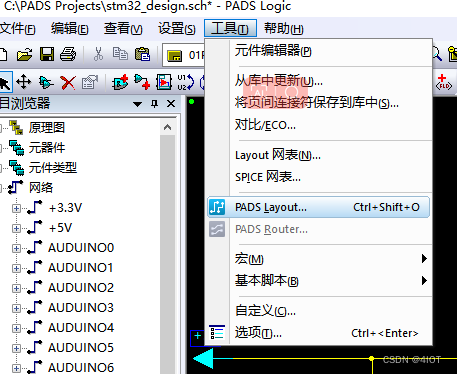

新建PCB封装5.08-2P 解决错误后,err文件消失,只生产了.asc的网表文件格式 重新导入网表到Layout 9.3 Layout链接在Padslogic里,Layout链接设计选项 CTRL+SHIFT+O

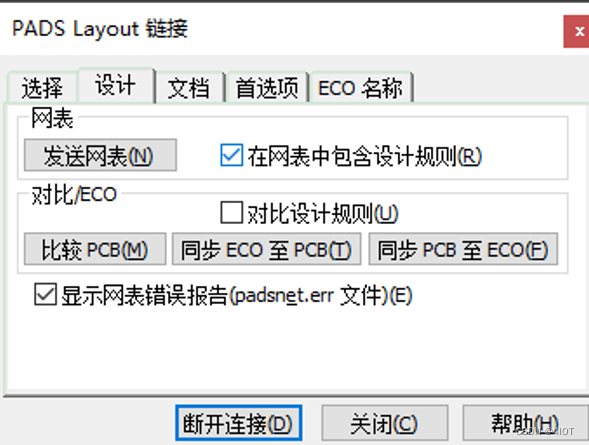

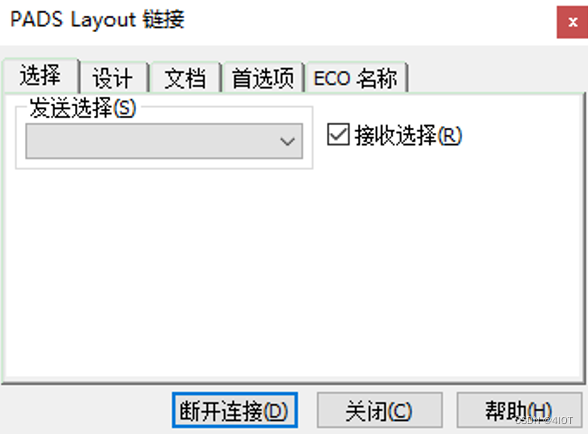

网表:不需要通过工具网表输出,只需要发送网表 对比/ECO:打勾Layslogic会更改Layout规则,一般不勾 比较PCB:比如0603改成0805是在原理图上改的,点击PCB可以同步到Layout 同步ECO至PCB:对原始PCB Layout进行修改和更新,并将这些修改同步到实际的PCB中+

文档 有可能打开多个PCB需要关注是否是你设计的PCB

首选项 忽略未使用的管脚网络,一般不勾 对比PCB封装分配:如果原理图里更新了,PCB不同步,这里就不会同步 包含属性:同上

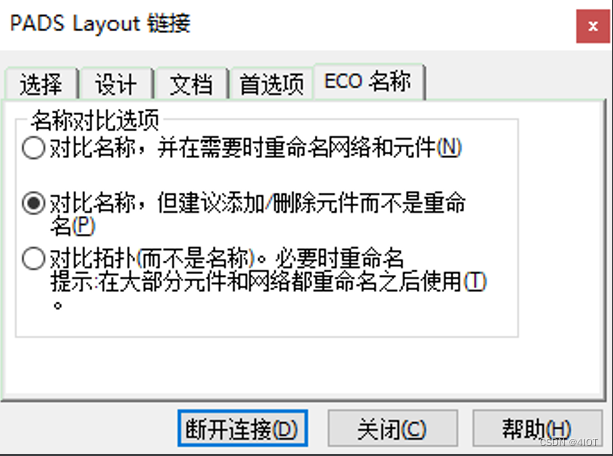

ECO名称: 一般选择默认

选择 可以选择原理图中的元件,PCB会高亮,这是Layout与PCB同步的特性

实际操作:先同步网表,再去Layout中看一些,比如设计规则已经同步过来了,11.81mil就是0.3mm

选择元件,同步高亮

|

【本文地址】

今日新闻 |

推荐新闻 |