【PCIE体系结构十五】电气物理层之接收端CTLE&DFE |

您所在的位置:网站首页 › dfe均衡器原理 › 【PCIE体系结构十五】电气物理层之接收端CTLE&DFE |

【PCIE体系结构十五】电气物理层之接收端CTLE&DFE

|

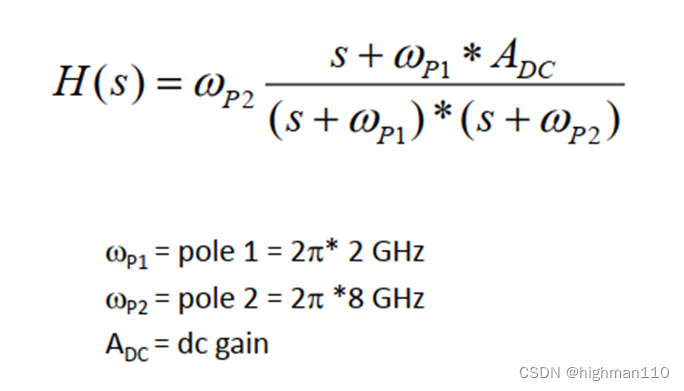

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考书籍:《PCI.EXPRESS系统体系结构标准教材 Mindshare》 参考文章:https://www.eetop.cn/measurement/6948203.html 接收端均衡接收端的眼图能不能张开,接收端会不会发生码间干扰,关键不在于信号的衰减,而在于高频分量和低频分量的衰减差异。传输链路通常可以看做是一个低通滤波器,其对高频分量的衰减作用远大于低频分量,所以经过这一段传输链路后,信号的边沿将会越来越缓,眼图就越来越小。所以发送端先用FFE,增加信号中高频分量的比例用来对冲链路上的损耗。但前面我们说过,去加重的幅度不能过低,过低又会导致接收端眼高不够,也就是说发送端FFE只能解决部分问题,万一经过类低通滤波器的传输链路后,高频分量被衰减,低频分量又太高了怎么办?所以接收端还需要另做处理来补偿链路上的高频分量和低频分量的损耗差。 PCIE接收端有两种均衡器,CTLE(Continuous Time Linear Equalizer,连续时间线性均衡器)和DFE(Decision Feedback Equalizer,判决反馈均衡器)。在PCIe 3.0 & 4.0基础规范中,并没有明确地规定接收端的结构是怎样的,而只是从测量的角度对接收端性能进行了规定。相反地,在规范中定义了一个行为级CTLE和行为级DFE。这些行为级模型可以作为设计指南;并且为了使得待测对象能够通过规范的要求,一般来说用户所设计的接收端性能至少要等于这些行为级模型的性能,可以强于这些行为级模型,但不能弱于这些行为级模型。 发送端的输出在经过一段很长的FR4走线之后,仅仅使用CTLE,可能是不够的。因此在PCIe 3.0 & 4.0中,还使用了DFE的技术。在3.0中,使用1-tap的DFE,在4.0,由于速率相对于3.0翻倍了,所以使用2-tap的DFE,在5.0,速率继续翻倍到32GT/s,使用了3-tap的DFE,以便移除更大的ISI。 先来看CTLE,如下是PCIE 3.0的CTLE传递函数和信号增益的频率响应,4.0的差不多:

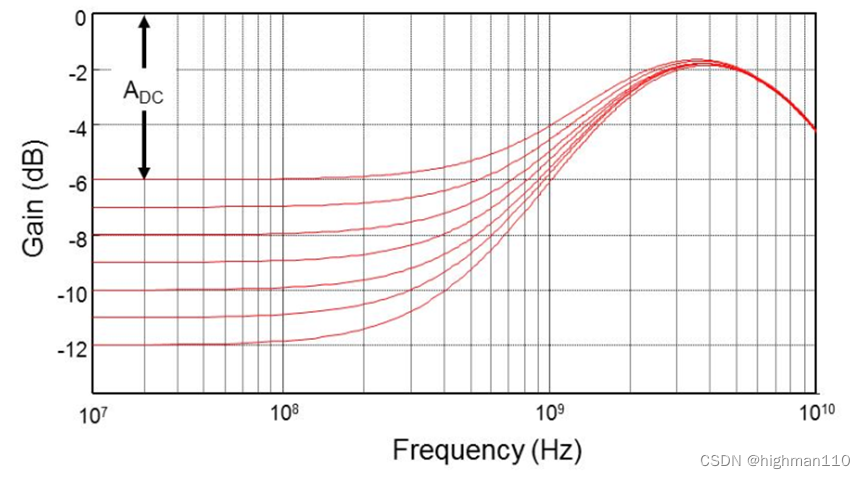

从上图可以看到,对于8.0 GT/s速率,ADC(adjustable DC gain,可调直流增益)可在-6dB至-12dB的范围内进行调整,步长为1.0 dB。增益是负的,就表示信号是衰减的,而且在10MHz~1GHz的低频段的衰减量大,在1GHz~10GHz的高频段内衰减量相对较小,整体表现为一个高通滤波器特性,且8.0 GT/s数据速率的基频是4GHz,上述1GHz~10GHz的通频带也是合理的。这个高通滤波器就与走线的类低通滤波器形成了互补,如下图,补偿了走线在高频段的衰减。

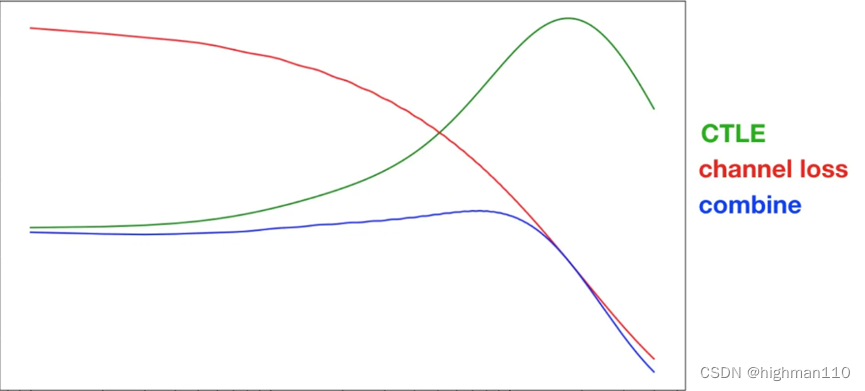

实际应用中CTLE虽然补偿了高频信号,但同时外部的噪声与串扰会相对被放大(正常信号的低频直流分量被衰减了,高频噪声就相当于放大了),还需要与DFE配合使用才能达到最优的效果。 与线性均衡器FFE和CTLE相比,DFE为一种非线性均衡器。DFE的基本思想是:若已经正确接收了之前的比特数据的话,那么先前的比特数据对当前比特所产生的影响就是已知的,从而我们就可以通过反馈的方式进行补偿,这样就能够进一步消除抖动和噪声的影响。不难看出这里的非线性体现在:反馈回来的信号是经过判决之后的数字信号,而判决电路是一种非线性电路。显然,反馈通路上的抽头数目越多,那么对抖动和噪声的消除可能就越好,这也就是为什么3.0中使用1-tap的DFE,而在4.0中使用2-tap的DFE。如下图示DFE的效果:将产生了码间干扰的拖尾部分用过反馈压下来,是一个码元的能量限定在一个UI之内。 如下是规范定义的3.0的DFE行为级模型:

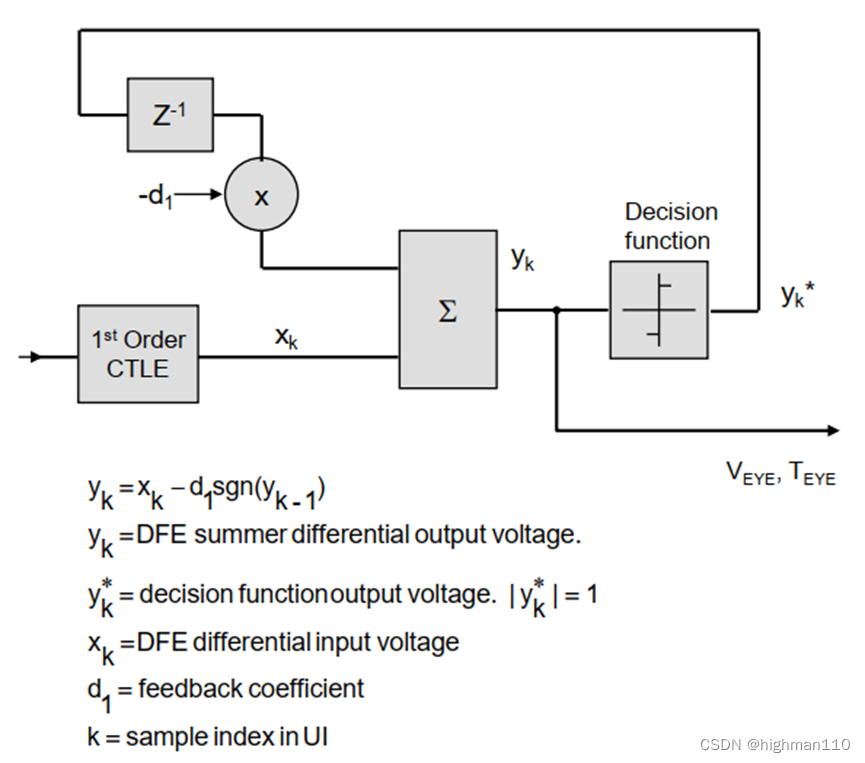

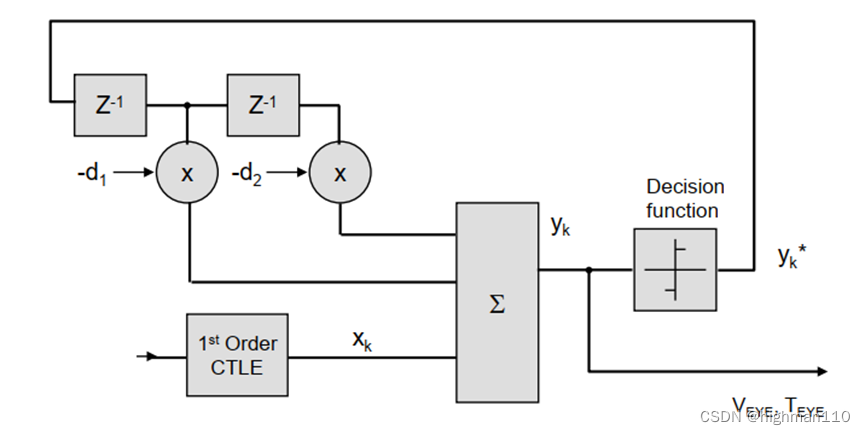

如下是4.0的DFE行为级模型:

图中的两个反馈系数,对于8.0 GT/s和16.0 GT/s,d1的限值为±30 mV。对于16.0 GT/s,d2的限值是±20 mV。

|

【本文地址】

今日新闻 |

推荐新闻 |