Verilog:【1】时钟分频电路(clk |

您所在的位置:网站首页 › devider是什么意思 › Verilog:【1】时钟分频电路(clk |

Verilog:【1】时钟分频电路(clk

|

碎碎念: 作为Basic Verilog的第一个学习笔记,打算用这种命名方式来对博客进行命名,应该有助于检索。 简单阅览了部分工程的代码,发现里面有很多嵌套关系,因此决定先从基础模块开始,也是为了整个博客内容的流畅性。 读者朋友有问题的话,也可以随时和我进行讨论!咋们一起学习,一起进步! 目录 1 模块功能 2 模块代码 3 模块思路 4 TestBench与仿真结果 1 模块功能通过计数器来将时钟进行分频处理的功能,通过修改parameter部分,可以用来修改输出数据的范围大小。 2 模块代码 //------------------------------------------------------------------------------ // clk_divider.sv // published as part of https://github.com/pConst/basic_verilog // Konstantin Pavlov, [email protected] //------------------------------------------------------------------------------ // INFO ------------------------------------------------------------------------ // Divides main clock to get derivative slower synchronous clocks // /* --- INSTANTIATION TEMPLATE BEGIN --- clk_divider #( .WIDTH( 32 ) ) CD1 ( .clk( clk ), .nrst( 1'b1 ), .ena( 1'b1 ), .out( ) ); --- INSTANTIATION TEMPLATE END ---*/ module clk_divider #( parameter WIDTH = 32 )( input clk, input nrst, input ena, output logic [(WIDTH-1):0] out = '0 ); always_ff @(posedge clk) begin if ( ~nrst ) begin out[(WIDTH-1):0] begin clk = 0; forever begin #half_cycle clk = 1; #half_cycle clk = 0; end // --> end $display("Running testbench"); end clk_divider #( .WIDTH( 32 ) ) CD1 ( .clk( clk ), .nrst( 1'b1 ), .ena( 1'b1 ), .out( out ) ); endmodule

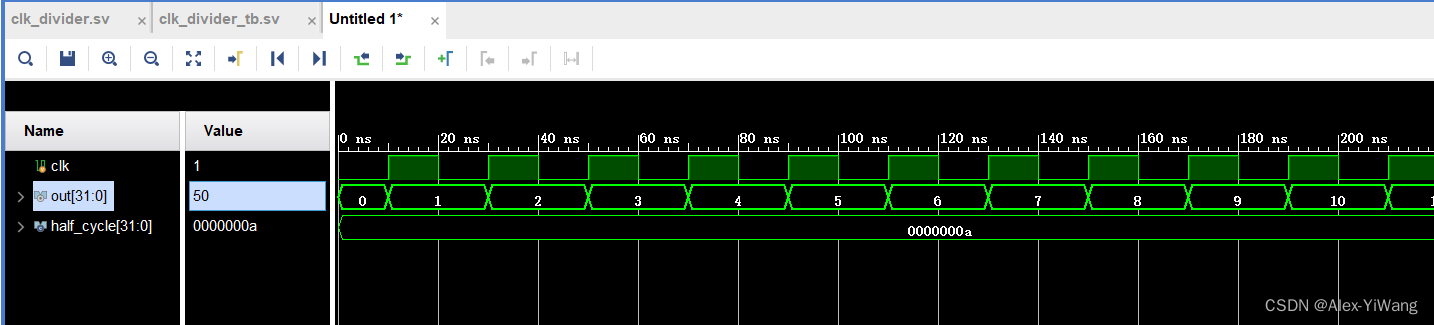

通过仿真波形可以看到,就是简单的计数器原理,之后可以在out输出连接组合逻辑(例如与门)来实现分频操作。 这就是本期的全部内容啦,如果你喜欢我的文章,不要忘了点赞+收藏+关注,分享给身边的朋友哇~ |

【本文地址】

今日新闻 |

推荐新闻 |