vivado DDS IP核参数设置和仿真 |

您所在的位置:网站首页 › dds中文什么意思 › vivado DDS IP核参数设置和仿真 |

vivado DDS IP核参数设置和仿真

|

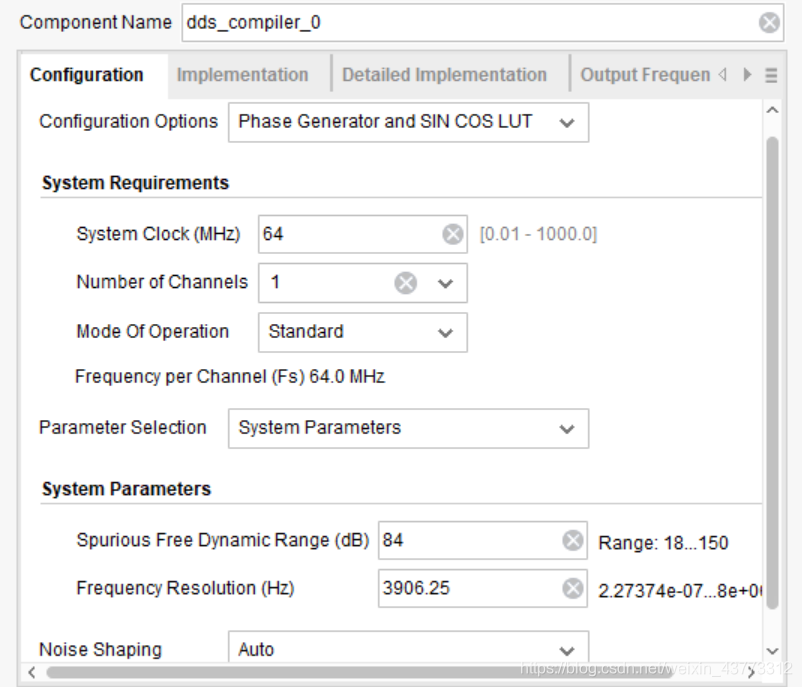

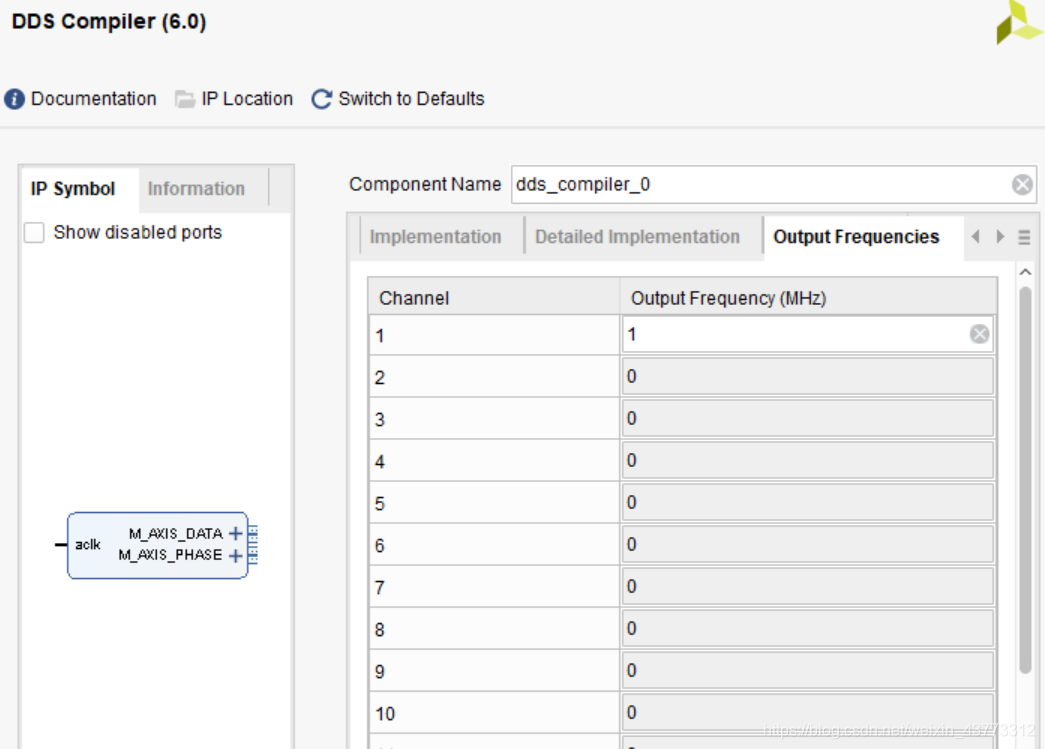

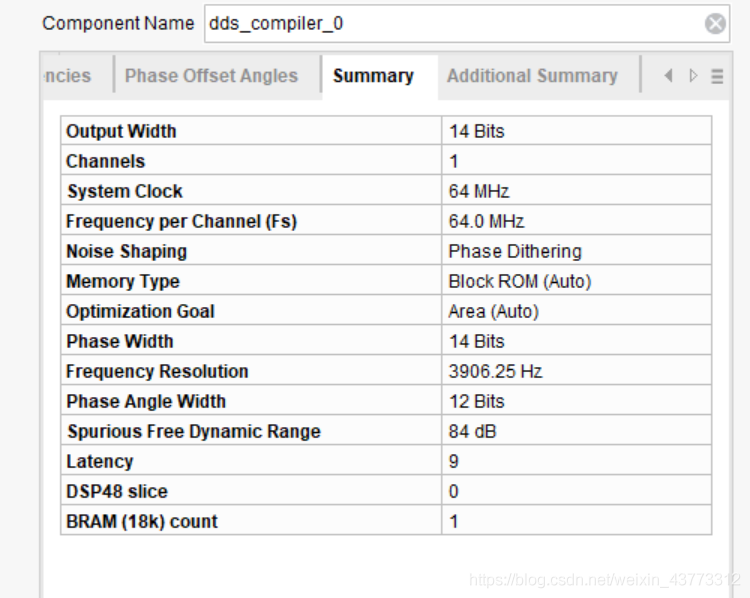

IP核版本 DDS Compiler(6.0) 参考文件:PG141. DOCNEV真的是神器,它能解决你对工具所有的问题。 以生成一个64Mhz时钟驱动,14位带符号位的1Mhz正弦波为例,讲解下DDS核的设置和仿真。 建立DDS IP核 IP Catalog 中搜索DDS, 选择DDS Compilier。 选择 Configuration Options为 Phase Generator and SIN COS LUT. 设置Parameter 参数。 这里参考PG141 SFDR 设置信息为: Implementation 设置 Phase Increment Programmability 设置为Fixed, Phase Offset Programmability设置为Fixed, output Selection设置为Sine.如果在前面设置的是两路输出,则可以选择Sine and Cosine,此时输出的高位为Sine信号,低位为Consine信号(参考PG141 34页Output DATA Channel TDATA Structure) Output Frequencies设置为1MHz 相位偏移设置为0 检查summary 和 Additional Summary 仿真 Vivado生成的例化模板,在IP Source中,Instantiation Template.其中VHDL使用.vho文件,Verilog使用.veo文件。这里可以看到例化模板.veo文件和testbench,DDS核使用的是VHDL语言。在Sources窗口的Hierarchy标签下,在Simulation Sources文件夹中打开IP核的层次结构(这里可能会延迟半天,正常现象)(点击前面的小箭头,或右键->IP Hierarchy->Show IP Hierarchy),TestBench文件名格式为tb_ipname。将该Testbench设置为顶层仿真模块,右键->Set as Top: |

【本文地址】

System Clock 为驱动时钟,设置为64MHz,Number of Channels 为输出的通道数,Mode of Operation选择为Standard。 Parameter Selection 选则为Sytem Parameters。

System Clock 为驱动时钟,设置为64MHz,Number of Channels 为输出的通道数,Mode of Operation选择为Standard。 Parameter Selection 选则为Sytem Parameters。 举例,我这里输出位宽为14,Noise Shaping选择为 Taylor Series Corrected时, SFDR = 6*14-1 = 83 Frequency Resolution设置参考

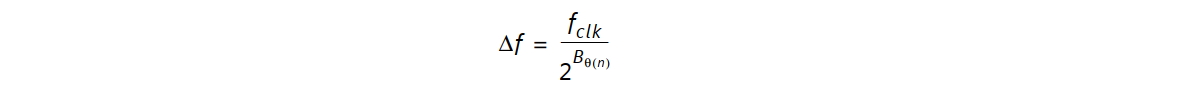

举例,我这里输出位宽为14,Noise Shaping选择为 Taylor Series Corrected时, SFDR = 6*14-1 = 83 Frequency Resolution设置参考  我这里设置的是单通道输出,则单个通道驱动时钟64MHz(若输出SINE和CONSINE信号两个通道,则计算时需要按照每个通道驱动的时钟为Fclk /2计算。) Fr = 64_000_000/2^14 = 3906.25

我这里设置的是单通道输出,则单个通道驱动时钟64MHz(若输出SINE和CONSINE信号两个通道,则计算时需要按照每个通道驱动的时钟为Fclk /2计算。) Fr = 64_000_000/2^14 = 3906.25

检查输出位宽14位,输入时钟64MHz

检查输出位宽14位,输入时钟64MHz  1通道输出时钟为1MHz。

1通道输出时钟为1MHz。 在Flow Navigator 中SIMULATION上右键,simulation settings 设置仿真模式和仿真时长,同时设置仿真顶层文件名称。

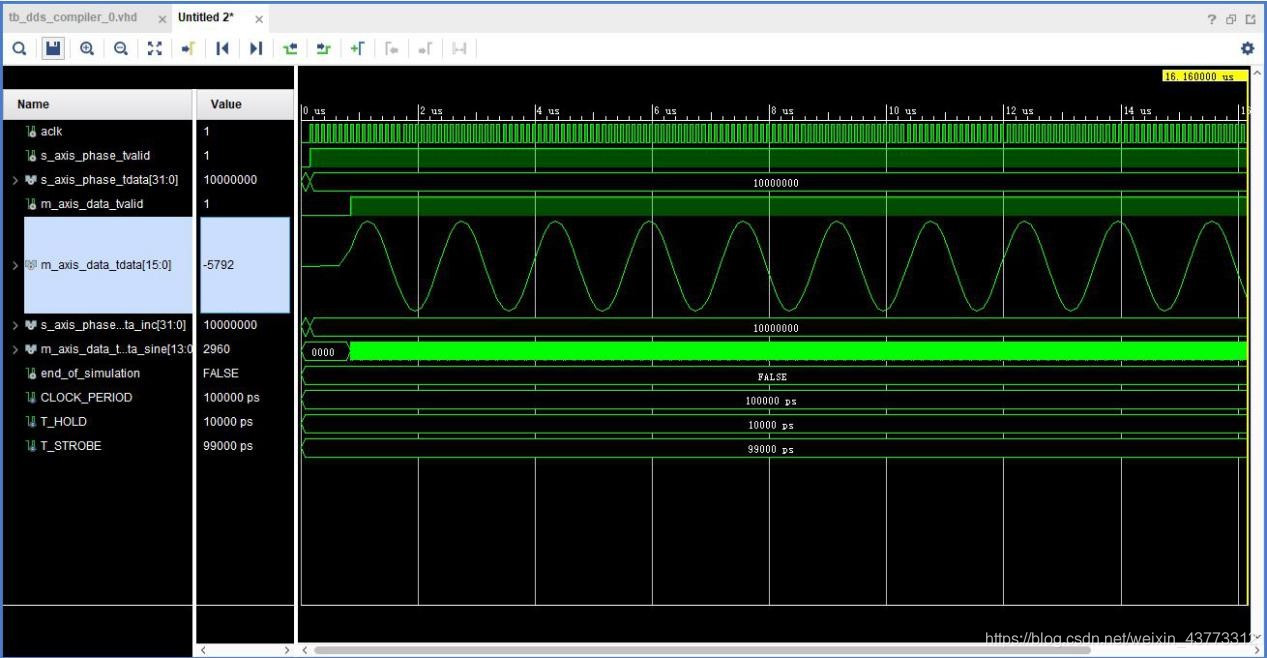

在Flow Navigator 中SIMULATION上右键,simulation settings 设置仿真模式和仿真时长,同时设置仿真顶层文件名称。  然后就可以run simulation了。

然后就可以run simulation了。