如何使DDR4降低系统功耗?要借助POD电平 |

您所在的位置:网站首页 › ddr4芯片功耗 › 如何使DDR4降低系统功耗?要借助POD电平 |

如何使DDR4降低系统功耗?要借助POD电平

|

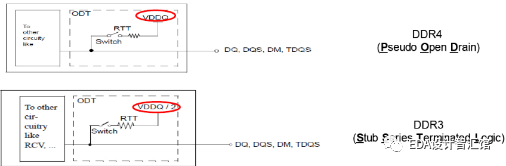

DDR4主要是针对需要高带宽低功耗的场合。这些需求导致了DDR4芯片引入了一些新的特点:它摒弃了上几代内存产品的SSTL电平接口,引用了新的I/O架构POD(Pseudo Open Drain)。这个新的特点,在实际PCB系统的设计中,引入了一些新的设计需求,在后面的一些章节中我们会详细的介绍相关内容。先来看POD输出和上一代DDR3电平接口标准的差异。 在STLL里接收端将信号端接到轨电压的一半(VDD/2),而POD是VDD,如下图

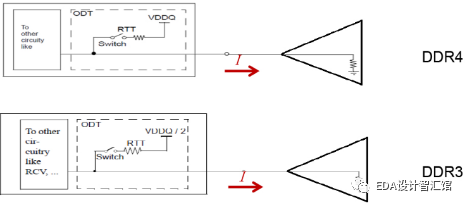

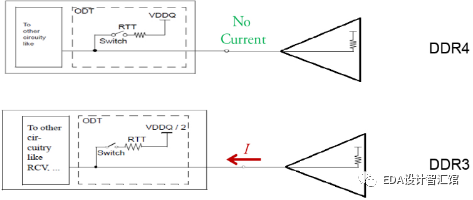

下图为在输出高和低的情况下,DDR4/DDR3的电流流向。当输出为低时,SSTL/POD的都会有电流流过。因为POD是端接到轨电压,而SSTL的端接到轨电压的一半。所以,POD的电流会比SSTL稍大,这个也是为什么DDR4的轨电压选用了一个稍微低一点的电平。

主要的区别在于输出高电平时。SSTL电平将会继续有消耗电流,并且电流大小和输出低电平的时候一致。POD在输出高电平时,没有工作电流。

所以,一个降低DDR4系统功耗的方法是,尽量加大DDR4输出高的数量。这个就是为什么DDR4中多了“DBI管脚”。DBI的全称是Data Bus Inversion数据总线反转/倒置,它与POD电平密不可分,它们也是DDR4区别于DDR3的主要技术突破。 正是由于POD电平的这一特性,DDR4设计了DBI功能。当一个字节里的“0”比特位多于“1”时,可以使能DBI,将整个字节的“0”和“1”反转,这样“1”比“0”多,相比原(反转前)传输信号更省功耗。 举个例子,当8bit lane中有至少有5个DQ都是低时,所有的Bit将会被翻转,并且DBI(Data Bus Inversion)置低,用来指示数据线的反转。通过这个方法,总共9个信号中(8个DQ和1个DBI),总有至少5个是被驱动为高电平。如果原始的数据中有4个或者更多的信号被驱动为高时,那么DBI信号也将会设为高,同样,还是9个里面至少有5个为高。这样的话,在每一个数据传输的过程中,都是至少有5/9的数据是高电平,可以在一定程度上降低了功耗。

|

【本文地址】