德力威尔PCB培训之AM335X之DDR3布局布线指导 |

您所在的位置:网站首页 › ddr3电路 › 德力威尔PCB培训之AM335X之DDR3布局布线指导 |

德力威尔PCB培训之AM335X之DDR3布局布线指导

|

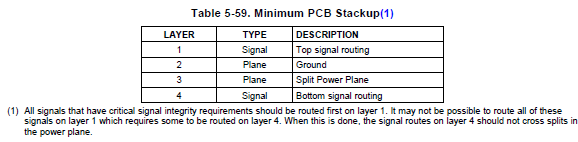

温度:-40℃-95℃ 焊球数量:96 pin 焊球直径:0.5mm 时钟:DDR_CK and DDR_CKn工作的标准速率是303 MHz 二、PCB叠层设计 2.1. PCB叠层 DDR3布线部分至少需要4层板(也可以再额外增加层数,用来布其他的信号线或者增强信号完整性和提高电磁兼容抗干扰能力),优先考虑将信号布在第一层,第一层布不完时可以布在第四层,但第四层的走线不能跨越第三层电源分割面。PCB叠层如下:

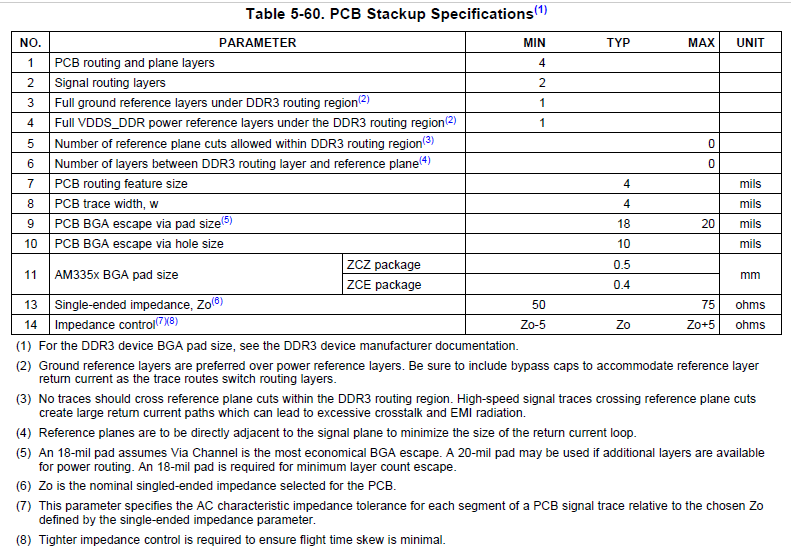

2.2. PCB叠层规则

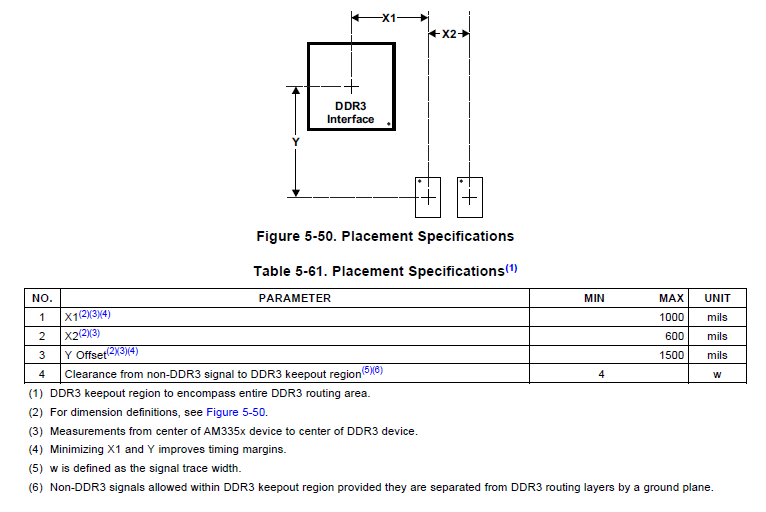

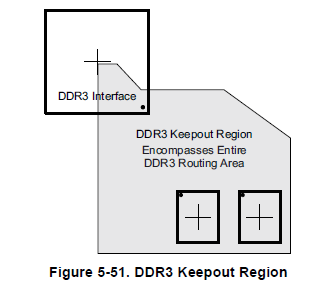

三、CPU和DDR3元件布局方法

四、DDR3布线区域 DDR3布线区域同层内不允许其他非DDR3信号走线,DDR3布线区域的参考平面一定要完整的DDR电源平面或地平面,非DDR3信号可以布在DDR3布线区域下面有完整参考平面隔离的层内。

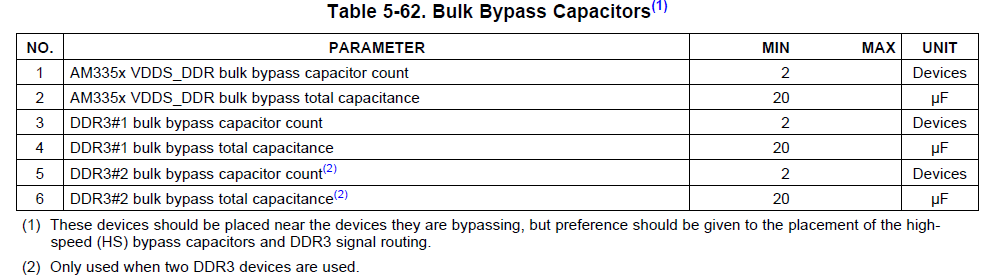

五、大体积高容量旁路电容的使用 CPU、DDR3需要大体积高容量的旁路电容。大体积旁路电容尽量靠近CPU或DDR3的电源引脚。但优先考虑高频旁路电容和DDR信号布局布线,然后再考虑大体积旁路电容。

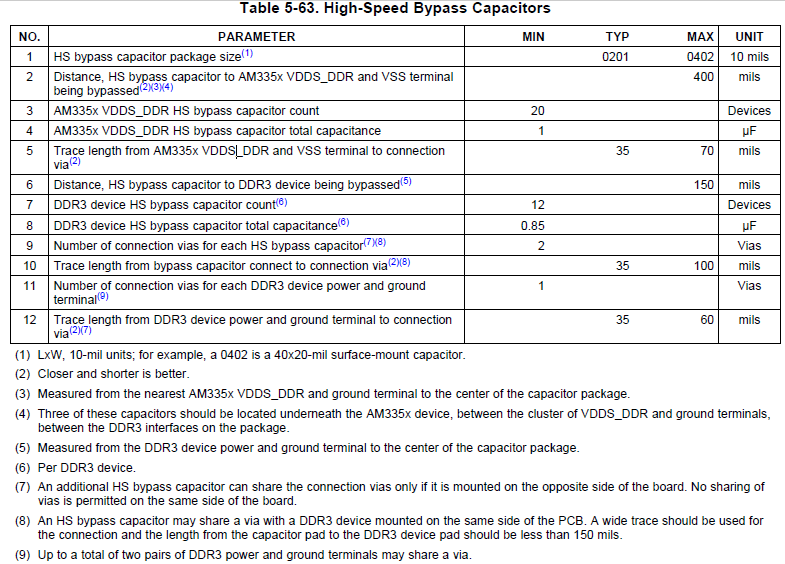

六、高频旁路电容的使用 DDR3的正常运行是离不开高频旁路电容的,并且要尽量减小连接在DDR电源和地之间的高频旁路电容的寄生电感。通常来说,至少做到以下几点是比较好的: 1、安装的高频旁路电容尽可能的多一点; 2、尽量减少旁路电容到需要旁路的CPU或DDR芯片上的电源引脚之间的距离; 3、使用物理尺寸尽量小中容量尽量高的旁路电容; 4、旁路电容打过孔的孔径尽量大,旁路电容焊盘到它的过孔之间的连线尽量要宽; 5、尽量不要多个旁路电容的焊盘共用一个焊盘。 下表是关于高速旁路电容使用注意事项:

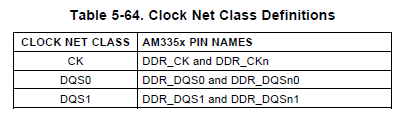

七、DDR3信号网络分组 7.1. DDR3的时钟网络分组:

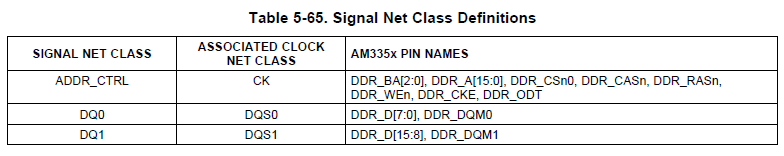

7.2DDR3的信号网络分组:

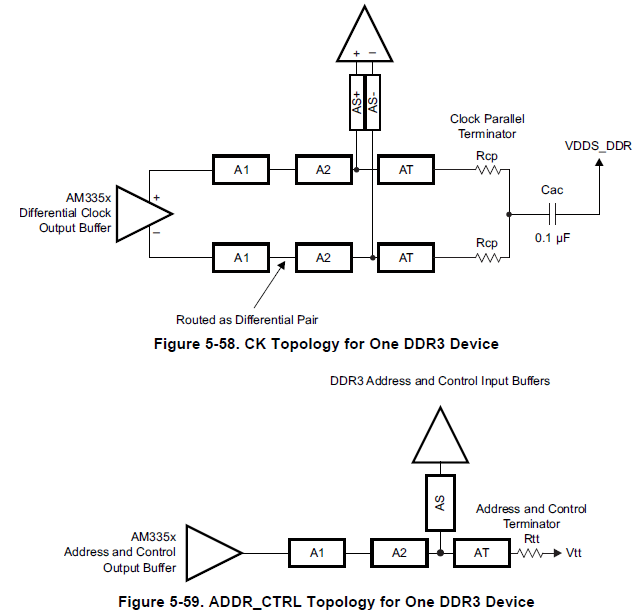

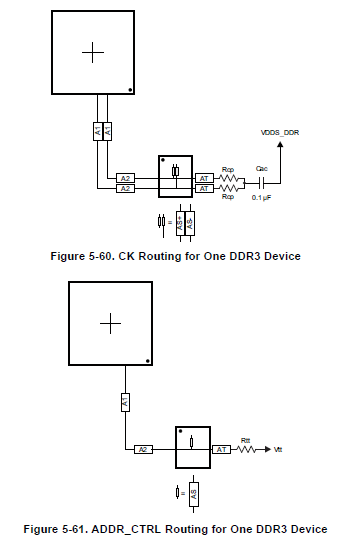

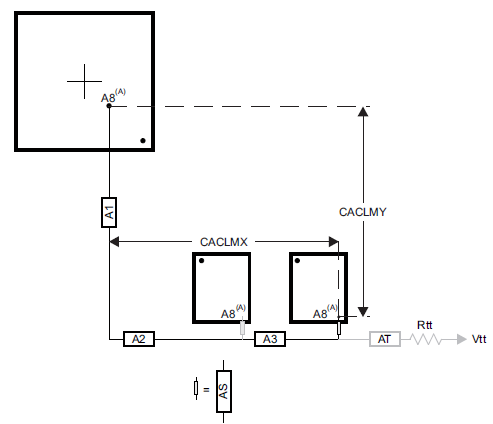

八、DDR3信号终端电阻 本例中DDR3芯片内含有针对DQS[x]和DQ[x]的ODT(片类终结器),而CK和ADDR_CTRL既没有内部的ODT,也没有外接VTT终结器,但这并不影响信号完整性,可以这样应用。 九、DDR3的 DDR_VREF布线 DDR_VREF走线宽度通常为20mil(0.508mm),如果布线空间有限可适当减小宽度。在CPU和DDR的每个DDR_VREF电源引脚附近,就近要放置一个0.1uF的高频旁路电容。 十、DDR3的 CK和ADDR_CTL拓扑和布线规则 10.1. CK和ADDR_CTL拓扑(本例不关注外部终结器,忽略AT、AS走线)

10.2.CK和ADDR_CTL走线(本例不关注外部终结器,忽略AT、AS走线)

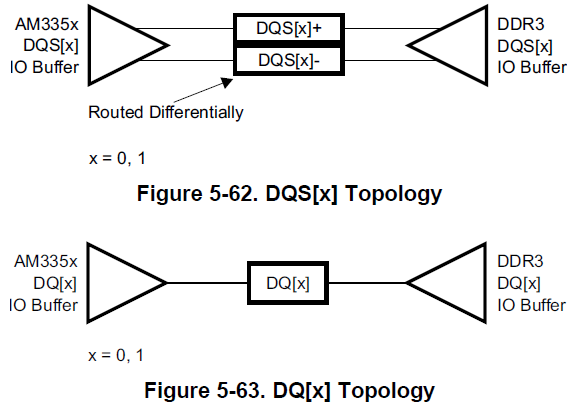

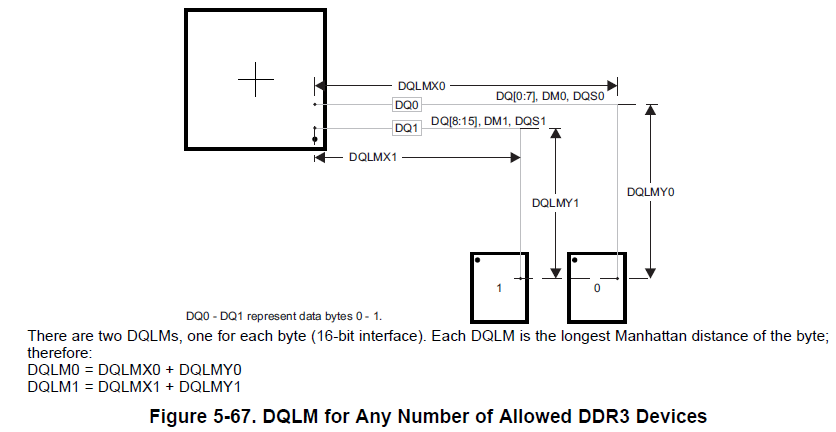

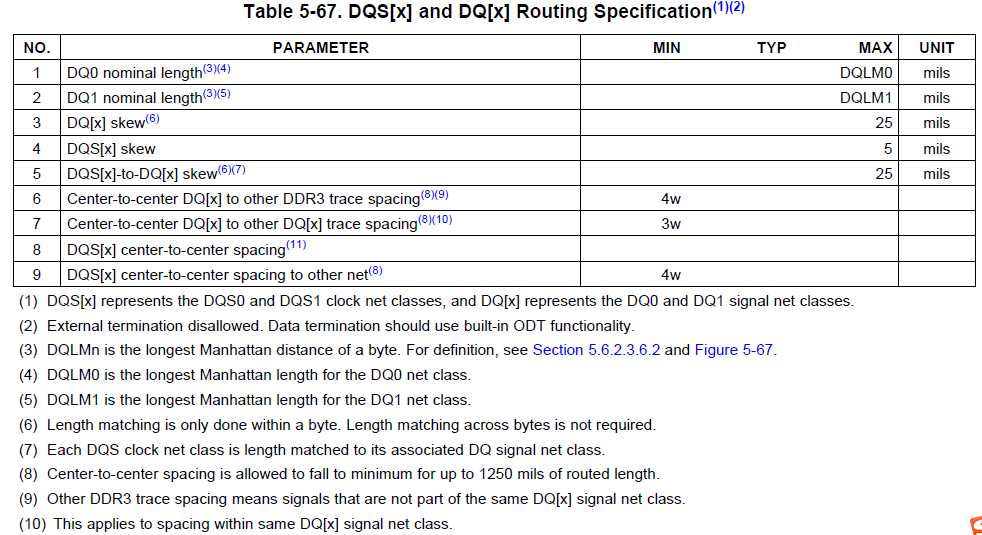

十一、DDR3的数据线拓扑和布线规则 11.1. 数据线拓扑 DQS[x]是点到点的差分信号线,所有DQ[x]是点到点的单端信号线,拓扑如下:

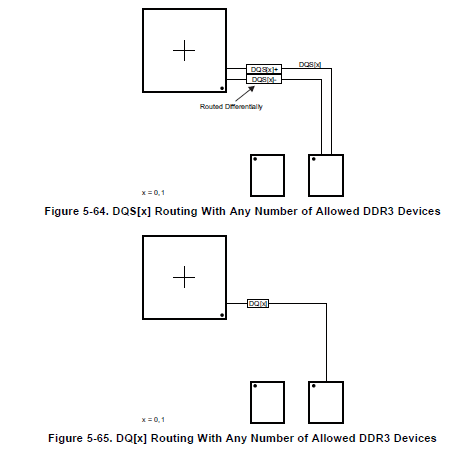

11.2. 数据线布线

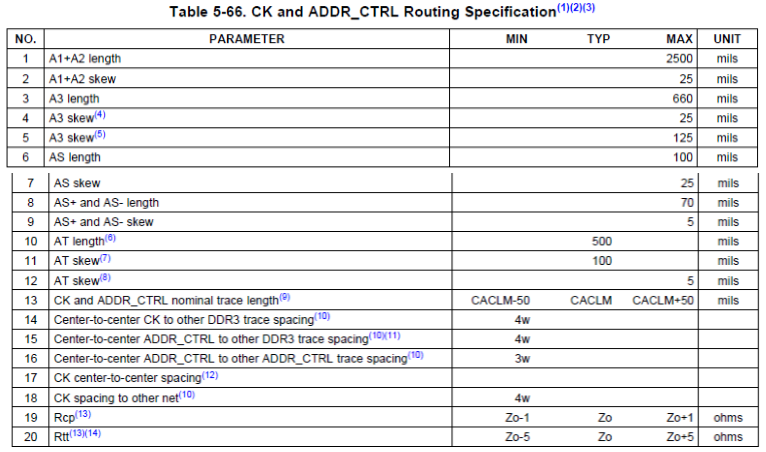

十二、DDR3布线规则 12.1. CK和ADDR_CTL布线规则 CK组内差分线要匹配等长;ADDR_CTL组内的各个信号线要以CK为基础匹配等长; CK和ADDR_CTL走线的最大长度可以采用下图的曼哈顿距离来确定:

几点说明: A、一旦CPU和DDR3的位置固定下来,采用上图中曼哈顿距离确定的布线长度基本上属于最长布线长度了;CK和ADDR_CTL以此线作为基线来匹配长度,尽量减少长度偏移; B、多个DDR3时,接入DDR3的短的树桩线和外接VTT终端的短的树桩线,不包含在长度计算内。 C、最长布线长度计算公式:CALM=CACLMY+CACLMX+300mils;此处额外的300mils作用是:CPU端的走线位置可以比CPU高,向上布一点,DDR3端的线还可以比DDR3低,向下布一点,给布线空间留有充足的余量。 D、下表是CK和ADDR_CTL布线详细规则

备注: (1)CK表示时钟信号网络组,ADDR_CTRL表示地址、控制信号网络组; (2)尽量使用最少数量的过孔; (3)当要在DDR3电源层作为参考平面打过孔换层时,需要添加返回电流旁路电容; (4)镜像放置;一个放置在顶层、一个放置在底层,呈镜像重合状。 (5)非镜像放置:所有的DDR3在同一层; (6)尽量减小走线长度; (7)只针对ADDR_CTRL网络组,建议减小长度偏移,但不是必须的; (8)只针对CK网络组; (9)CACLM是最长的曼哈顿距离; (10)当走线长度超过1250mils时,允许适当减小线中心到线中心的距离; (11)不同DDR3的信号线; (12)CK是差分阻抗,差分阻抗是单端阻抗的2倍; (13)外接的VTT终结器是绝对不允许放置在源端(CPU驱动端)。 12.2. DQS[x]和DQ[x]布线规则 不建议,也不必将所有的数据线匹配等长,但将每1字节的数据匹配等长是必须的。 可用曼哈顿距离确定最长走线长度,

注意:TI官方文档规定了CK时钟线和ADDR_CTRL线匹配等长,DQS[x]与DQ[x]匹配等长,并没有规定CK和DQS[x]匹配等长。据个人设计经验,建议DQS布线长度应小于或等于CK布线长度,最好小于CK布线长度。 德力威尔嵌入式软硬综合技术培训中心 手机:18983773515 QQ/微信:710068499 可进入德力威尔官网获取更多精彩内容! Copyright@德力威尔&王术平返回搜狐,查看更多 |

【本文地址】