驱动DDR3 |

您所在的位置:网站首页 › ddr3存储器工作原理 › 驱动DDR3 |

驱动DDR3

|

文章目录

一、驱动DDR3原理1、储存介质扫盲2、时间参数

二、IMX6U MMDC控制器DDR的初始化与测试

一、驱动DDR3原理

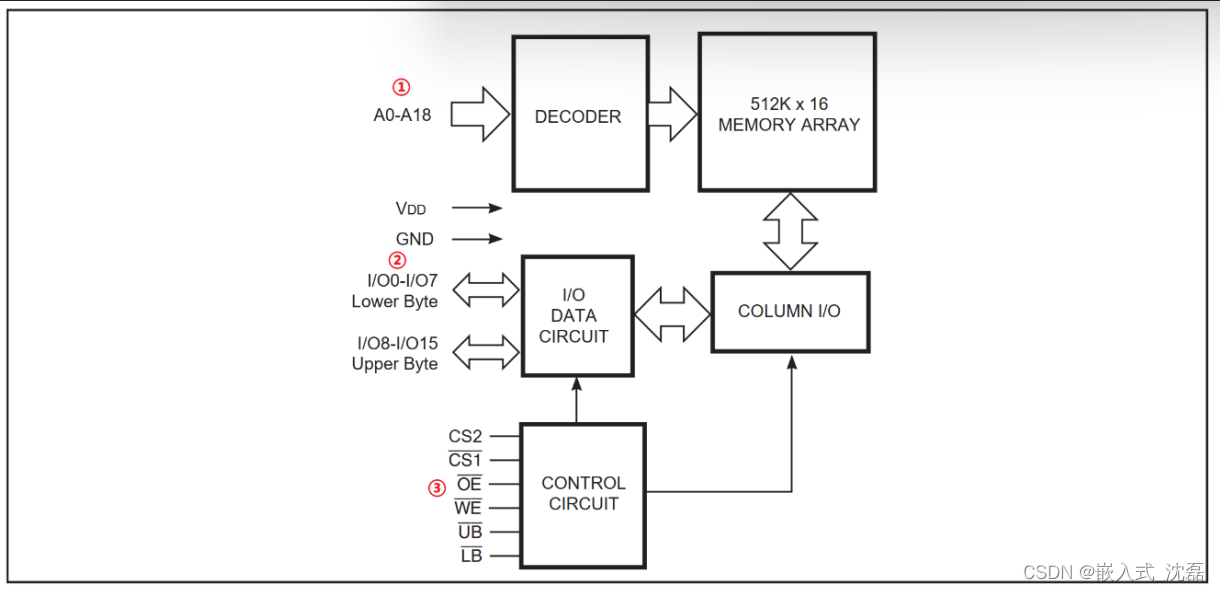

我的IMX6ULL的内部RAM只有128KB,外部的DDR3应该有512MB 型号为IS62WV51216:16位宽的1MB SRAM

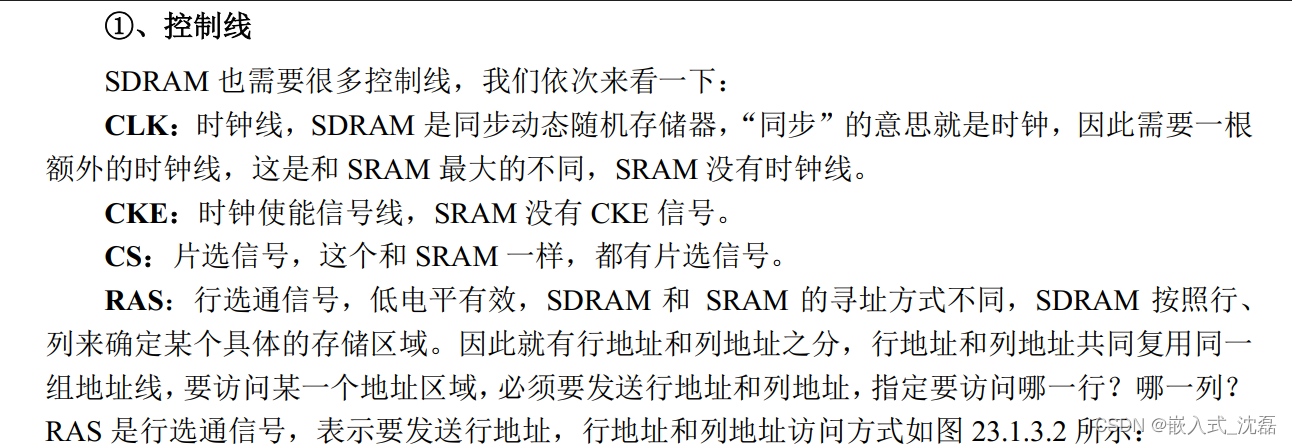

首先RAM,ROM,我们简单的清楚他是随机存储器、只读存储器 内存条、SRAM、DDR这些都是RAM 但是这个ROM“只读存储器”已经不是定义特别准确了 为什么呢?因为Flash、EMMC什么的这些ROM都是可以进行写操作的 SRAM这个是什么的意思呢,“静态RAM”,这种一般是外部扩展的 所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持 价格昂贵,容量小,但速度快!一般用作内部SOC的cache使用 DRAM就是动态RAM了 那么SRAM和DRAM最本质区别是什么呢? 首先他们两个都是断电丢失数据 区别在于:SRAM有供电不进行周期性的刷新仍能保持数据 但是DRAM必须还要保持周期性刷新才能保持数据 后面有发展出SDRAM更高级的RAM 后面有发展出SDRAM,“同步动态RAM” SDRAM在DRAM的基础上增设了“同步机制”,也就是需要时钟线 他跟DRAM一样是需要周期性刷新才能保持数据 DDR4\DDR3这些就是SDRAM

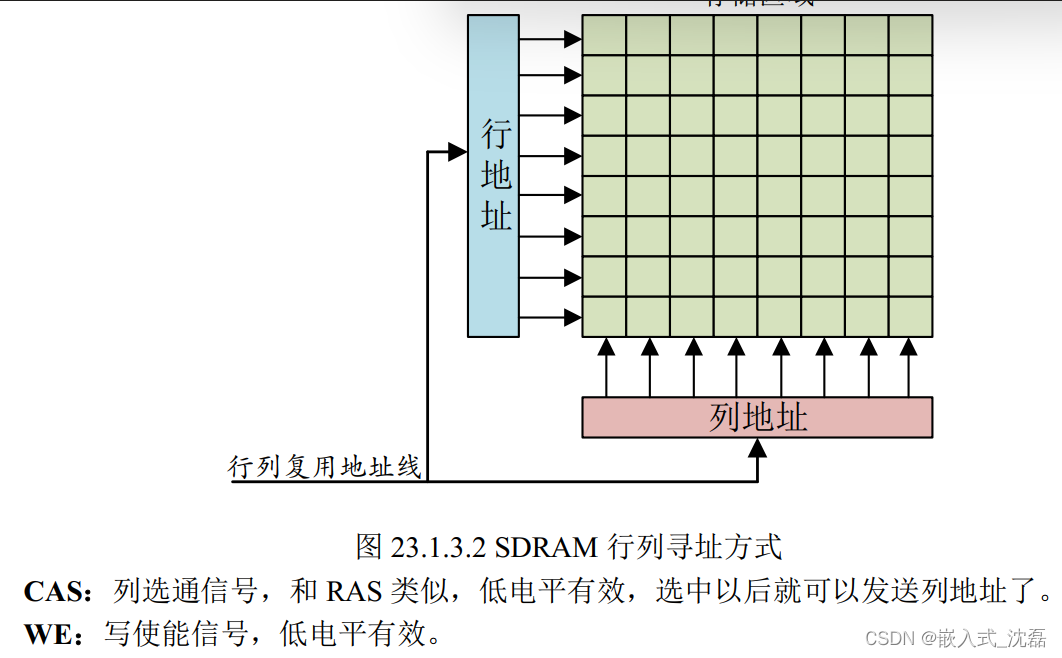

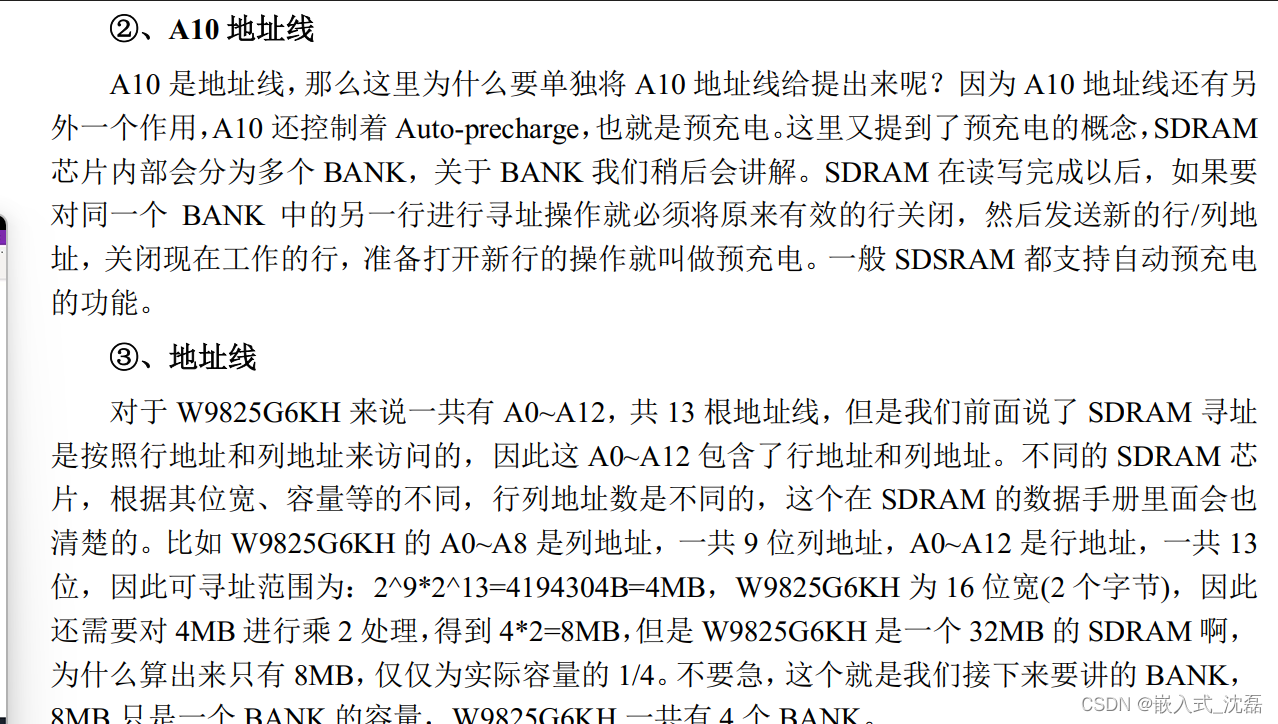

地址线: A0 ,A1~A12, 为什么要把A0单独列出来呢,因为A0有一个预充电的功能

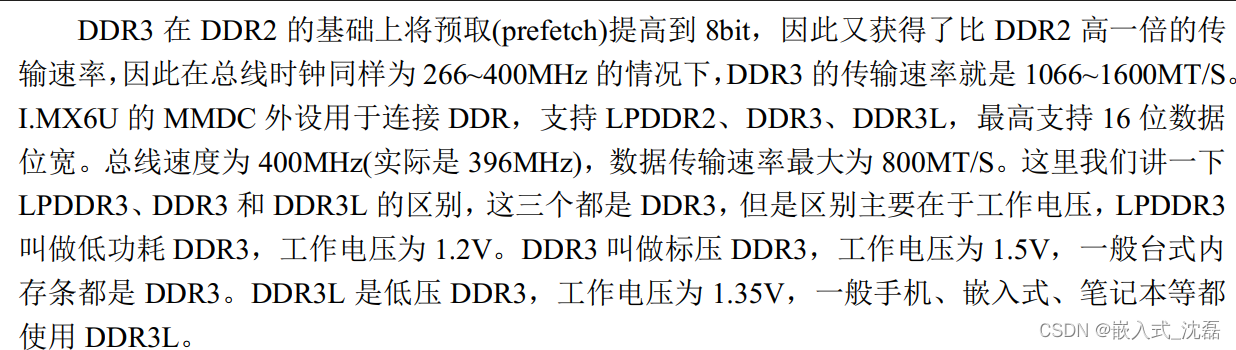

这个芯片有4个BANK BANK选择线:BS0,BS1 来选取四个不同的BANK 数据线:有多少位宽就有多少根数据线嘛 高低字节选择:LDQM,UDQM DDR:DDR 全称是 Double Data Rate SDRAM,也就是双倍速率 SDRAM 变快的原因:增加预取 DDR每一代更新速度就会提升一倍,DDR2比DDR1快一倍,DDR3比DDR2…

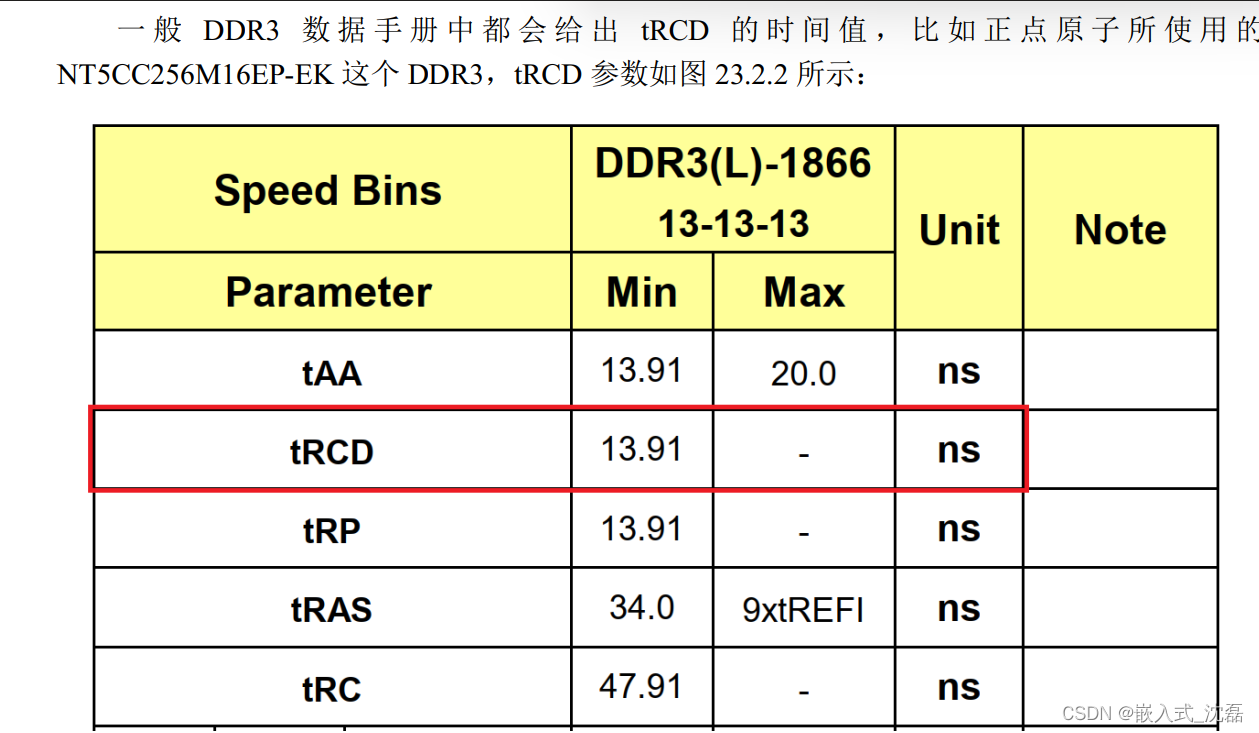

1、传输速率 DDR3 1600\DDR3 1866\DDR4 2400\DDR4\3200MTS实际上我们的DDR3到不了1866,因为6ULL的性能受限,只能到800左右 2、tRCD 行地址到列地址的延时

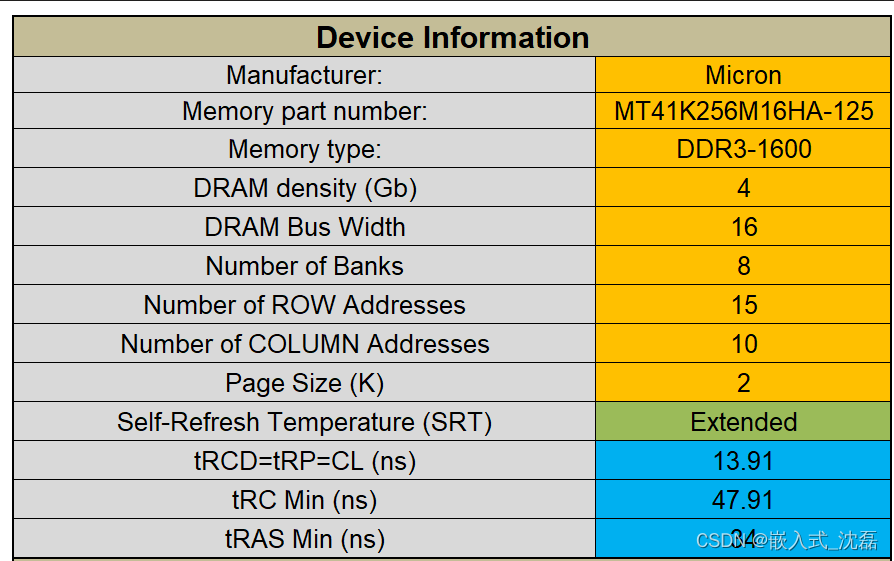

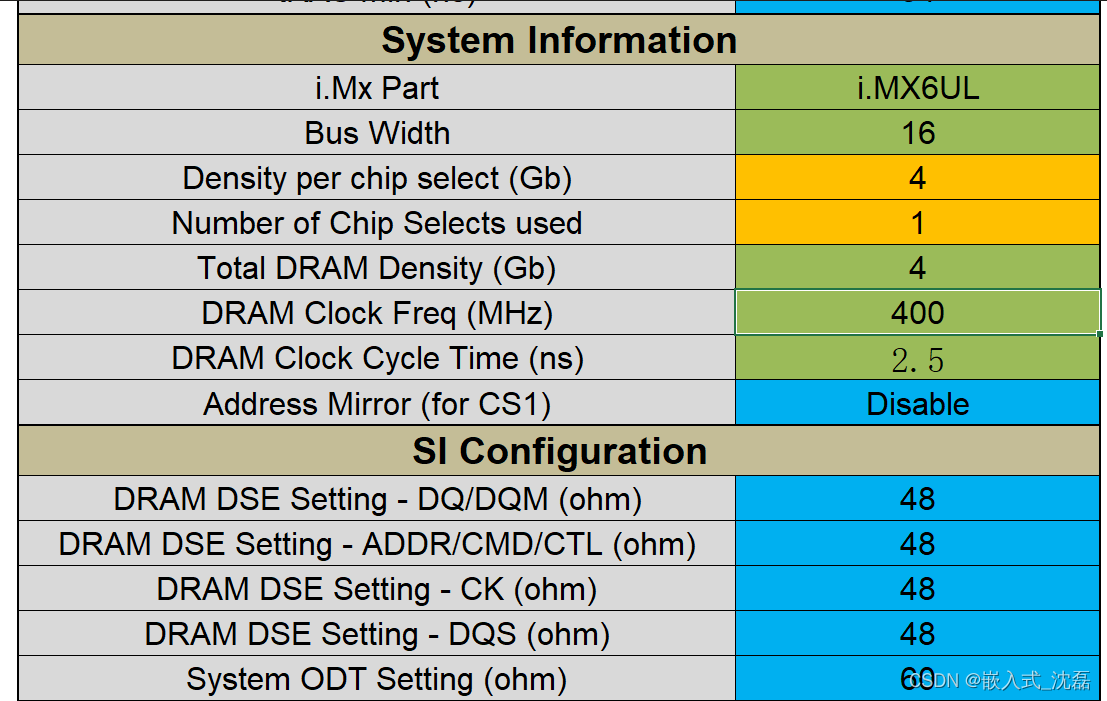

3、CL参数 列地址选通潜伏期 4、AL参数 目的为了解决指令冲突 5、tRC参数 tRC 是两个 ACTIVE 命令,或者 ACTIVE 命令到 REFRESH 命令之间的周期 6、tRAS参数 tRAS 是 ACTIVE 命令到 PRECHARGE 命令之间的最小时间 NT5CC256M16EP-EK 的 tRAS 值为 34ns 二、IMX6U MMDC控制器多模支持DDR/DDR3L LPDDR2 X16 BIT MMDC最高支持DDR,频率最高支持400MHZ

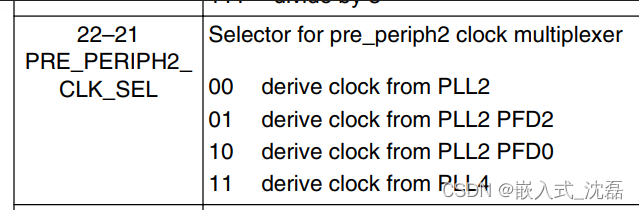

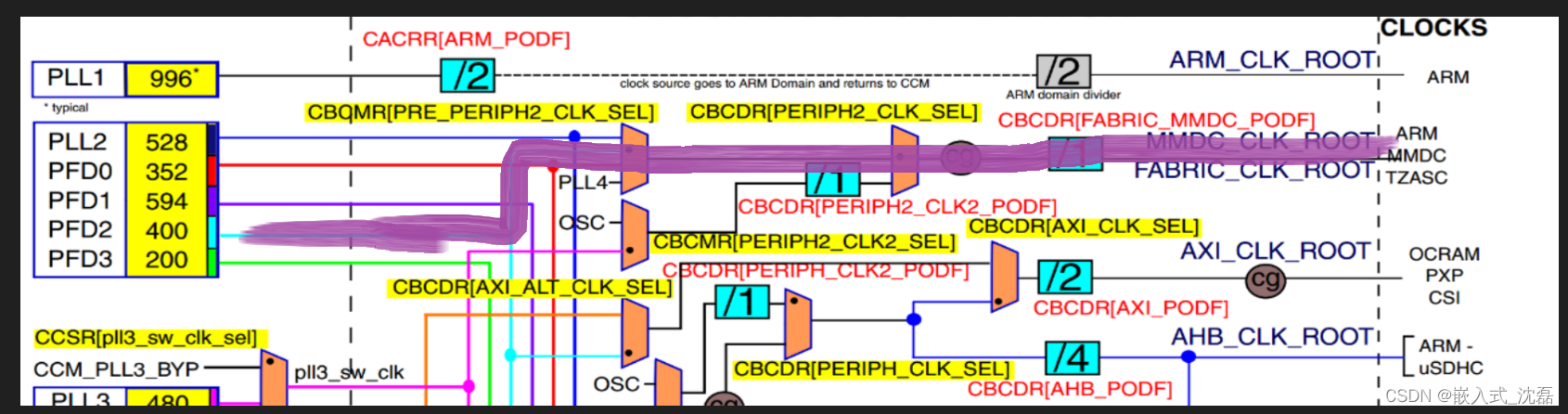

6ULL给DDR提供了专用的DDR IO引脚,这个引脚是不能复用的!!! DDR的时钟配置: 他的时钟是由IMX6U来提供的MMDC_CLK_ROOT 使用的路线:PLL_2 _PFD2 = 396MHZ,且在前面例程已经设置 CBCMR的PRE_PERIPH2_CLK_SEL设置01,选择时钟源位PLL2 PFD2

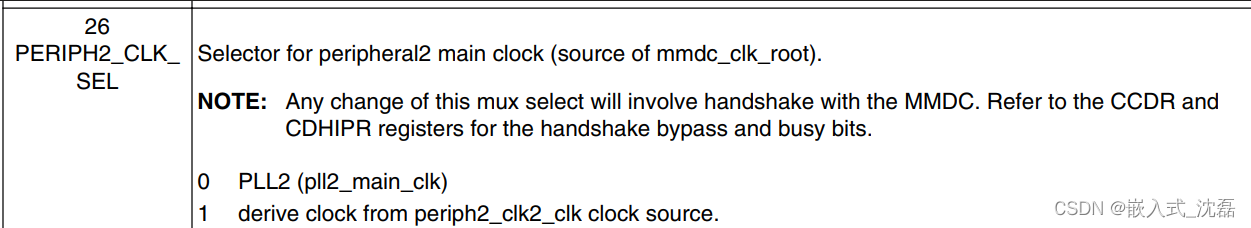

CBCDR的PERIPH2_CLK_SEL,也就是bit26为0,此时进来的时钟就是396MHZ

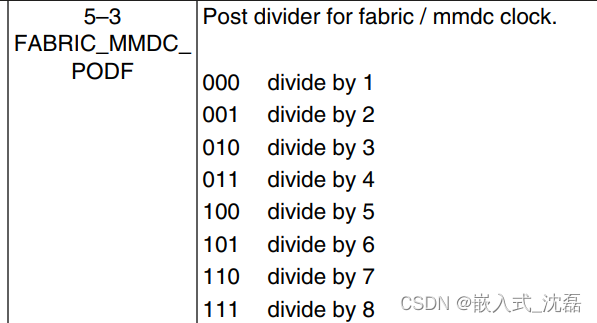

CBCDR的FABRIC_MMDC_PODF设置为0,取得1分频

1、DDR_STRESS_TESTER配置文件 其实是一个excel配置文件,配置好后realview.inc会同步更新

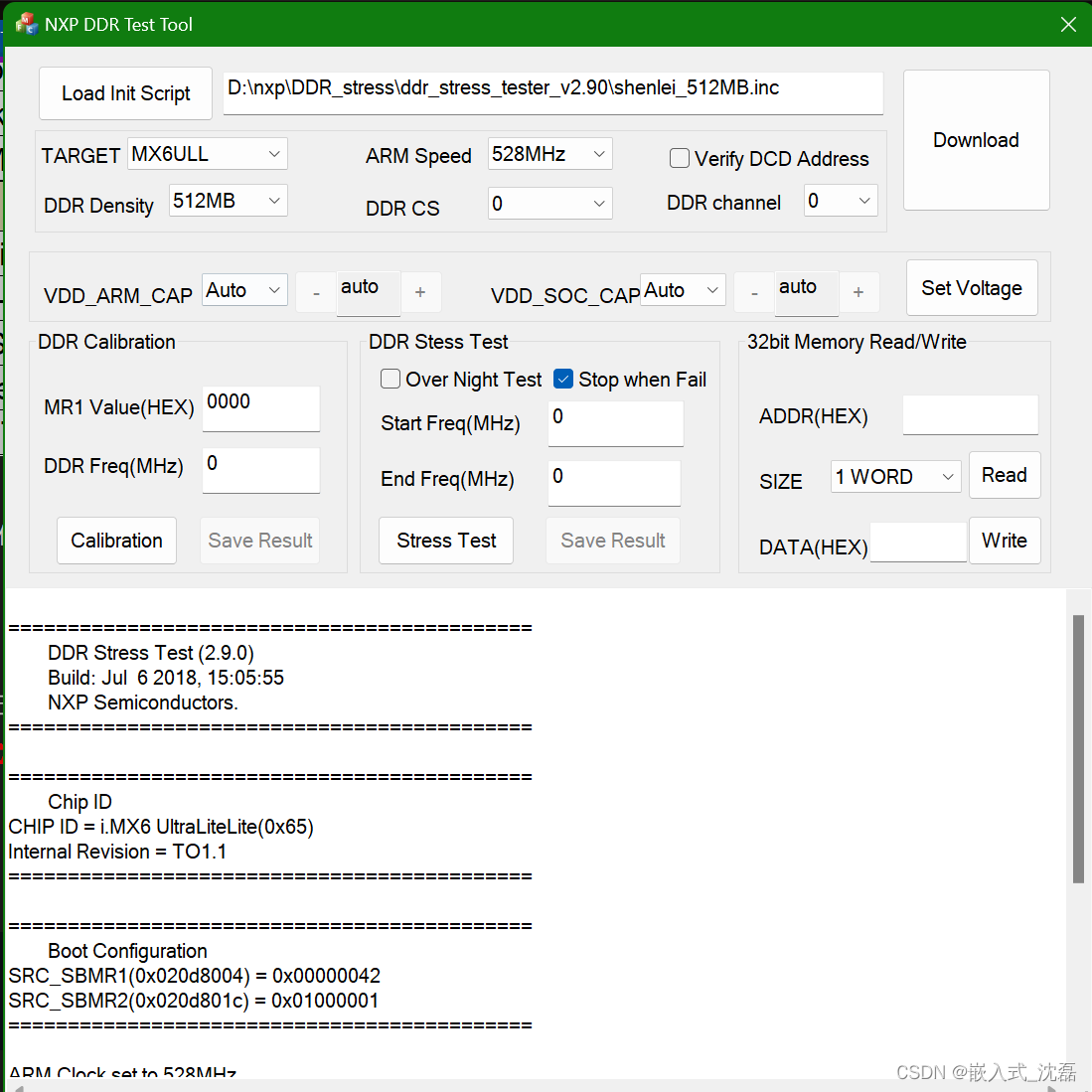

2、inc文件 Ddr_stress_tester工具需要用到.inc文件 3、测试 Ddr_stress_tester通过USB口将inc的配置信息下载到开发板里面 别忘记调整拨码开关到串行下载模式,且SD卡弹出 且USB连接到USB-OTG

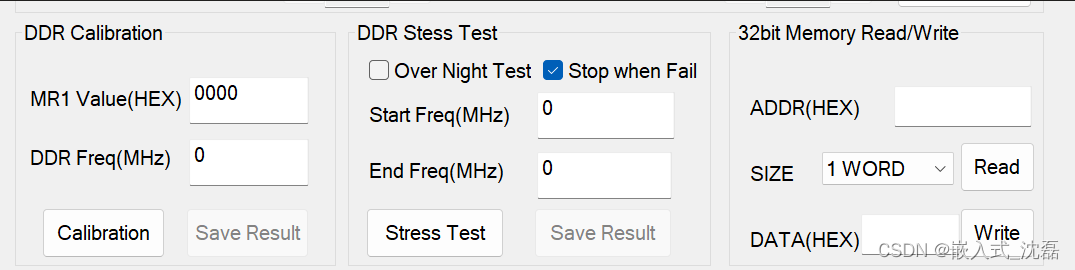

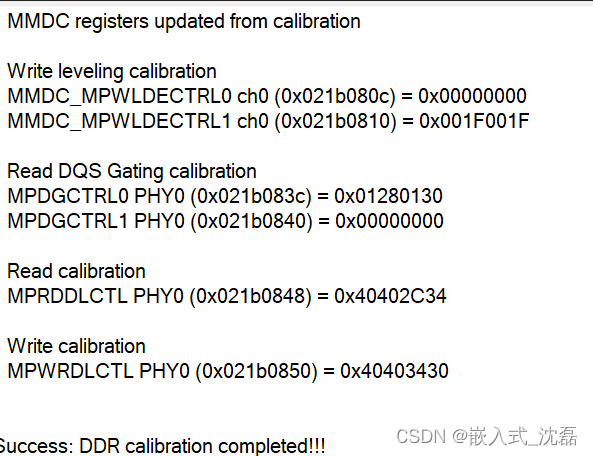

分别是DDR校准、DDR压力测试、32位读取 直接进行超频测试会失败,必须先进行校准 校准会时间比较久,校准完的值我们要修改到inc文件中去

如果使用的不是教程系列的开发板,一定要修改imxdownload.h的寄存器值,不然配置错误!!! |

【本文地址】