Nand Flash时序图怎么读? |

您所在的位置:网站首页 › daned怎么读 › Nand Flash时序图怎么读? |

Nand Flash时序图怎么读?

|

SSD | 怎么看时序图—nand flash的读操作详解?

概述操作详解分解CE写数据时序写命令锁存时序地址锁存时序相对复杂一些的时序

读操作时序

总解写操作时序

参考文章

本文总结Nand Flash的读操作的分解和总解。

概述

不同的芯片操作时序可能不同,读的命令也会有一些差别。 某些Nand Flash内部集成了控制器外设 (Flash Channel Controller (FCC)),具体到读写操作的细节时序(比如CLE/ALE的set up,写脉冲的宽度,数据的建立和保持时间等)由FCC完成,工程师需要做的基本就是设置几个时间参数。 举例说明,比如写命令,只要写个命令到相应寄存器中,CPU内部就会协调各个引脚来发出相应的信号把这些写命令、写地址、等待操作等步骤组合起来,来实现写命令的操作。 如果没有集成FCC,则需要工程师自己来写时序操作。 操作详解这里以写命令为例介绍写命令是怎么实现的: 分解 CECE(Chip Enable, 片选)Nand Flash,因为选中芯片才能让它工作。 Nand Flash是通过ALE / CLE的电平高低来区分数据线上的数据种类(高电平有效): 命令(CLE有效, ALE无效)地址(ALE有效, CE无效)数据(CLE/ALE都无效): 写数据时序 写命令锁存时序既然数据种类是写命令,则CLE有效(高电平),ALE无效(低电平),如下图的I/Ox Command部分。 并且写给Nand Flash的话肯定有一个写周期(Write Cycle)(需要注意地是,写是在上升沿有效还是下降沿有效。) 数据种类是写命令,即重点关注CLE有效(高电平)期间,ALE此时是低电平(ALE无效)所以可暂时忽略。 CLE为低电平的时期,其他大部分引脚上都是灰色的阴影, 即不需要关心这段时期的这些引脚的电平。 nWE在低电平有效,但并不是说nWE一变成低电平,命令就被锁存了(即真正获得命令),而是在nWE的上升沿时有一个贯穿所有其他引脚时序的竖线,即写入的数据(命令也是数据,只是可以通过CLE有效与否来区分)生效。 txxx是箭头两边所指的两条竖线之间的时间(信号的跳变沿)。 CLE中tCLS与tCLH分别代表CLE set up和CLE hold的时间。 nWE的上升沿有一个最长贯穿其他信号线的竖线,它指示数据(命令也是数据)是在上升沿被锁存的,即写到数据线上的命令数据才真正被锁存(接收),但是CLE信号在nWE上升沿之前就有效了。故,在命令数据被真正锁存之前,CLE有效的那段tCLS时间叫做CLE set up。 nWE上升沿后,命令数据已被锁存(接收),这时CLE可以变为无效了,但并未立刻被变为无效,而是经历tCLH时间之后才结束,则称这段时间为CLE保持时间。 nCE:tCS表示Chip Enable(片选)信号建立时间,tCH表示Chip Enable信号保持时间 I/Ox:tDS表示数据建立时间,tDH表示数据保持时间 地址锁存时序既然数据种类是写地址,则ALE有效(高电平),CLE无效(低电平),如下图的I/Ox Command部分。 地址周期通常需要好几个,即一个地址是分几次发送的。 数据种类是写地址,即重点关注ALE有效(高电平)期间,CLE此时是低电平(ALE无效)所以可暂时忽略。 nWE在上升沿,有一个贯穿所有其他引脚时序的竖线,即先写入的数据(数据是地址,只是可以通过ALE有效与否来区分)是上升沿有效。 CLE无效,所以无需关注tCLS nWE的上升沿有一个最长贯穿其他信号线的竖线,它指示数据(也就是地址)是在上升沿被锁存的,即写到数据线上的地址数据才真正被锁存(接收),但是ALE信号在nWE上升沿之前就有效了。故,在地址数据被真正锁存之前,ALE有效的那段tALS时间叫做ALE set up。 nWE的一个下降沿周期,即一个写周期的时间tWC [write cycle]; 一个下降沿到上升沿,即低电平持续时间,即写脉冲宽度tWP [write pulse]; 一个上升沿到一个下降沿,即高电平持续时间,即tWH [write hold] nCE:tCS表示Chip Enable(片选)信号建立时间,tCH表示Chip Enable信号保持时间 I/Ox:tDS表示数据建立时间,tDH表示数据保持时间 信号的建立和保持时间都是以数据被锁存为分界点,即nWE的上升沿 相对复杂一些的时序

TRC: nRE的一个下降沿周期,即一个读周期的时间tRC[read cycle]; TREA: 起始时间到结束时间,指的是从读信号有效到数据被读之间的时间(RE access) TRHZ: 从RE无效(高电平)到数据线变成高阻态之间的时间(数据线画在中间表示的是高阻态)(RE high to output High Z) 读操作时序

3.1 从对应的R/B是数据线上可以看到时间t内它为低电平,即指示现在CPU处于忙碌状态中,正在处理命令,即定位到1.2中的地址读数据到内部寄存器中,还未准备好数据输出。 3.2 从对应的R/B是数据线上可以看到时间t后它为高电平,即命令已处理完毕,数据被读出。 读出目标数据后,暂时不再需要Nand Flash,所以需要取消片选信号以上步骤的具体时序,CPU中的Nand Flash Controller会帮我们完成,但前提是我们所需要时间参数已设置完成。 那么,需要设置的时间参数有哪些呢? 总解 写操作时序

TACLS表示的是CLE/ALE有效到WE变成低电平之间的时间,但WE只有在上升沿才锁存命令/地址。 TWRPH x TWRPH0代表的是WE的脉冲宽度,即有效时间 TWRPH1代表的是CLE/ALE的保持时间

命令和地址锁存时的时序,和,数据读取和写入的时序,需要的时间参数是一样的。 所以,从Nand Flash中找一个命令时序来对照就好了。

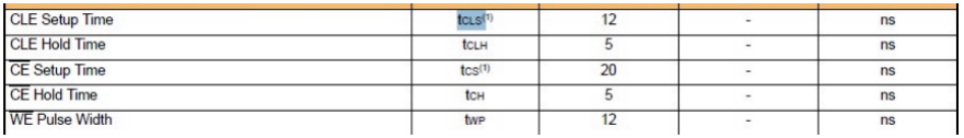

手册中会对tWP , tCLH , tCLS 还会至少给需要的最小时间 比如Nand Flash是手册中这3个参数要求是: 怎么看时序图–nand flash的读操作详解 |

【本文地址】

今日新闻 |

推荐新闻 |

I/Ox信号线的状态,指示了读操作需要哪些单元步骤:

I/Ox信号线的状态,指示了读操作需要哪些单元步骤: 命令和地址锁存时的时序

命令和地址锁存时的时序 数据读取和写入的时序

数据读取和写入的时序

可以得到如下的关系: TWRPH0 = tWP TWRPH1 = tCLH TACLS = tCLS - tWP

可以得到如下的关系: TWRPH0 = tWP TWRPH1 = tCLH TACLS = tCLS - tWP 即, TWRPH0 = tWP >=12ns TWRPH1 = tCLH >=5ns TACLS = tCLS - tWP >=0

即, TWRPH0 = tWP >=12ns TWRPH1 = tCLH >=5ns TACLS = tCLS - tWP >=0