计算机组成原理(微课版) |

您所在的位置:网站首页 › cpu组成中不包括 › 计算机组成原理(微课版) |

计算机组成原理(微课版)

|

6.2 选择题

(1)[2010] 下列寄存器中,汇编语言程序员可见的是 。

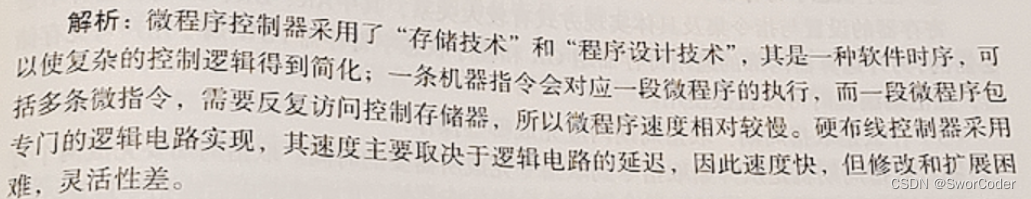

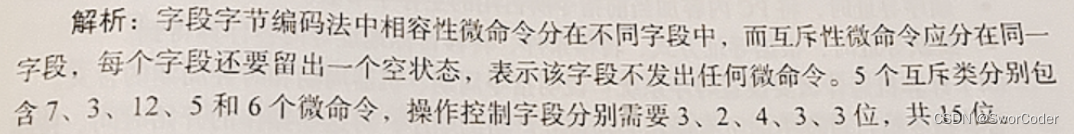

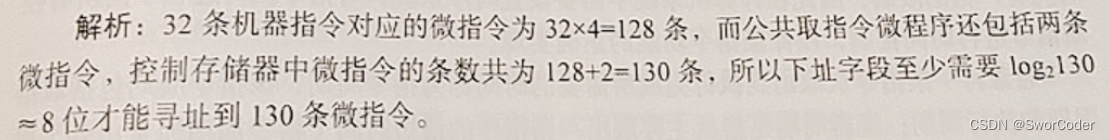

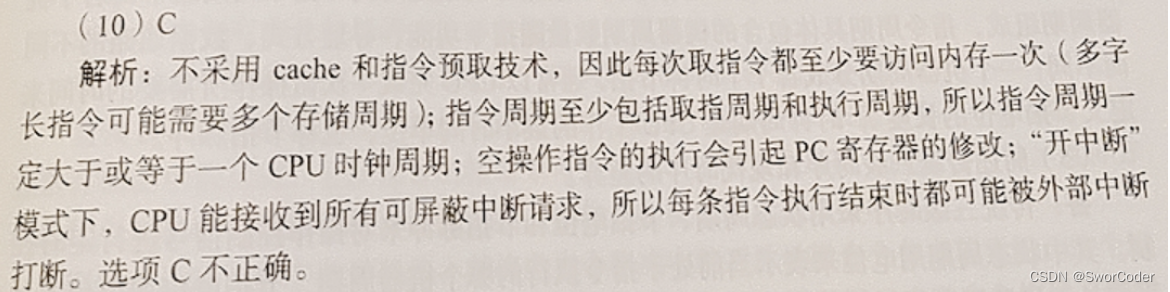

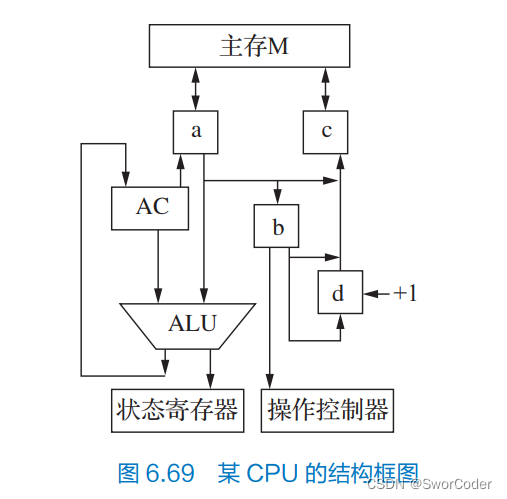

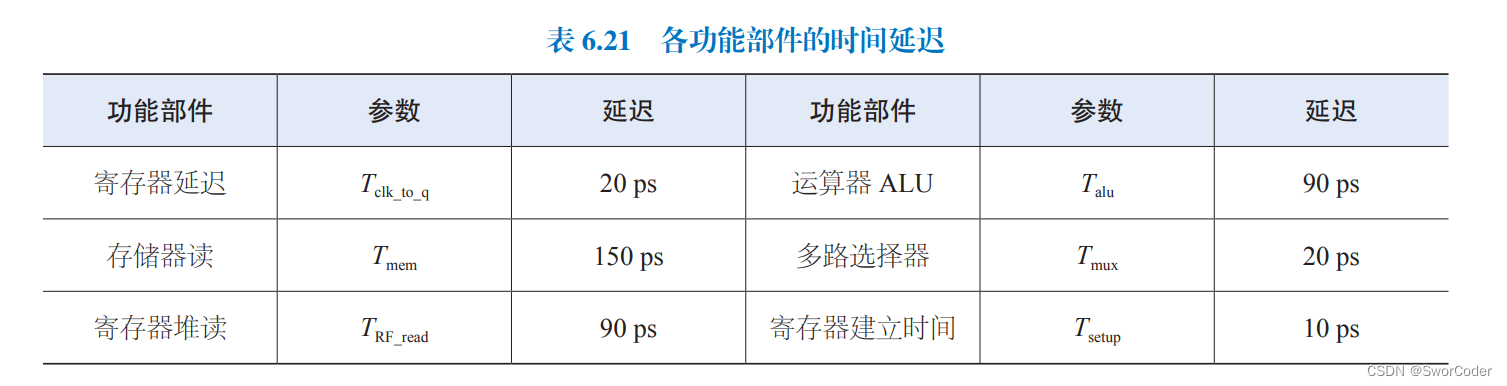

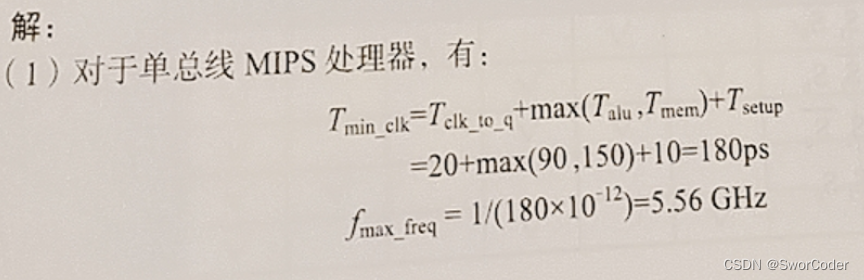

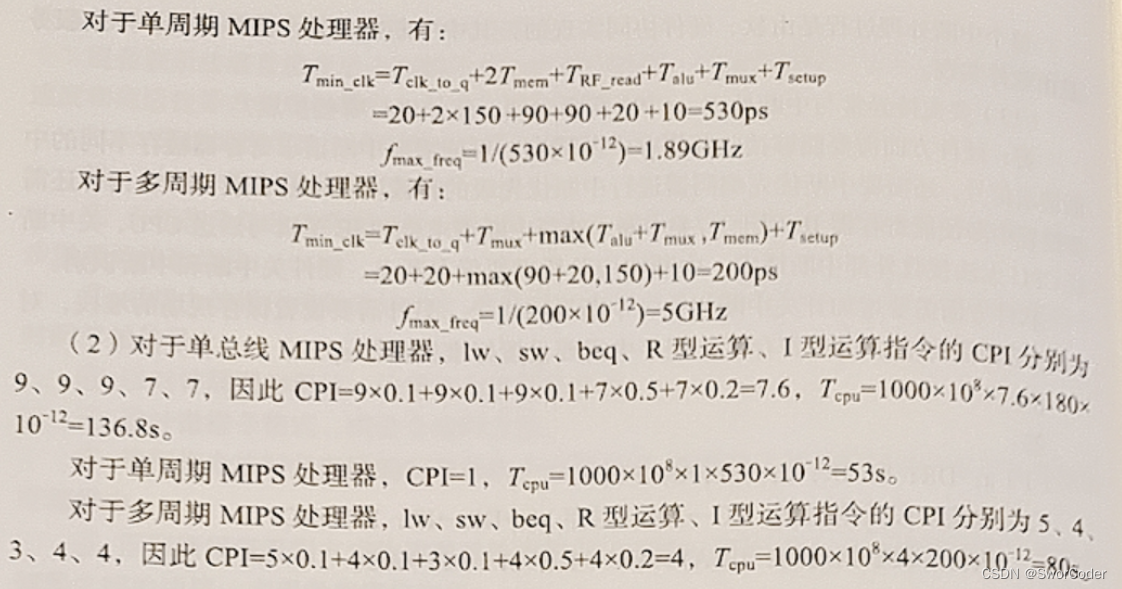

A.存储器地址寄存器(MAR) B.程序计数器(PC) C.存储器数据寄存器(MDR) D.指令寄存器(IR) 答案:B 解析: 一般来说,高级语言程序员能看到的是通用寄存器,而汇编语言程序员能看见的是程序计算器PC。 (2)[2019] 某指令功能为 R[r2] ← R[r1]+M[R[r0]],其两个源操作数分别采用寄存器、寄存器间接寻址方式。对于下列给定部件,该指令在取数及执行过程中需要用到的是 。Ⅰ.通用寄存器组(GPRs) Ⅱ.算术逻辑单元(ALU) Ⅲ.存储器(Memory) Ⅳ.指令译码器(ID) A.仅Ⅰ、Ⅱ B.仅 I、Ⅱ、Ⅲ C.仅Ⅱ、Ⅲ、Ⅳ D.仅Ⅰ、Ⅱ、Ⅳ 答案:B 解析: A.30、30 B.30、32 C.32、30 D.32、32 答案:B 解析: IR位宽与指令字长相同,由于是采用 32 位定长指令字格式,那么IR是32位; A.时钟脉冲信号由机器脉冲源发出的脉冲信号经整形和分频后形成 B.时钟脉冲信号的宽度称为时钟周期,时钟周期的倒数为机器主频 C.时钟周期以相邻状态单元间组合逻辑电路的最大延迟为基准确定 D.处理器总是在每来一个时钟脉冲信号时就开始执行一条新的指令 答案:D 解析: A.可以采用单总线结构数据通路 B.处理器时钟频率较低 C.在指令执行过程中控制信号不变 D.每条指令的 CPI 为 1 答案:A 解析: A错误,解释:为什么单周期处理器不可以采用单总线数据通路? - 来君见我的回答 - 知乎; 时钟频率 = 1 / 时钟周期 = 1,因为每条指令的CPI为1,要考虑比较慢的指令,所以处理器的时钟频率较低,B正确; 同一个时钟周期内,控制信号是不变的,一条指令一个时钟周期,所以执行过程中控制信号不变,所以C正确; CPI为执行一条指令所需要的时钟周期数,该题目中所有指令的指令周期为一个时钟周期,那么CPI为1,D正确。 (6)[2017] 下列关于主存(MM)和控制存储器(CS)的叙述中,错误的是 。A.MM 在 CPU 外,CS 在 CPU 内 B.MM 按地址访问,CS 按内容访问 C.MM 存储指令和数据,CS 存储微指令 D.MM 用 RAM 和 ROM 实现,CS 用 ROM 实现 答案:B 解析: A.指令执行速度慢,指令功能的修改和扩展容易 B.指令执行速度慢,指令功能的修改和扩展难 C.指令执行速度快,指令功能的修改和扩展容易 D.指令执行速度快,指令功能的修改和扩展难 答案:D 解析: A.5 位 B.6 位 C.15 位 D.33 位 答案:C 解析: A.5 B.6 C.8 D.9 答案:C 解析: A.每个指令周期中 CPU 都至少访问内存一次 B.每个指令周期一定大于或等于一个 CPU 时钟周期 C.空操作指令的指令周期中任何寄存器的内容都不会被改变 D.当前程序在每条指令执行结束时都可能被外部中断打断 答案:C 解析: (1)根据 CPU 的功能和结构标明图中 4 个寄存器的名称。 (2)简述指令 LDA addr 的数据通路,其中 addr 为主存地址,指令的功能是将主存 addr 单元的内容送入 AC 中。 答: (1)根据 CPU 的功能和结构标明图中 4 个寄存器的名称 d:PC(由PC=PC+1和图中的“+1”推断) c:AR(将PC中的内容送入到AR) a:DR(从主存中取出的指令通过数据总线送到MDR) b:IR(将MDR中的内容送入IR中) (2)简述指令 LDA addr 的数据通路,其中 addr 为主存地址,指令的功能是将主存 addr 单元的内容送入 AC 中 取指令阶段的数据通路:PC → AR → 主存M → DR → IR;PC = PC + 1 执行阶段的数据通路:IR(A) → AR → 主存M → DR → AC 6.10 假设构成 CPU 的各功能部件的时间延迟如表 6.21 所示,试分别计算单周期、多周期 MIPS 处理器的最小时钟周期和最大时钟频率。假设某 MIPS 程序包含 1000 亿条指令,其中 lw、sw、beq、R 型算术逻辑运算、I 型算术逻辑运算指令比例分别为 10%、10%、10%、50%、20%,试分别计算该程序在单总线结构处理器、单周期 MIPS、多周期 MIPS 处理器上的 CPI 值及执行时间。

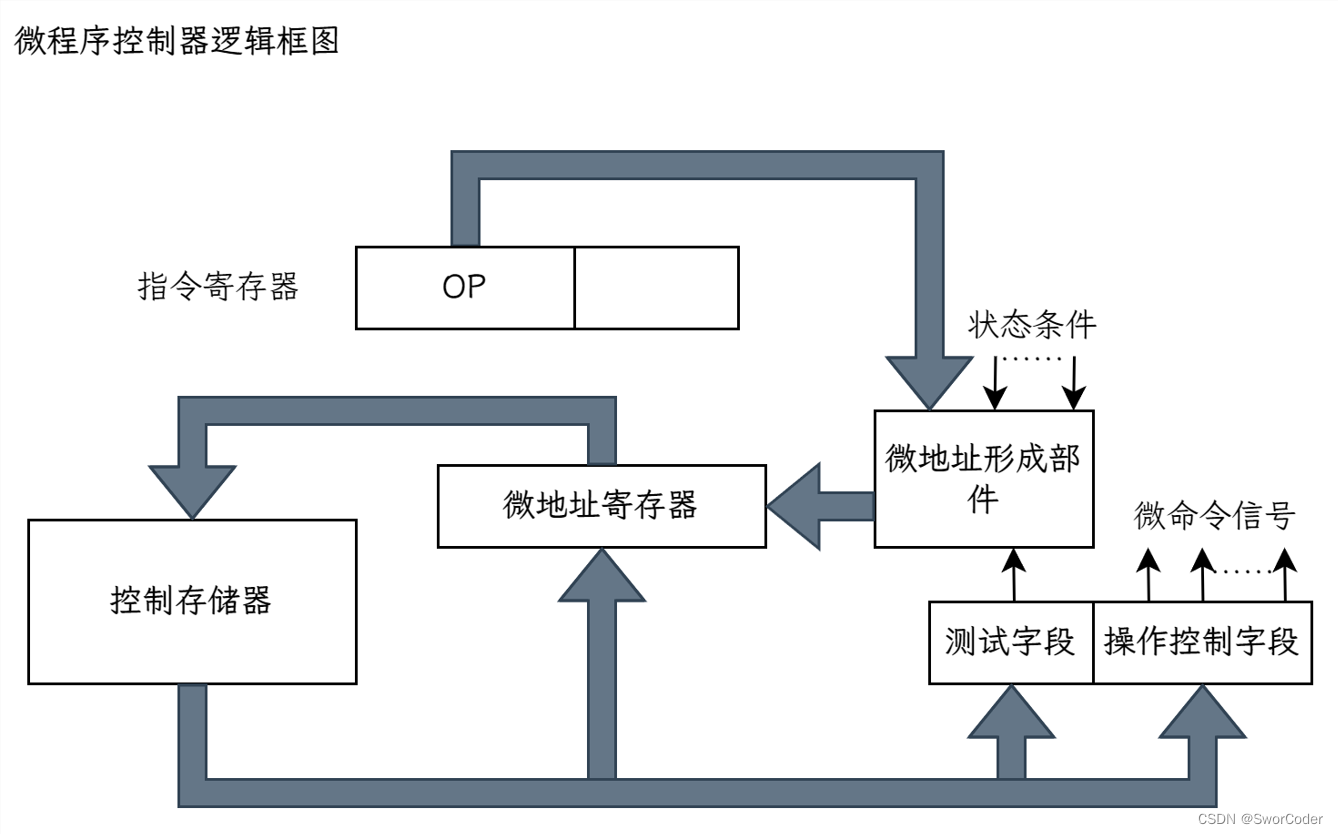

答: (1)微指令的 3 个字段分别应为多少位? (2)画出对应这种微指令格式的微程序控制器逻辑框图。 答: (1)微指令的 3 个字段分别应为多少位 若判别字段中每一位作为一个判别标志,那么因为有3个判别测试条件,故判别测试条件有3位; 由于控制存储器容量为128 × 32 位,所以下址字段有7位(

2

7

=

128

2^{7}=128

27=128),操作字段有(32 - 3 - 7)位 = 22位。 (2)画出对应这种微指令格式的微程序控制器逻辑框图 |

【本文地址】

今日新闻 |

推荐新闻 |