CPU组成结构 |

您所在的位置:网站首页 › cpu主要由什么组成 › CPU组成结构 |

CPU组成结构

|

CPU组成结构

CPU总体构图

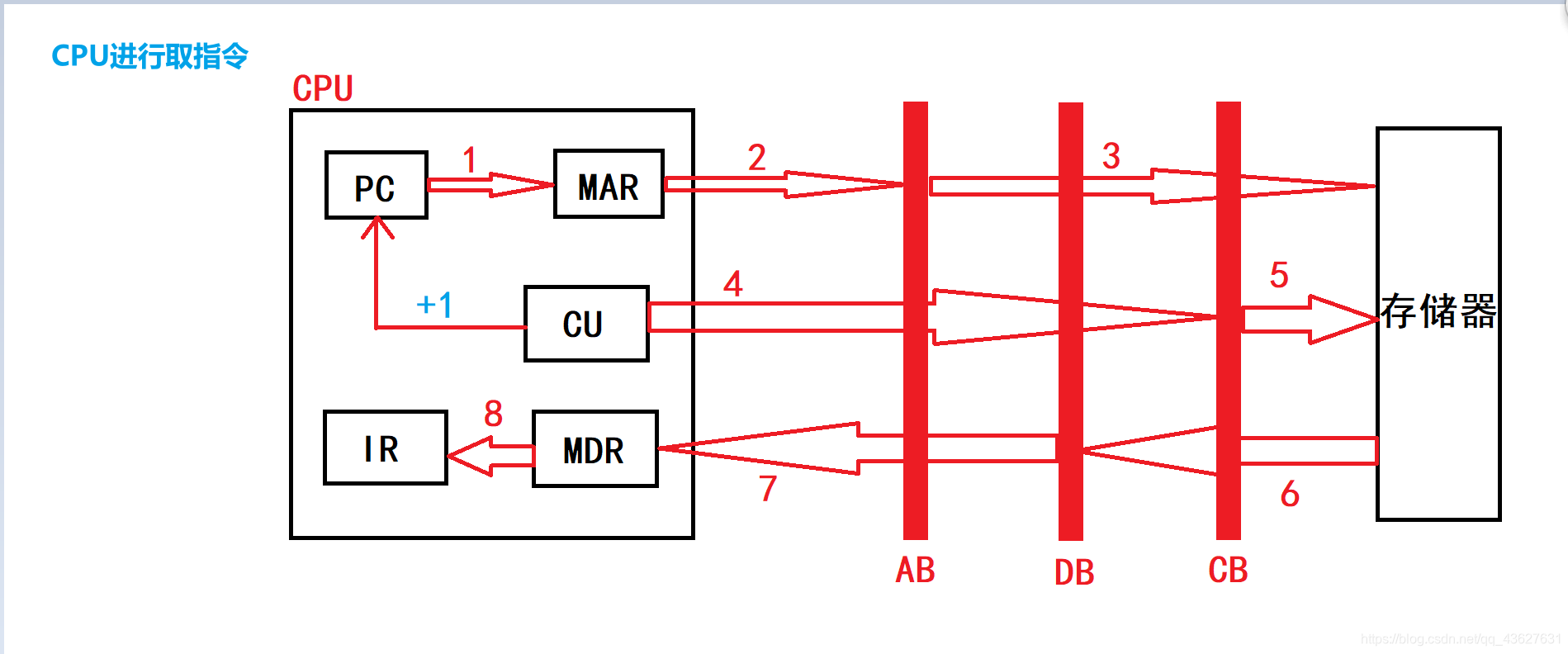

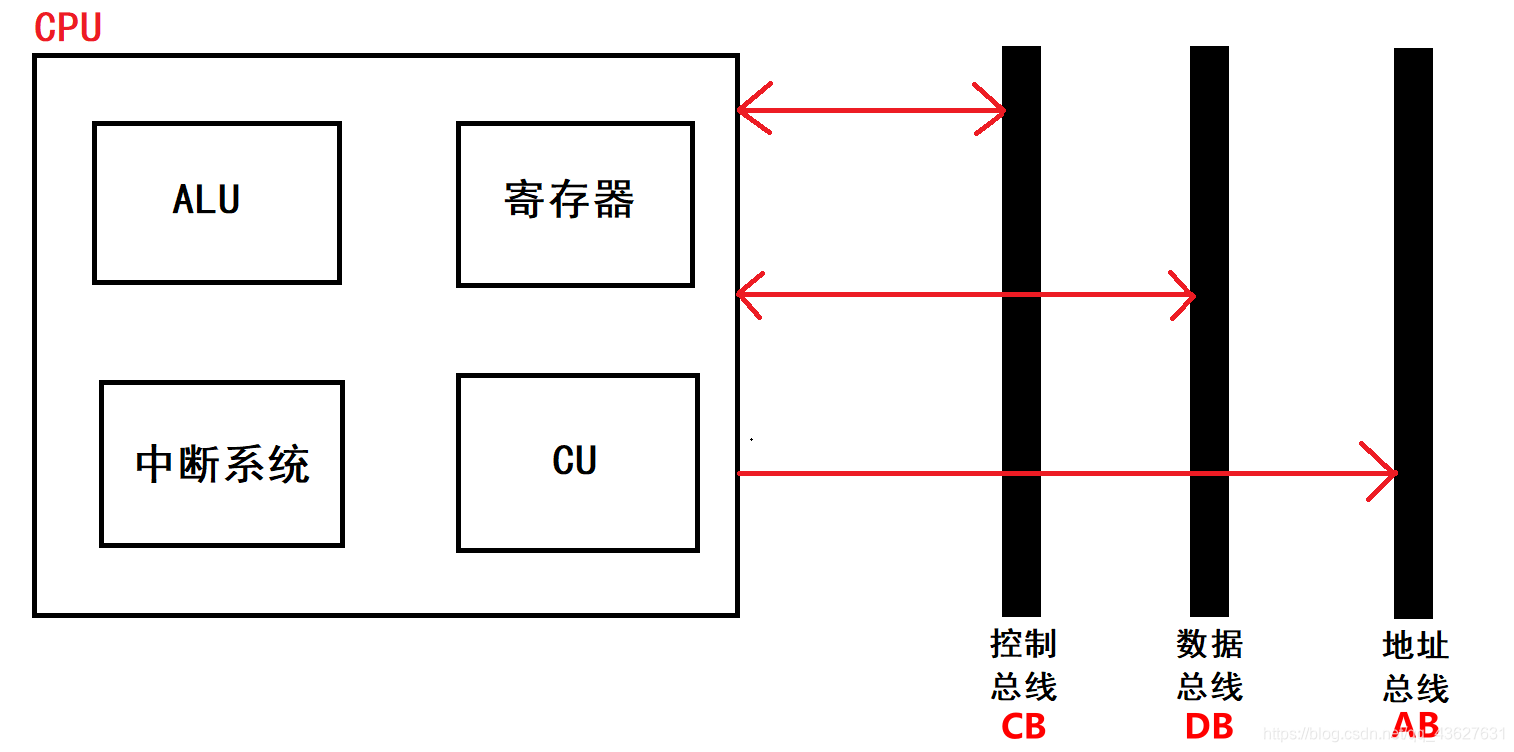

CPU中央处理器(Central Processing Unit) CPU的结构框图:CPU内部由ALU(算术逻辑单元)、CU(控制器)、寄存器(PC、IR、PSW、DR、通用寄存器等)、中断系统组成,外部通过总线与控制总线、数据总线、地址总线进行相连,对数据和程序进行相关的操作。 控制器的功能: (1)从指令cache中取出一条指令,并指出下一条指令在指令cache中的位置。 (2)对指令进行译码或测试,并产生相应的操作控制信号,以便于启动规定的动作。例如:一次数据cache的读写操作,一个算术逻辑运算操作,一个输入输出操作。 (3)指挥并控制CPU,数据cache和输入输出设备之间数据流向的方向。 控制器内部的组成部分: 程序计数器(PC):用来存放下一条要执行的指令的地址。指令寄存器(IR):用来存放当前正在执行的指令。指令译码器(ID):对指令进行“翻译”,确定指令执行什么操作,以决定操作的性质和方法。控制电路:根据指令译码器的分析,发出控制信号,完成该指令的所有操作。详细分析CPU取指的流程: 指令的地址保存在程序计数器(PC)中,取指过程中,不需要使用ALU,要想把指令从内存单元中取出来,先要知道指令的地址,即需要从PC中取出指令地址。PC先把指令地址传输到MAR(存储器地址寄存器),通过MAR把信号送到地址总线,最后送到存储器。这时存储器已经得到系统将要执行的指令地址。 然后由控制单元CU向存储器发出读命令,读出的数据由存储器通过数据总线送到MDR,再由MDR送到==IR(指令寄存器)==中。这是程序计数器PC自动加一,从而确定了下一条指令的地址。

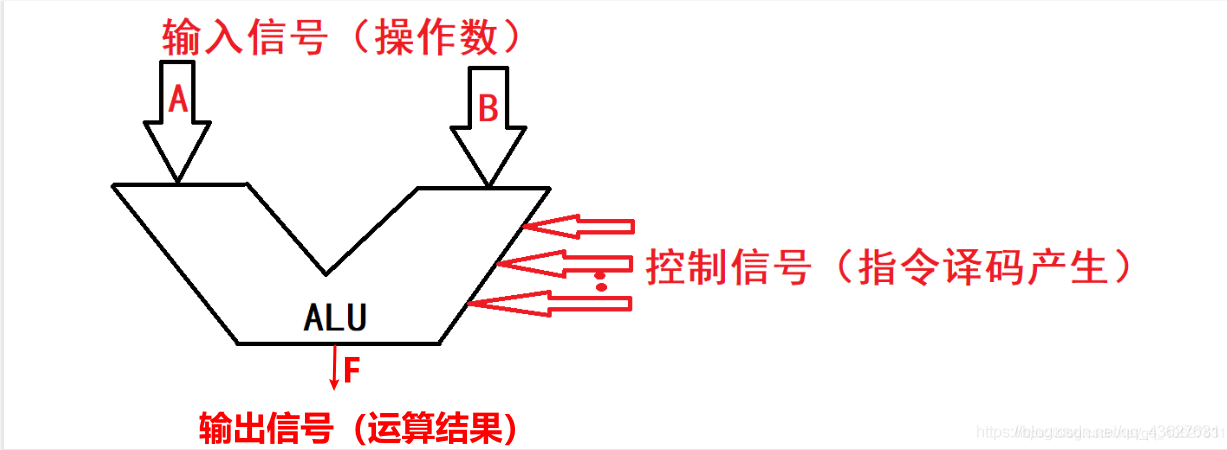

针对每一种算术运算,都必须有一个相对应的基本硬件配置,其核心部件是加法器和寄存器。 算术逻辑单元的功能: (1)执行所有的算术运算。 (2)执行所有的逻辑运算,并进行逻辑测试。如零值测试或两个数的比较。

寄存器是用来暂时保存运算和控制过程中的原始数据,中间结果,最终结果以及控制、状态信息的。CPU的寄存器被分为:用户可见寄存器、控制和状态寄存器 用户可见寄存器: (1)通用寄存器:存放原始数据和运算结果,可以作为某种寻址方式所需的专用寄存器。当算术逻辑单元ALU执行算数或逻辑运算时,通用寄存器为ALU提供一个工作区。现代计算机中,为了减少CPU访问存储器的次数,提高运算速度,往往设置大量的寄存器。通用寄存器一般由CPU直接访问,CPU对寄存器的访问速度远大于访问主存的速度。 (2)数据寄存器:存放操作数、运算结果和运算的中间结果,以减少访问存储器的次数,或者存放从存储器读取的数据以及写入存储器的数据的寄存器。寄存了将要写入到计算机主存储器(例如:RAM)的数据,或由计算机主存储器读取后的数据。它就像缓冲器,持有从内存复制的数据,以准备给处理器使用。 (3)地址寄存器:用来保存当前CPU所访问的内存单元的地址。由于在内存和CPU之间存在着操作速度上的差别,所以必须使用地址寄存器来保持地址信息,直到内存的读/写操作完成为止 。 (4)条件码寄存器:存放条件码(条件码:体现当前指令执行结果的各种状态信息,如有无进位(CF位)、有无溢出(OV位)、结果正负(SF位)、结果是否为零(ZF位)、奇偶标志位(P位)等),可作程序分支的依据。 控制和状态寄存器 (1)控制寄存器:控制寄存器(CR0~CR3)用于控制和确定处理器的操作模式以及当前执行任务的特性。 (2)状态寄存器: 状态寄存器:存放条件码 PSW寄存器:保存由算数指令和逻辑指令运算或测试结果建立的各种条形码;保存中断和系统工作状态等信息。 |

【本文地址】

今日新闻 |

推荐新闻 |

CPU的功能: (1)指令控制:按照顺序进行取指操作,由控制器CU完成取指和分析指令的操作。 (2)操作控制:能对指令进行译码、寄存、执行的有关操作。 (3)时间控制:对各种操作进行的时间实施定时。 (4)数据加工:能够进行算术运算和逻辑运算,该功能的实现由ALU寄存器(算术逻辑单元)完成。 (5)处理中断:能够响应输入输出设备发出的中断请求。

CPU的功能: (1)指令控制:按照顺序进行取指操作,由控制器CU完成取指和分析指令的操作。 (2)操作控制:能对指令进行译码、寄存、执行的有关操作。 (3)时间控制:对各种操作进行的时间实施定时。 (4)数据加工:能够进行算术运算和逻辑运算,该功能的实现由ALU寄存器(算术逻辑单元)完成。 (5)处理中断:能够响应输入输出设备发出的中断请求。