用Cadence Virtuoso IC617结合gm/id方法设计运放(五管OTA加共源极) |

您所在的位置:网站首页 › cadence设计共源共栅放大器 › 用Cadence Virtuoso IC617结合gm/id方法设计运放(五管OTA加共源极) |

用Cadence Virtuoso IC617结合gm/id方法设计运放(五管OTA加共源极)

|

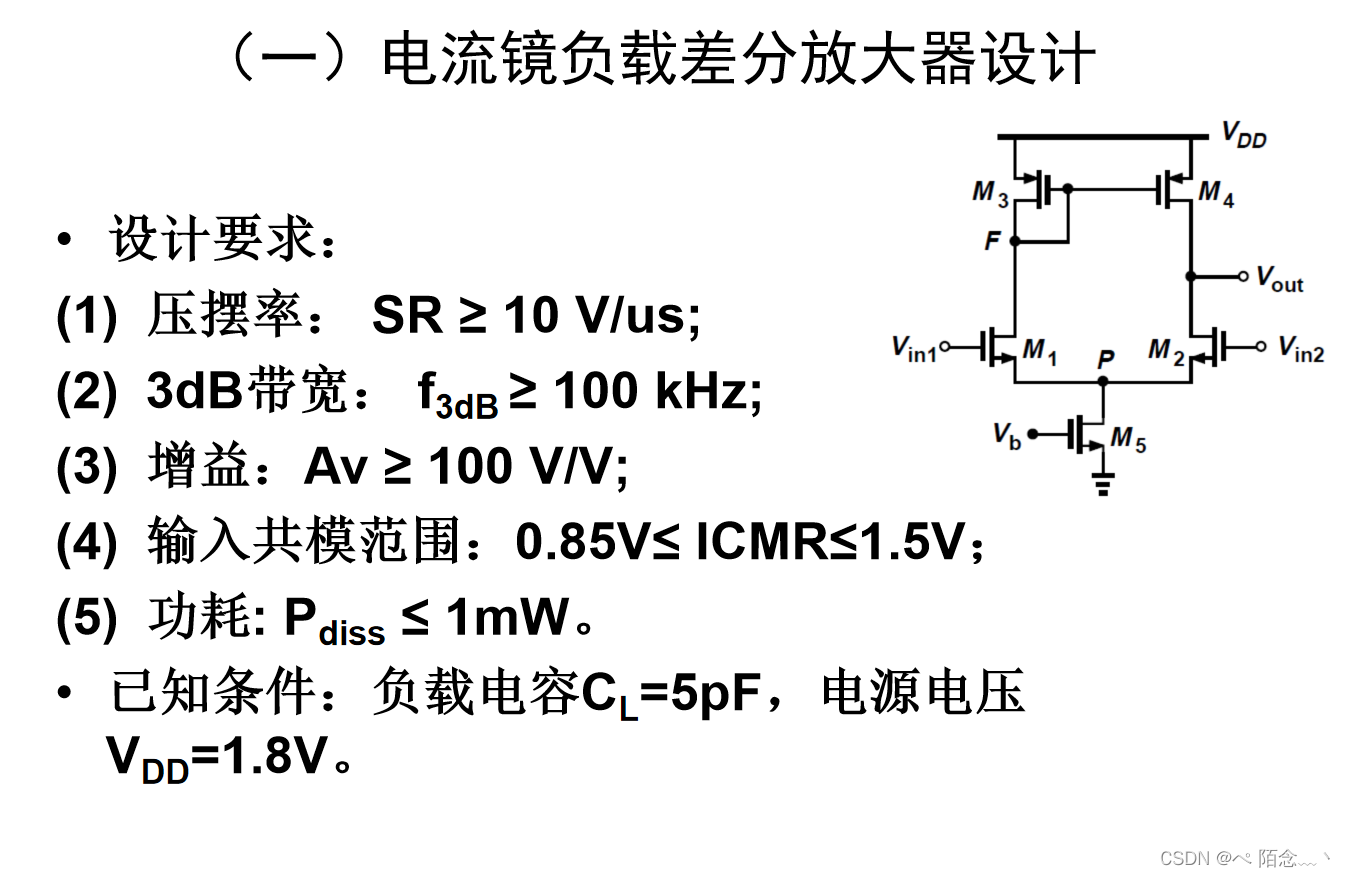

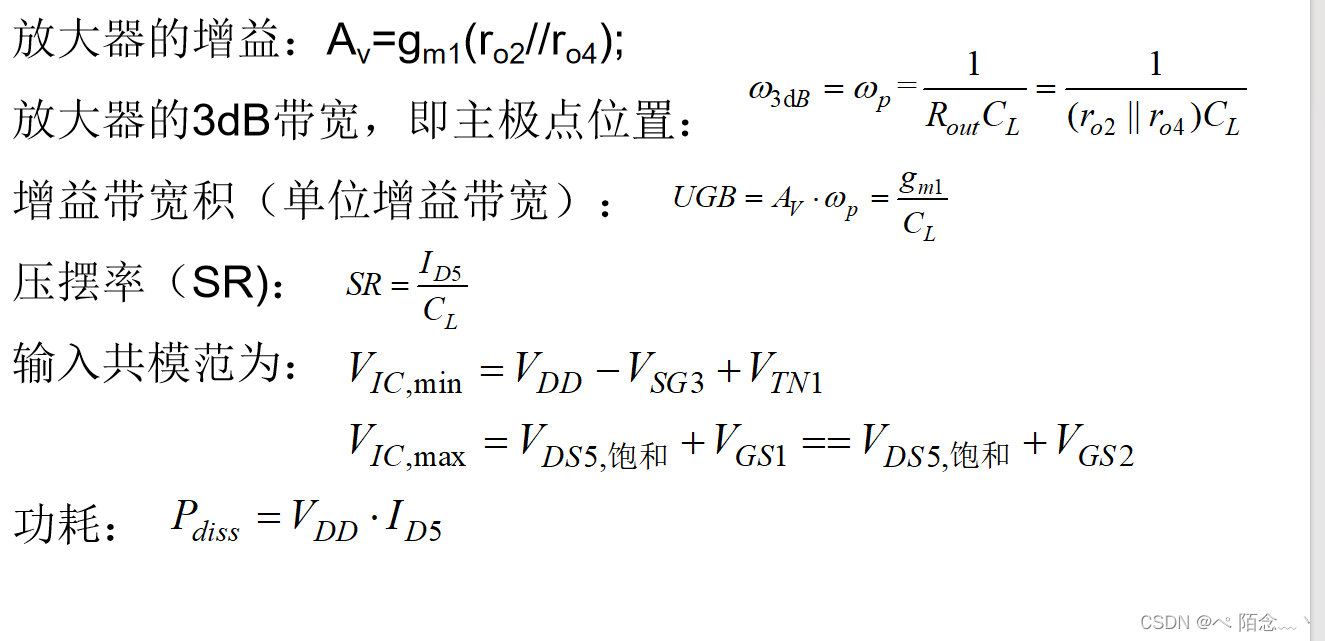

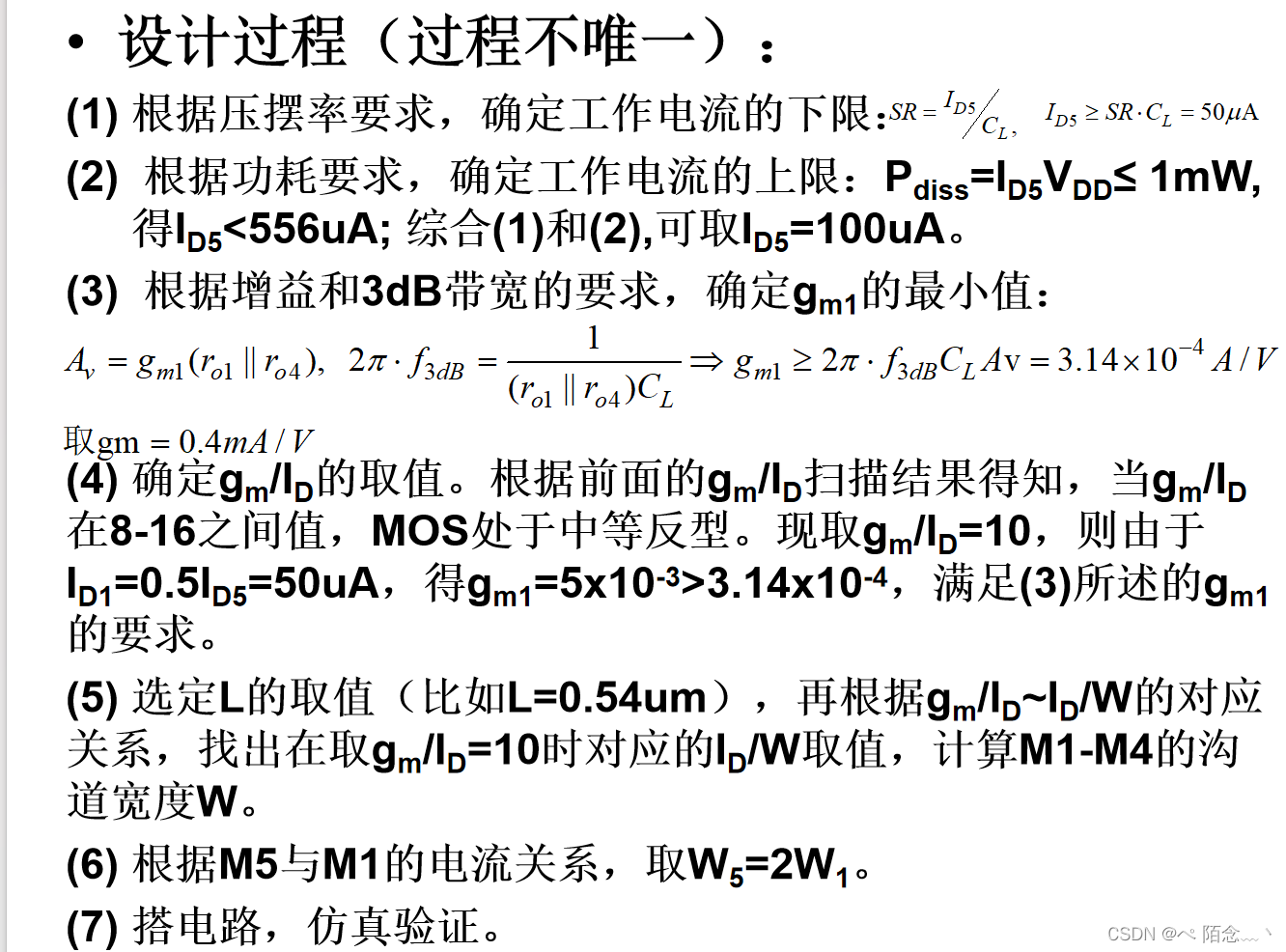

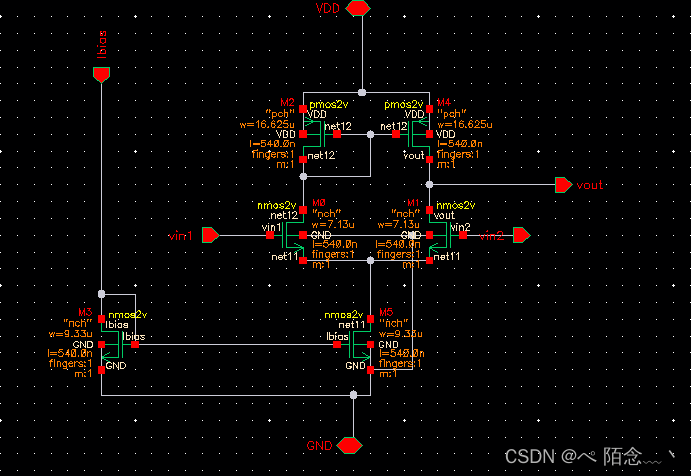

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、设计步骤1.原理描述2.设计过程(过程不唯一)3.搭电路计算nmos,pmos 中的w总电路图 4 仿真1输入共模范围2.共模增益3.差模增益4.-3db带宽5.功耗6.压摆率文章参考: http://t.csdn.cn/7SfzC http://t.csdn.cn/EFwhk http://t.csdn.cn/ujpfD 注: 1.选取最小栅长180nm的两倍作为晶体管栅长,定以下尺寸。晶体管栅长的最小步进是10nm,也就是说,只能是180nm,190nm这样取值,而不能取185nm,会导致W/L的实际取值和计算稍微有点偏差。 2.主要熟悉设计和仿真流程,怎么修改参数到达要求,还没弄太明白,后续慢慢学习 前言设计目标

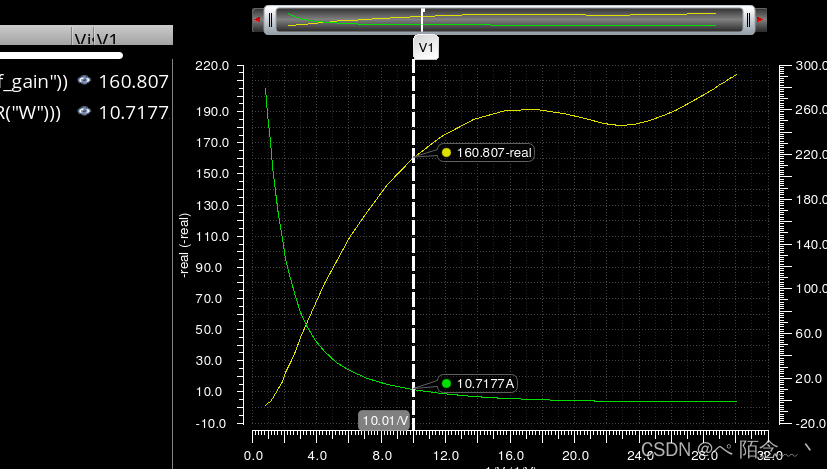

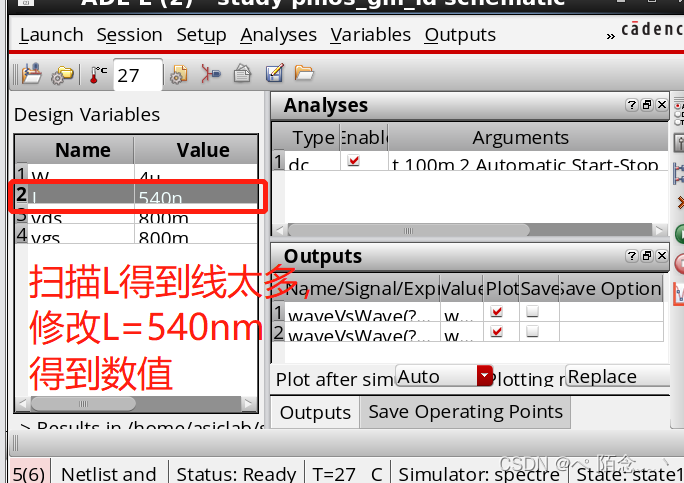

确定NMOS M0,M1宽,选L=0.54um=540nm,打开之前NMOS中gmid-id/w的图,找到L=0.54um=540nm下,gmid-id/w的所对应的曲线,算出W W=I/ id/w W=I/ id/w = 50ua / 10.7177 = 4.67

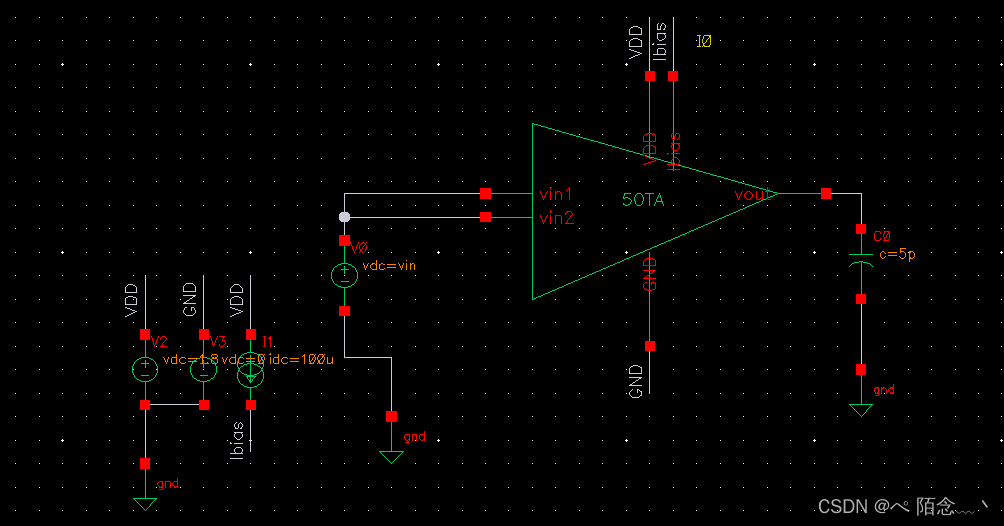

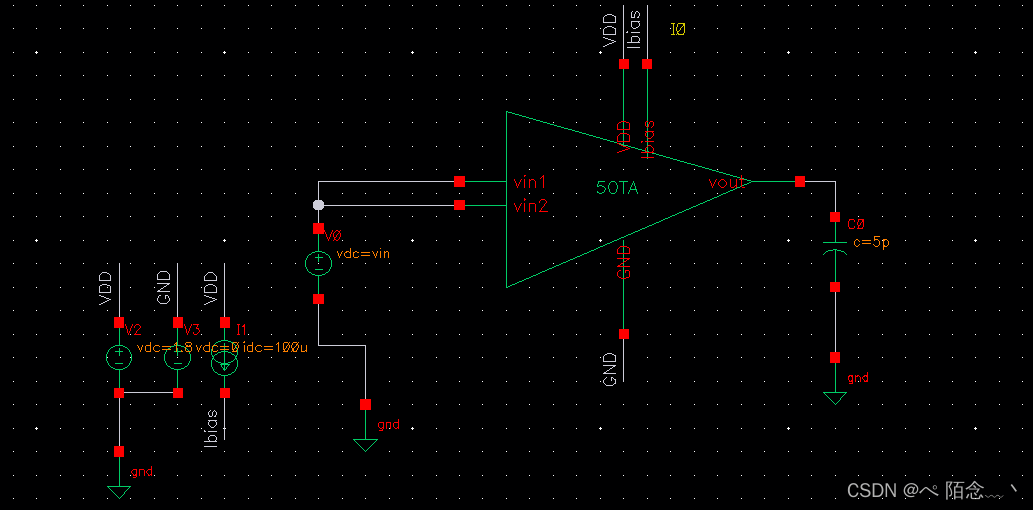

对设计5点要求进行验证 1输入共模范围电路图

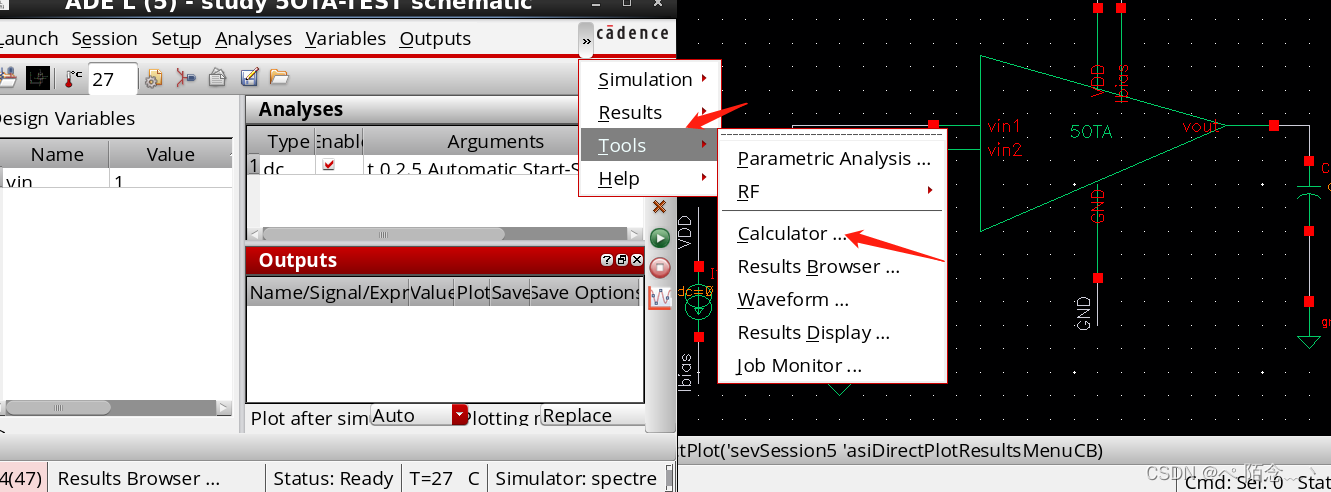

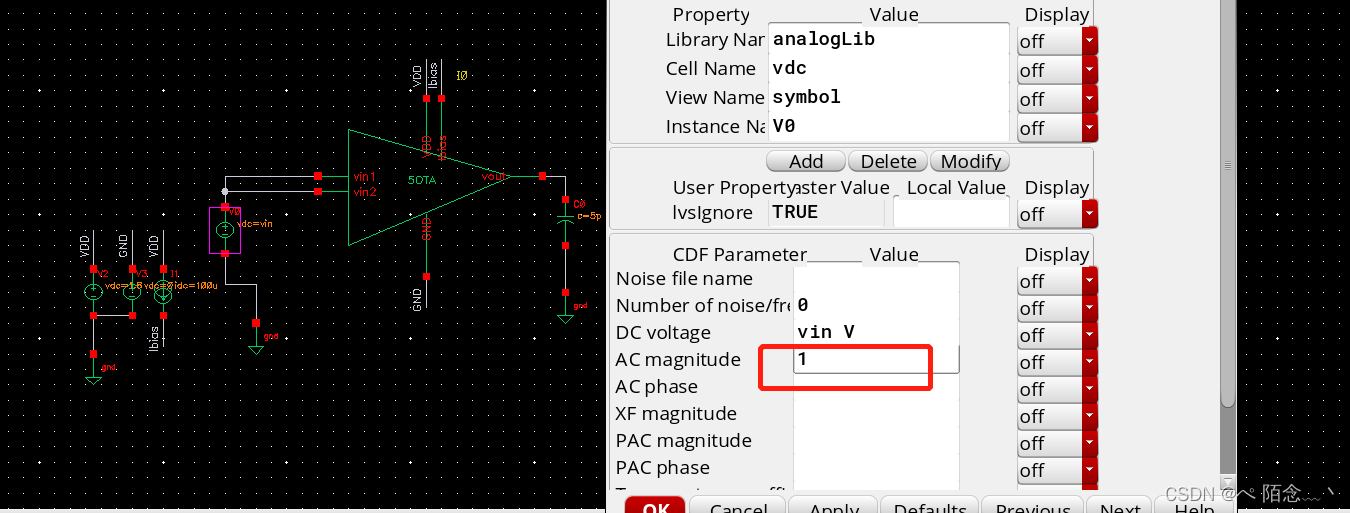

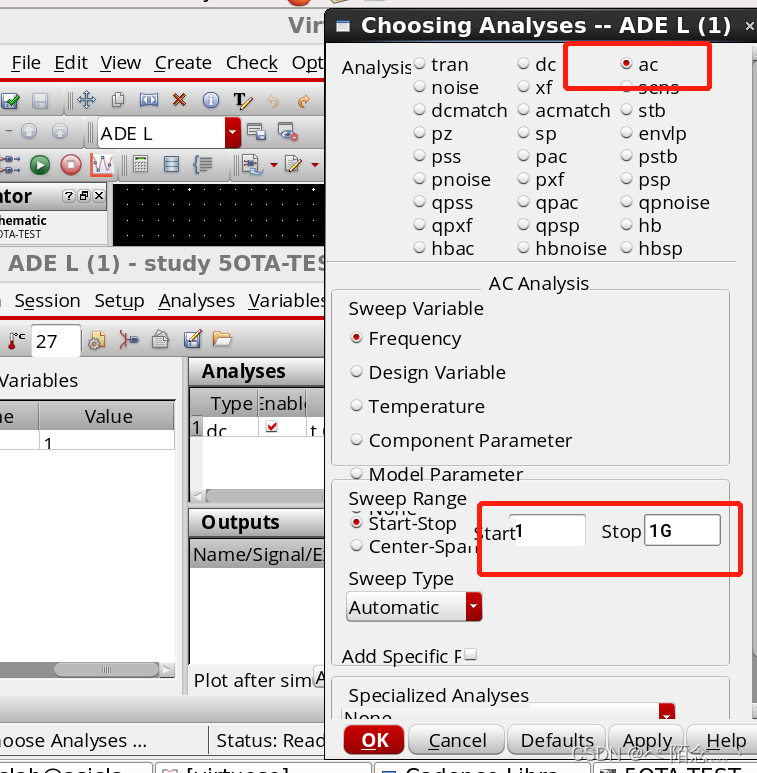

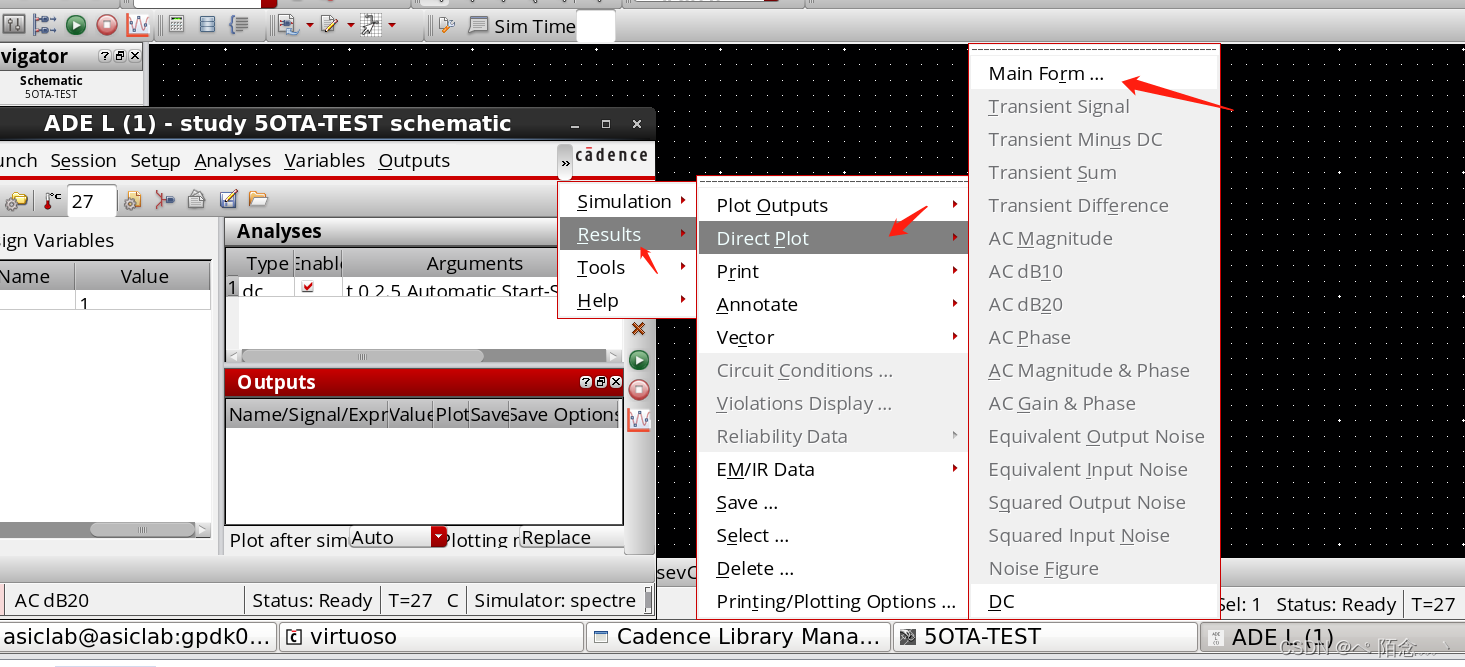

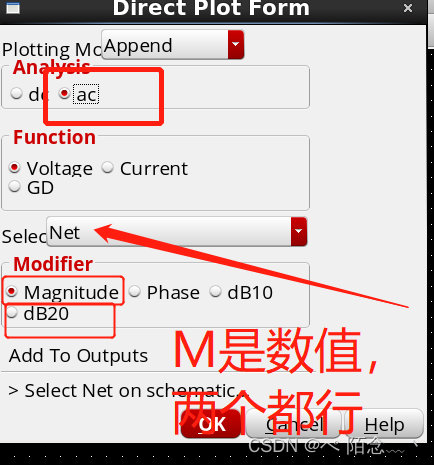

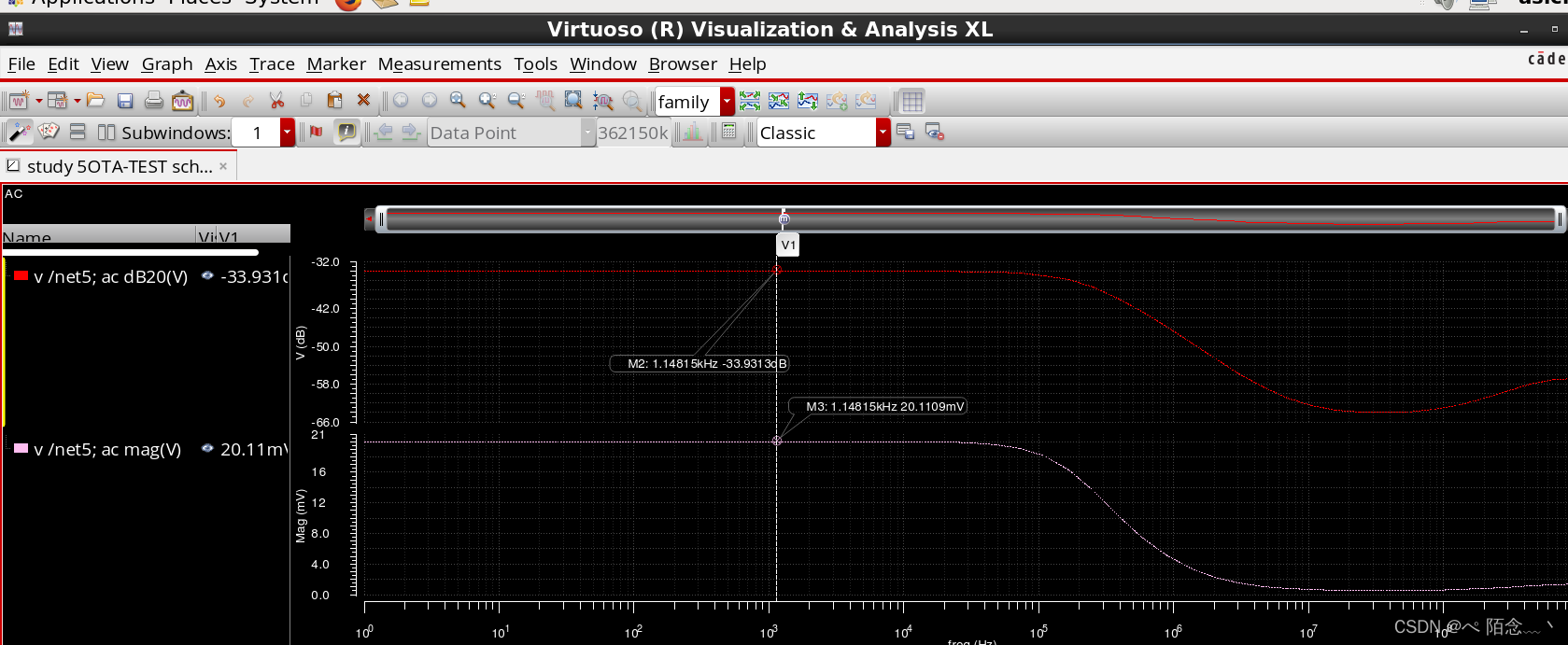

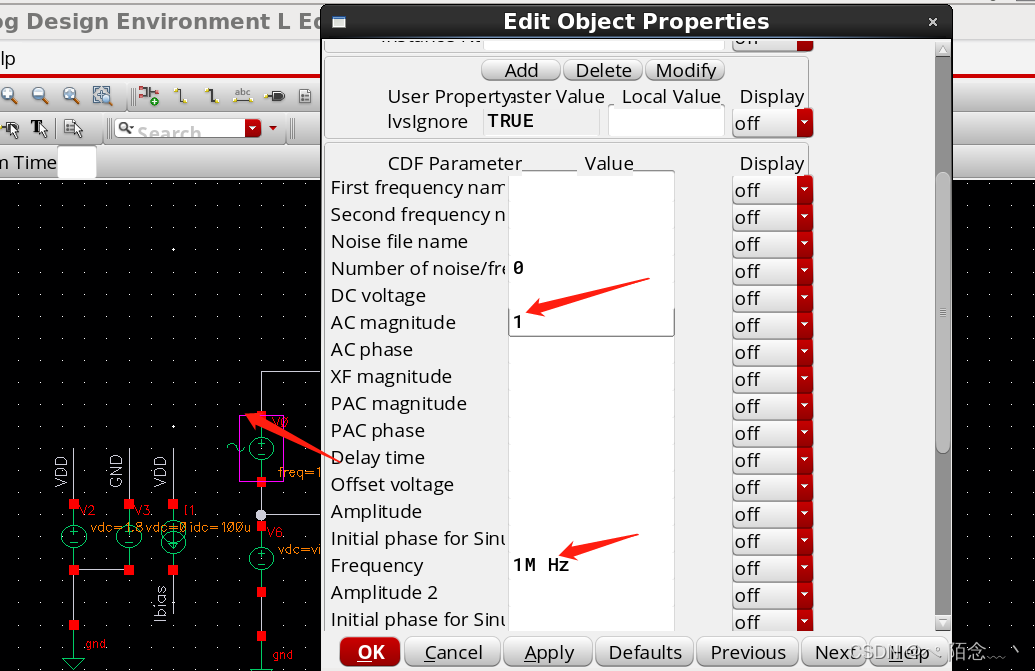

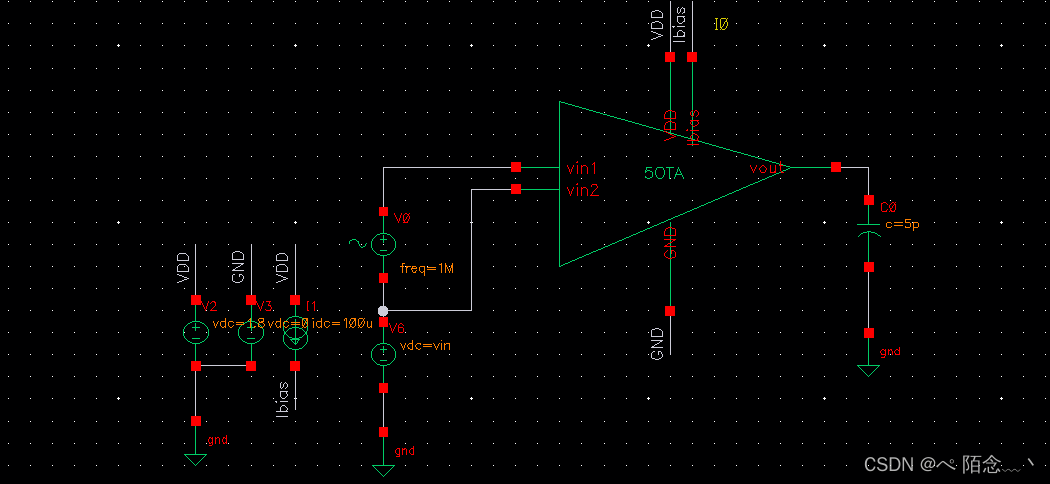

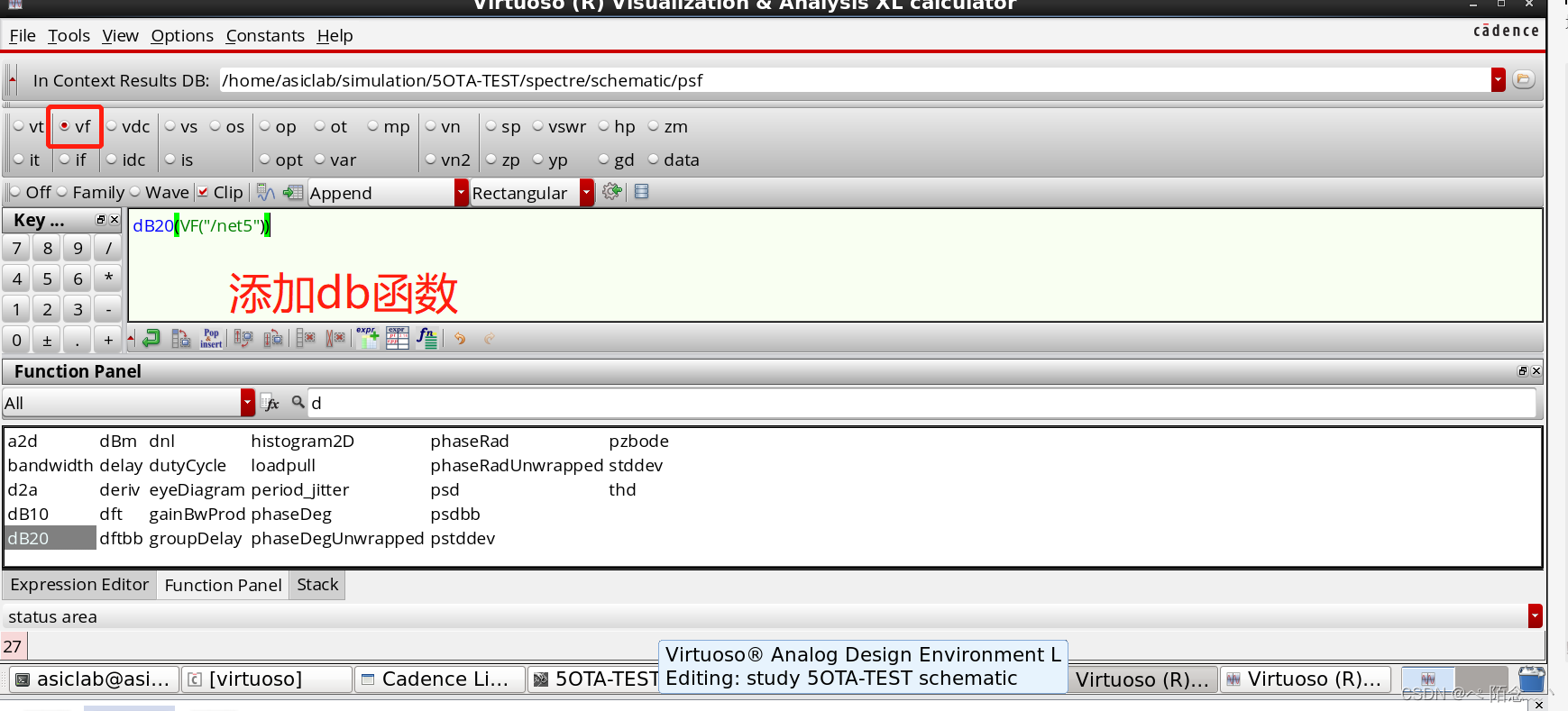

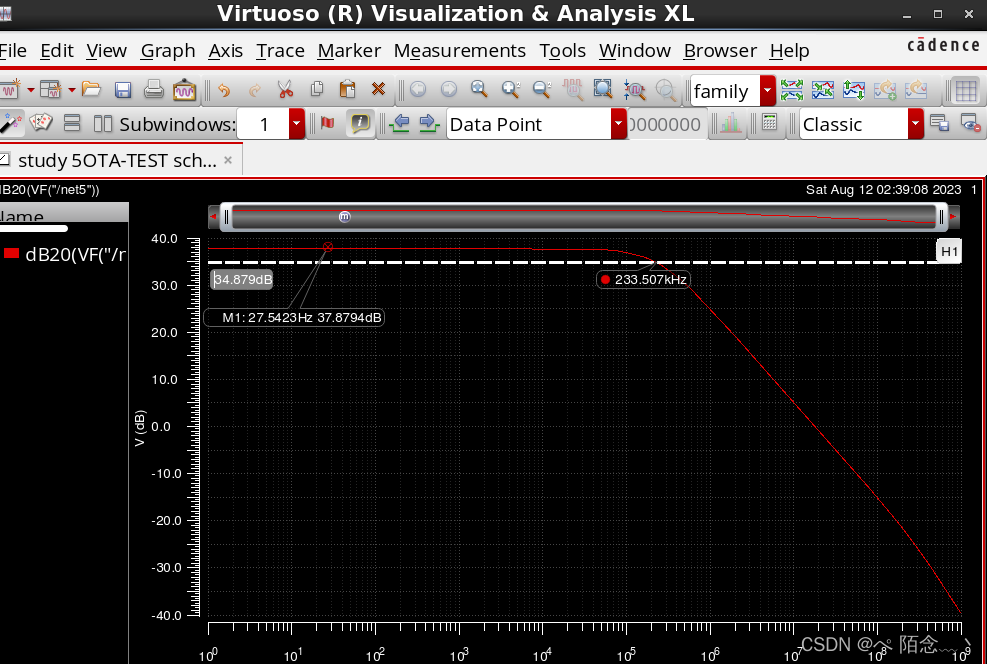

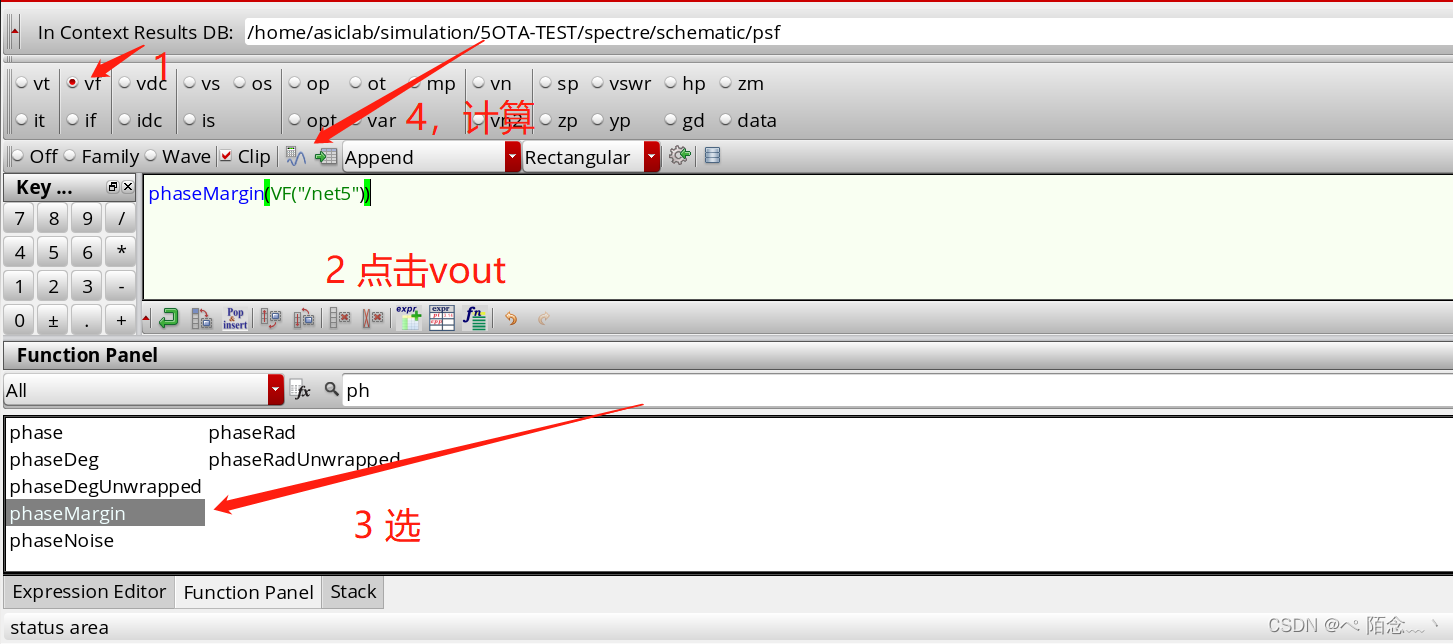

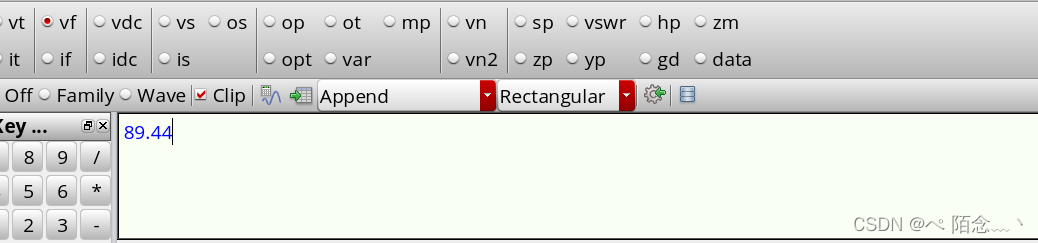

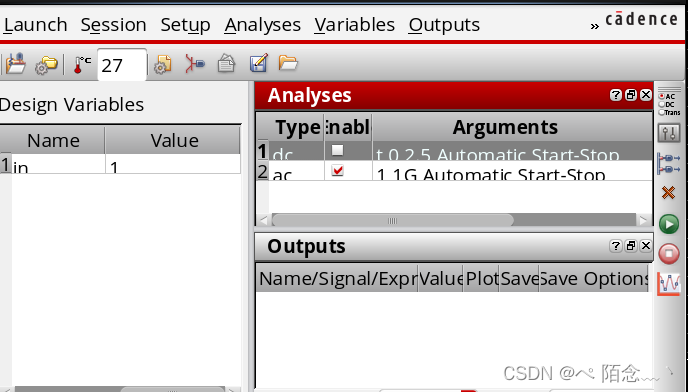

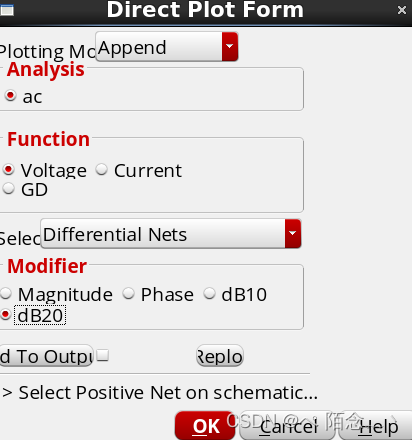

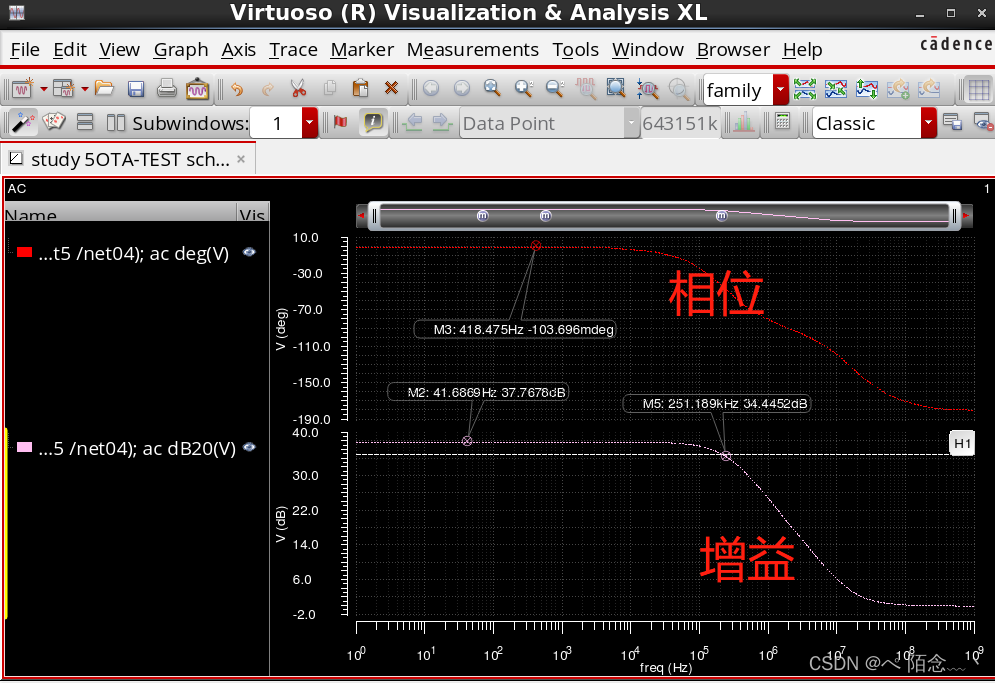

电路图 在输入共模电平添加一个小信号,设置小信号幅值为1,那么输出的Vout就是共模放大倍数 设置好先运行一下,不然后续步骤不能运行 仿真 一个小信号变化叠加在两输入之间,对于放大器而言就是输入了一个差模信号,现设置差模信号幅值为1,那么输出的Vout就是差模放大倍数 电路图:添加 vsin ,频率为1M,AC magnitude为1V 电路图 仿真 增益37.8794db , -3db带宽233.507Khz, 打开计算器—vf ----点击原理图vout ---- all ----PhaseMargin 观察差模增益和相位裕度也可用 main form 去掉dc,不然后面跳不出来曲线

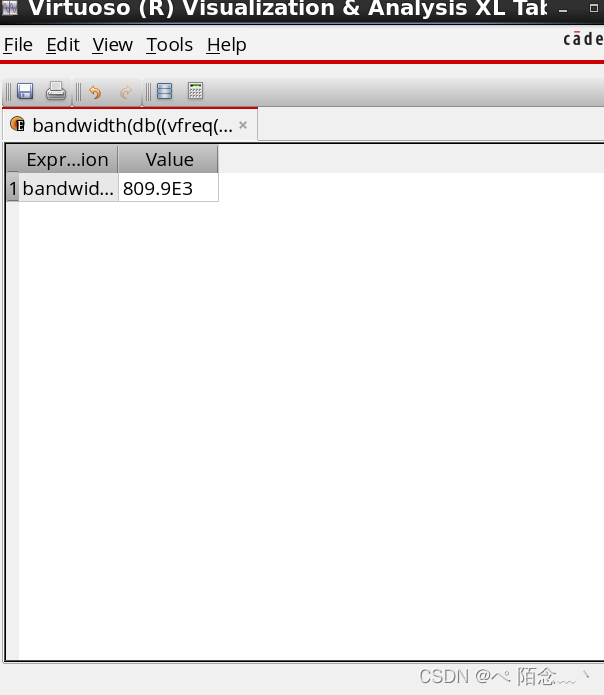

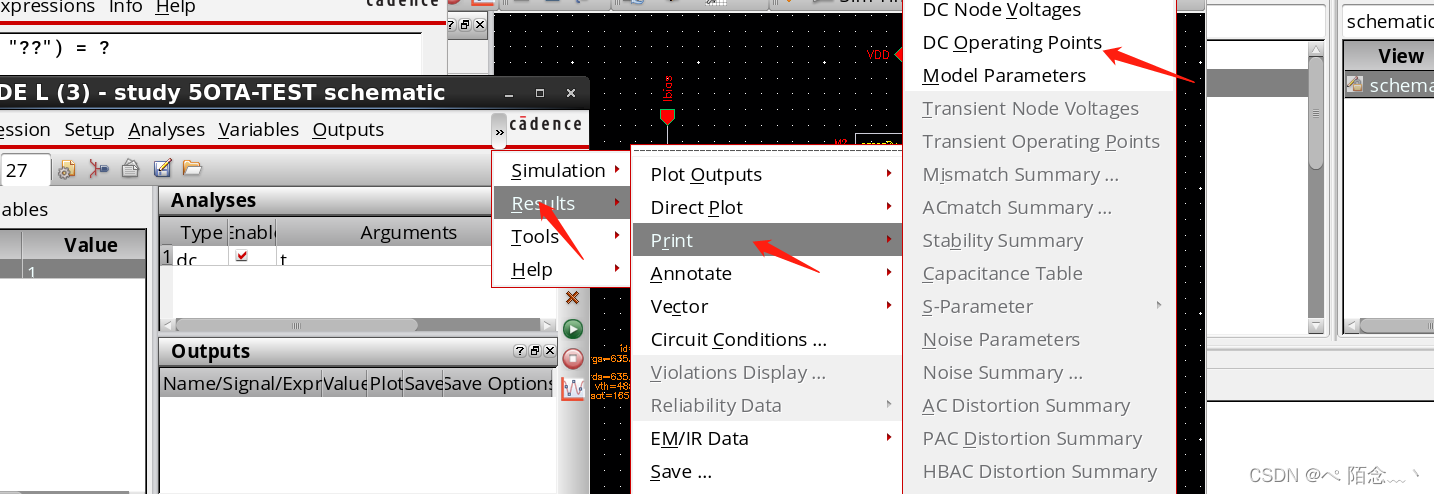

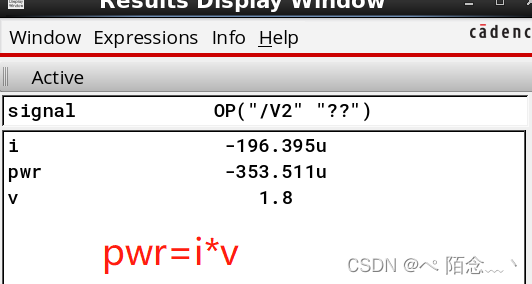

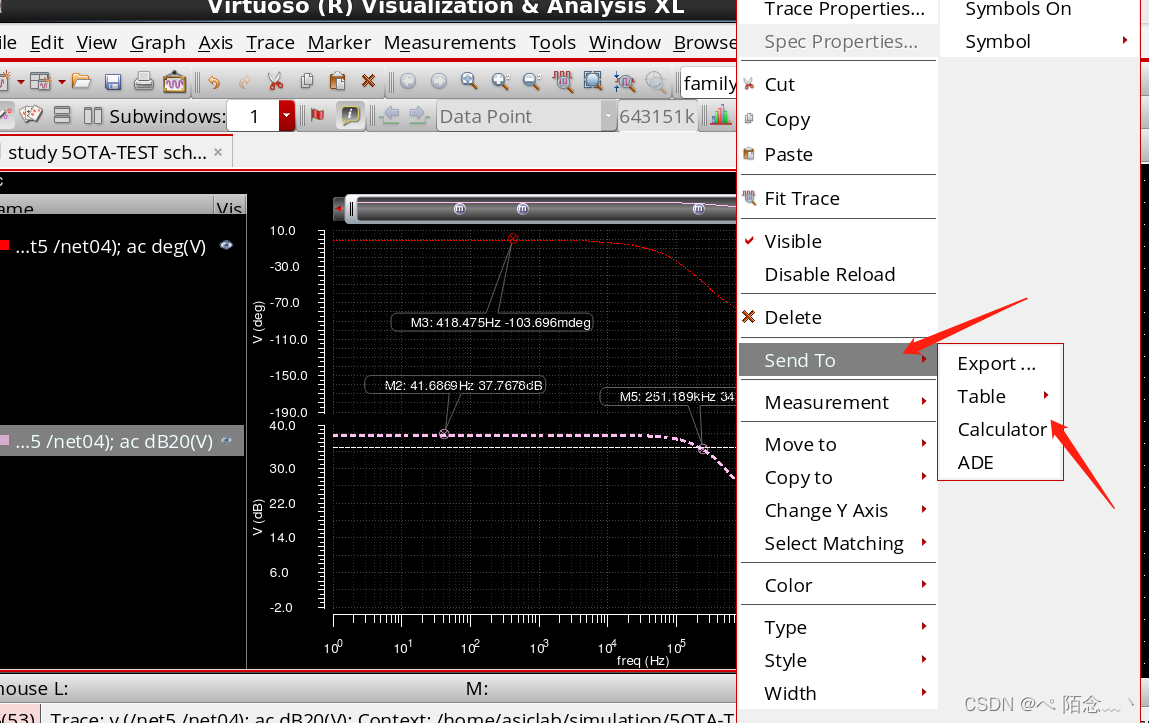

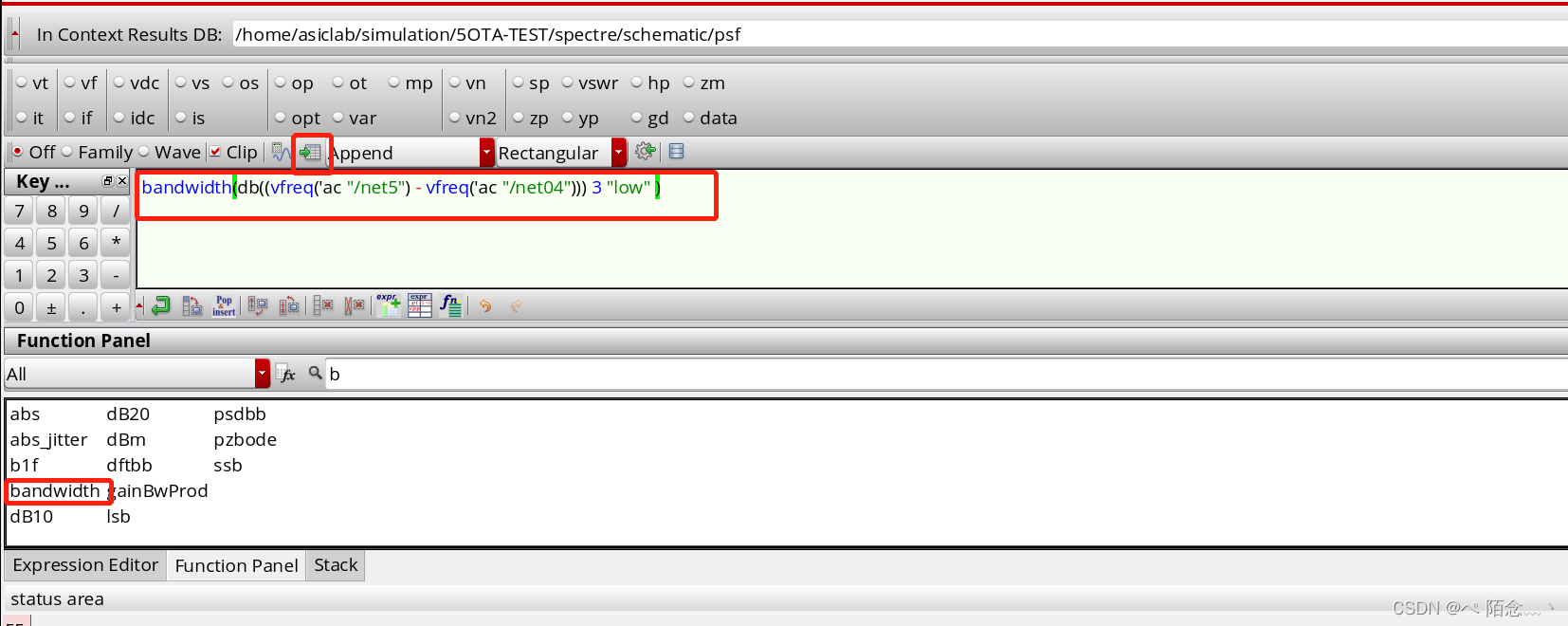

仿真结果 用计算器查看-3db带宽 选中幅频曲线----右键-----send to----caculat------bandwith—ok pwr=总电流×VDD=100u*1.8

点击vdc 压摆率 是看的瞬态的斜率 放出瞬态来自己算 |

【本文地址】

今日新闻 |

推荐新闻 |

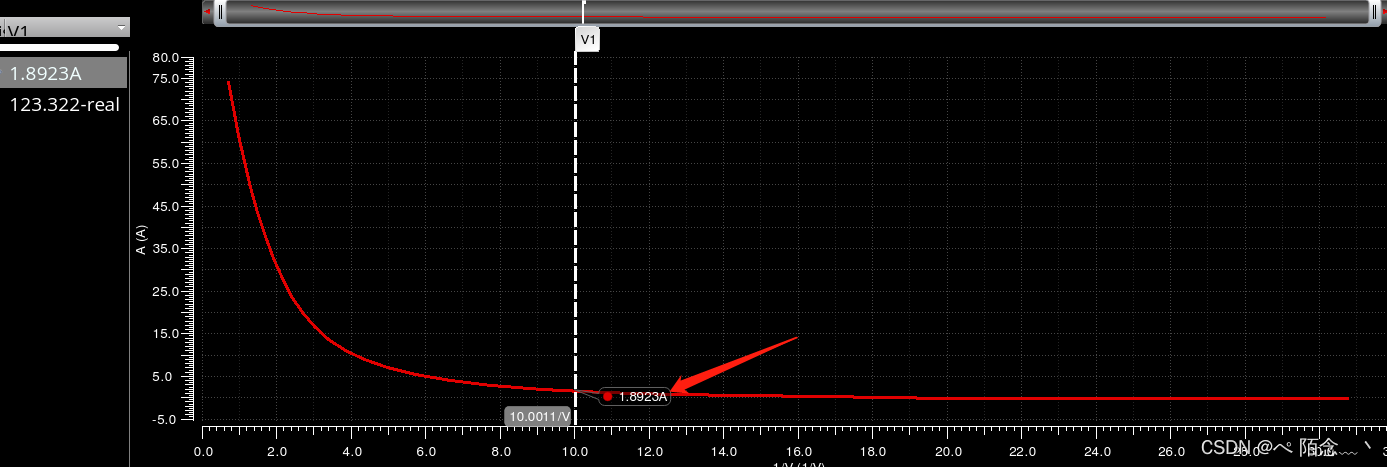

同理算出PMOS中的宽。

同理算出PMOS中的宽。  PMOS L=540nm时id/w=1.8923A,W=W=I/ id/w =50uA/1.8923=26.42

PMOS L=540nm时id/w=1.8923A,W=W=I/ id/w =50uA/1.8923=26.42

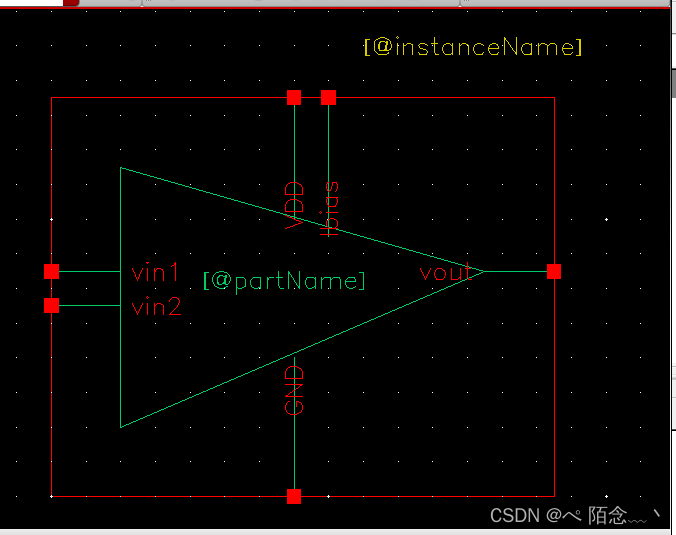

创建symbol

创建symbol

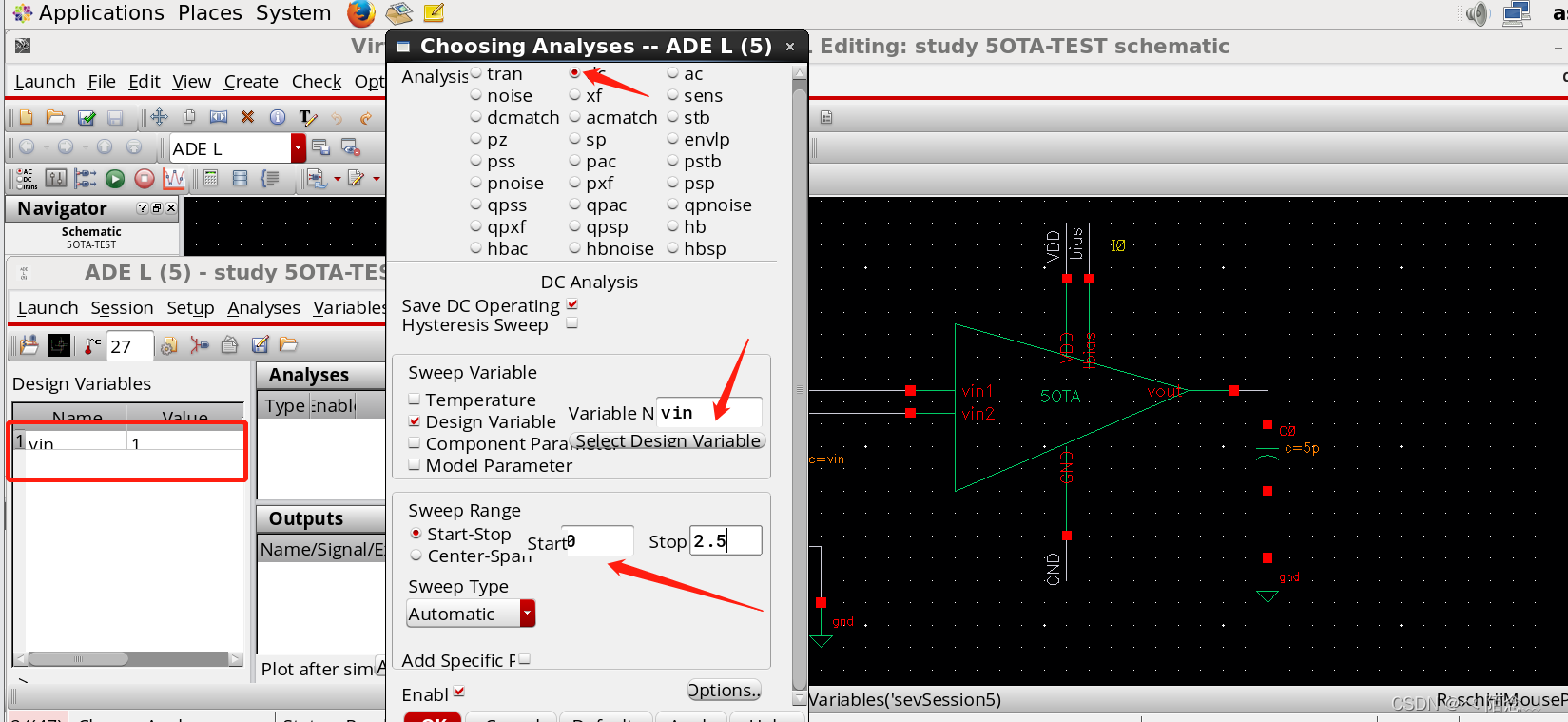

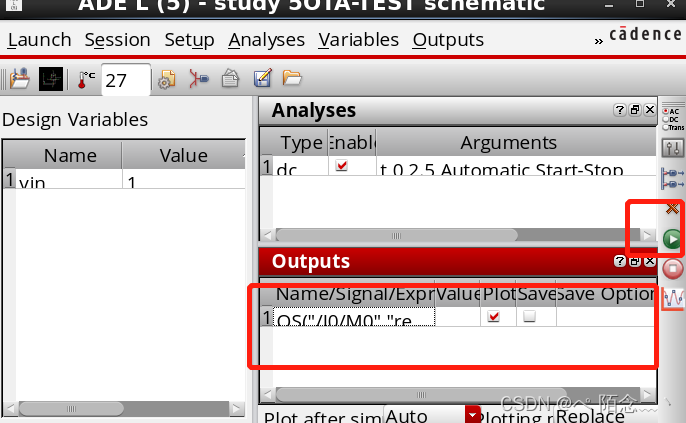

仿真设置 设置变量,dc仿真

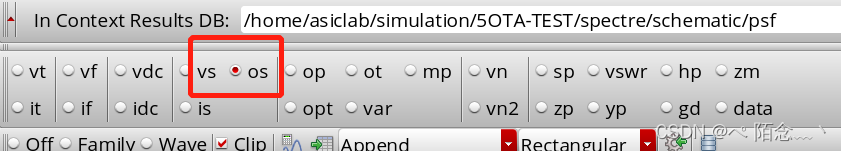

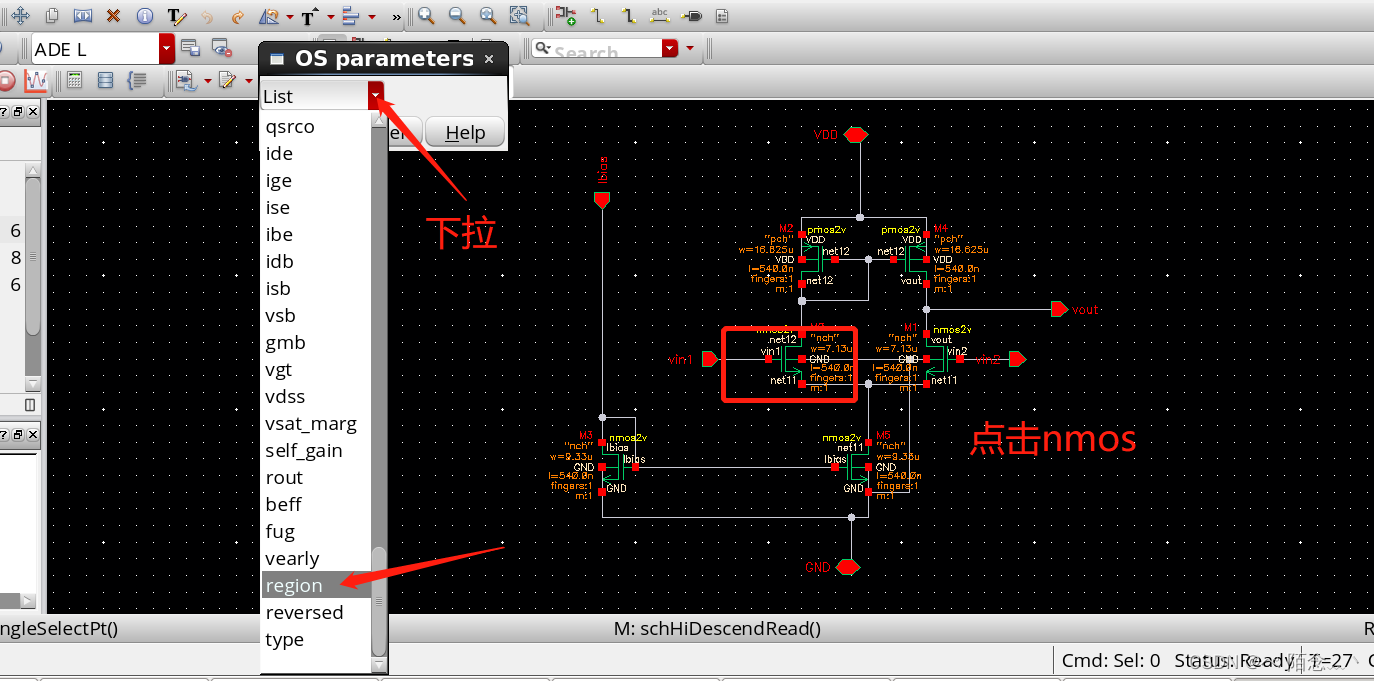

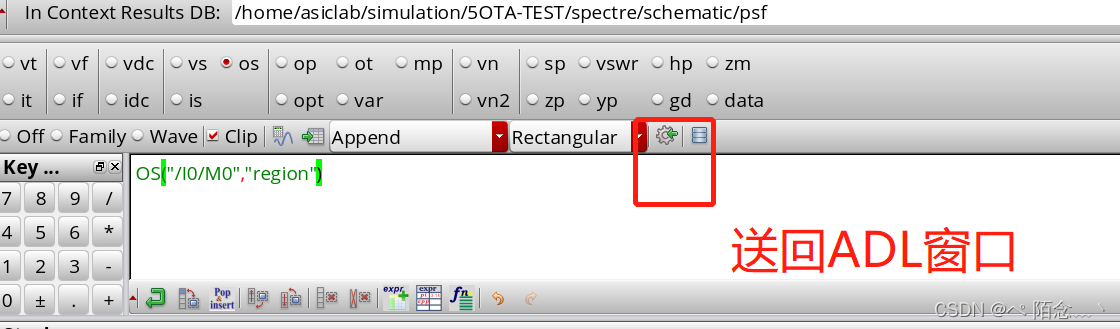

仿真设置 设置变量,dc仿真  对输入管进行共模仿真 打开计算器,os ---- 点击输入管,-------选中resign-----

对输入管进行共模仿真 打开计算器,os ---- 点击输入管,-------选中resign-----

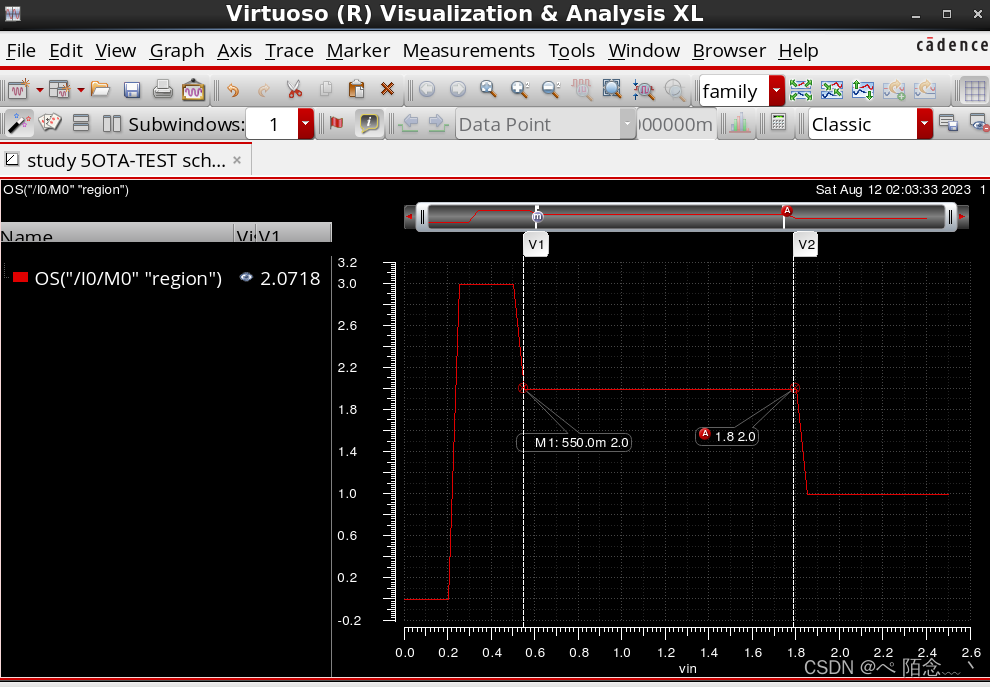

共模范围 550.0mv—1.8v 不满足

共模范围 550.0mv—1.8v 不满足

点击输出

点击输出

观察相位裕度 稳定性仿真可以直接看相位裕度,而交流仿真可以看其某一点相位,从而计算出相位裕度 PM = 180 ° + 相位

观察相位裕度 稳定性仿真可以直接看相位裕度,而交流仿真可以看其某一点相位,从而计算出相位裕度 PM = 180 ° + 相位

809.9khz,数值不一样,原因不懂

809.9khz,数值不一样,原因不懂