实习:BG版图设计 |

您所在的位置:网站首页 › cadence教程版图 › 实习:BG版图设计 |

实习:BG版图设计

|

一、实习任务

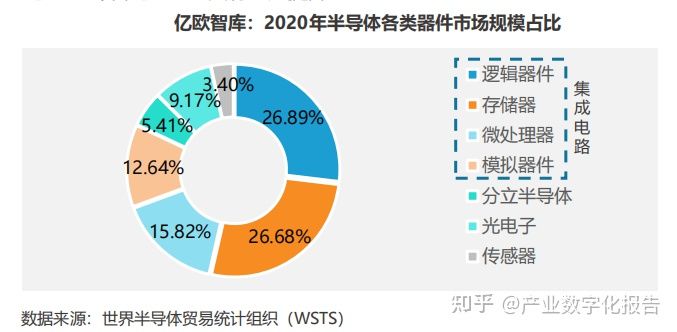

1、熟悉EDA软件相关操作、项目库搭建以及常用规则; 2、掌握版图的匹配设计(电流镜、差分对、三极管、电阻等); 3、学习模拟前端设计典型案例、模拟前端设计规则、与后端得连续与规则; 4、明白版图中电位隔离措施、噪声模块与敏感模块的区分、噪声信号的屏蔽方式以及敏感信号的保护措施; 5、了解版图寄生参数提取、版图后仿以及数据打包等操作。 6、完成BG版图布局、绘制、验证及修改; 二、实习总结 1、实习项目背景与意义要求:请对实习项目背景进行简介,包含专业行业背景知识/行业的生产、设计、研究开发流程/项目对环境、社会和可持续发展的影响。 本次实习的岗位为集成电路版图设计工程师。根据相关要求,本人从以下几点进行实习项目背景与意义的阐述。 1)专业行业背景知识(1)专业背景 纵观过去半个世纪,半导体产业的迅猛发展为现代信息技术革命提供了基础。如今,半导体已经成为人们日常生活中的一部分,小至智能手机、智能手表,大到卫星、飞机,半导体已经无处不在。 根据应用场景的不同,半导体可以分为四个大类,分别是:集成电路、分立器件、光电器件及传感器。集成电路是四类半导体器件中应用最为广泛的,据世界半导体贸易统计协会统计,2020年集成电路占全球半导体各类器件市场的82.03%,相比2019年占比80.8%又有一定提升。集成电路产业既是当前国际政治和经济竞争的重要砝码,也是国际竞争最激烈以及全球资源流动和配置最彻底的产业。

图1 半导体分类 集成电路是采用特定的制造工艺,将晶体管、电容、电阻 和电感等元件以及布线互连,制作在若干块半导体晶片或者介质基片 上,进而封装在一个管壳内,变成具有某种电路功能的微型电子器件。 集成电路主要分为数字集成电路和模拟集成电路,其中数字集成电路主要包括逻辑器件、储存器和微处理器。逻辑器件是进行逻辑计算的集成电路;存储器是用来存储程序和各种数据信息的记忆部件;微处理器可完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作;模拟器件是模拟电路集成在一起用来处理模拟信号的芯片,如运算放大器、模拟乘法器、锁相环、电源管理芯片等。

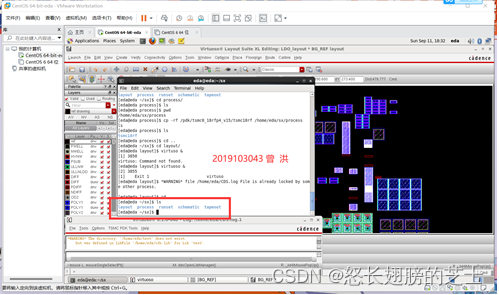

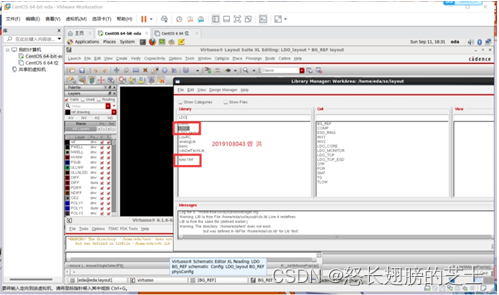

图2 2020年半导体各类期间市场规模占比 (2)行业背景 集成电路版图设计是连接设计与制造工厂的桥梁,主要从事芯片物理结构分析、版图编辑、逻辑分析、版图物理验证、联系代工厂、版图自动布局布线、建立后端设计流程等。版图设计人员必须懂得集成电路设计与制造的流程、原理及相关知识,更要掌握芯片的物理结构分析、版图编辑、逻辑分析、版图物理验证等专业技能。 (3)行业的生产、设计、研究开发流程。 集成电路版图设计的职业定义为:通过EDA设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII数据。 通常由模拟电路设计者进行对模拟电路的设计,生成电路及网表文件,交由版图设计者进行绘制。版图设计者在绘制过程中需要与模拟电路设计者进行大量的交流及讨论,这关系到电路最终的实现及最终芯片的性能。这些讨论涉及到电流的走向,大小;需要匹配器件的摆放;模块的摆放与信号流的走向的关系;电路中MOS管、电阻、电容对精度的要求;易受干扰的电压传输线、高频信号传输线的走线问题。而且要确保金属线的宽度和引线孔的数目能够满足要求(各通路的电流在典型情况和最坏情况的大小) ,尤其是电源线和地线的宽度。 在进行完这些讨论之后,版图设计者根据这些讨论所得到的信息及电路原理图开始着手对版图的绘制,在绘制过程中遇到的问题,比如牵涉到敏感信号的走线,高精度匹配器件的摆放,连接等,都需及时与模拟电路设计者进行讨论,以确保模拟电路设计者的思想及电路能以最好的方式实现。同时版图设计者需要对所采用的代工厂所提供的工艺文件,规制文件有仔细的阅读和理解,并按照这些规则进行版图的绘制。 绘制完成后需要进行DRC,即设计规则检查,以保证所绘制电路可在代工厂的所提供的工艺精度下完成芯片的制造。如有错误则需进行相关修改,直至满足设计规则为止。 完成DRC后需要进行LVS,即版图与电路图的对照,通常根据LVS的规则文件对版图所生成的网表与模拟电路设计者所提供的电路网表文件进行对照,确保版图的物理:连接与电路设计者所设计的电路一致,如有错误进行相关修改,直至与电路网表一致为止。 在完成DRC和LVS之后还需进行版图的寄生参数提取,所提取的数据包括寄生电阻,寄生电容,寄生电感(射频电路中会考虑此项)。电路设计者根据这些参数进行后仿真并与原电路的仿真结果进行比较,如有较大差距,则需与版图设计者讨论,交由版图设计者进行修改,直至满足仿真结果为止。 (4)项目对环境、社会和可持续发展的影响。 本次实习项目主要是BG版图布局、绘制、验证及修改。 近几年来,模拟集成电路设计技术随着CMOS工艺技术仪器得到了飞速的发展,芯片系统集成技术已经受到学术界及工业界广泛关注。随着电路系统结构的进一步复杂化,对模拟电路基本模块,如A/D和D/A转化器、滤波器电路以及锁相环等电路提出了更高精度及速度的要求。由于BG电路的输出电压及电流几乎不受稳定电源电压变化的影响,这就使得片内集成的带BG电路成了模拟集成电路芯片中不可缺少的关键部件。 2、实习项目具体实施方案及实习成果要求:能够对实习中所需要完成的工程项目进行研究,设计并实施实验,对实验结果进行分析与解释;或能够利用各种工具,进行建模、仿真与模拟,有仿真模拟等结果。 1)基础理论知识讲解 在完整电路实战之前,老师通过复习系列模拟集成电路的相关基础理论知识,从器件原理浅入再详细到讲解本次实习的BG电路,使我们进一步了解实习内容。 在大致复习了相关基础理论知识、添加完电路之后,老师介绍了各个工具和快捷键的使用方式,并带领着我们一步步熟悉cadence软件的基本操作。 (1)centos常用命令 文件和目录: # cd /home进入 '/home' 目录 # cd ..返回上一级目录 # cd ../..返回上两级目录 # cd -返回上次所在目录 # ls查看目录中的文件 # ls -a显示隐藏文件 # ls -l显示详细信息 # pwd显示工作路径 # mkdir dir1创建文件夹'dir1' # mkdir dir1 dir2同时创建文件夹dir1 dir2 # mv dir1移动/重命名文件夹 # rm -f file1删除 'file1' # rm -rf dir1删除 'dir1' 目录及其子目录内容 压缩和解压: # tar -zcvf archive.tar.gz file1 把file1打包成 archive.tar # tar -zxvf archive.tar 把 archive.tar解压 常用快捷键: [鼠标中间键] 粘贴突出显示的文本。 使用鼠标左键来选择文本,把光标指向想粘贴文本的地方;点击鼠标中间键来粘贴。 [Tab] 命令行自动补全。 键入命令或文件名的前几个字符,然后按 [Tab] 键,它会自动补全命令或显示匹配键入字符的所有命令。 (2)Cadence常用快捷键 (i)schematic常用快捷键 F:整图居中显示 U:撤销上一次操作 Esc:清楚刚键入的命令 C:复制 M:移动 Shift+M:移动器件但不移动连线 Delete:删除 I:添加元器件 P:添加端口 R:旋转器件并拖动连线 Q:属性编辑 L:添加线名 Shift+L:标注 (ii)Layout常用快捷键 Shift+Z:缩小 Ctrl+Z:放大 F:整图居中显示 U:撤销上一次操作 Esc:清楚刚键入的命令 C:复制 M:移动 Q:显示属性 Delete:删除 R:画矩形 P: 插入Path K:标尺工具 Shift+K:清除所有标尺 Shift+C:裁切 Ctrl +D:取消选择,这个也可用鼠标点击空白区域实现。 S:拉伸工具Stretch,框选要拉伸图形,再拉伸。 3)项目库搭建在介绍相关指令的同时,老师也带领我们用相关指令建立文件夹、在软件中添加新的库以及修改库的路径以安装好虚拟机Linux的软件环境。

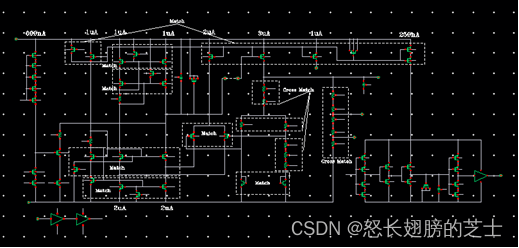

在搭建好环境后,老师讲解了两种保护环的区别和应用、修改参数设置的操作、打包为成熟的规则文件的方法等以及相关注意事项。老师根据电路中每个器件之间的联系和作用以及互相构成部分以PMOS、NMOS电流镜以及三极管的版图器件匹配为例介绍了器件匹配和实现方法。在大致掌握了软件的基本运用之后,我们开始就老师讲解的相关内容进行实操。

图6 电流镜的匹配

图7 电流镜的匹配

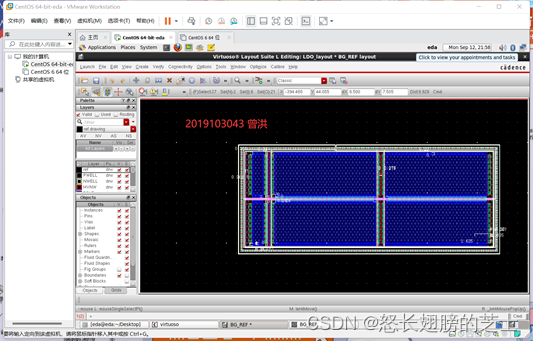

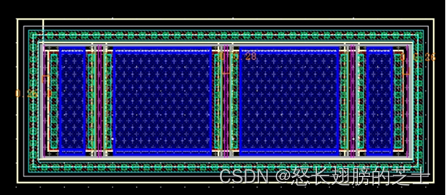

图8 三极管的匹配 在此基础上,在了解了差分对交叉匹配的画法电容块匹配以及电阻交指匹配的画法后,我们陆续完成了剩下部分器件的匹配,基本完成整个BG电路的版图匹配设计。 5)BG版图布局在进一步明白电路的连接关系以及各个匹配部件在电路中电流流向的关系后,我们根据版图的需要以及老师介绍的工业制作要求,我们进行了全局整体布置。

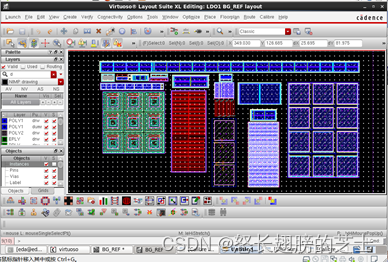

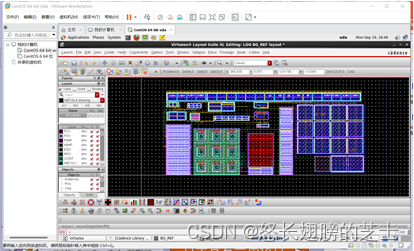

图9 版图布局 在老师的一对一指导下,我明白了我的版于布局的一些不妥之处,结合老师补充的版图中电位隔离措施、噪声模块与敏感模块区分、噪声信号屏蔽方式、和敏感信号保护方式等注意事项,调整我的版图布局并进行连线。

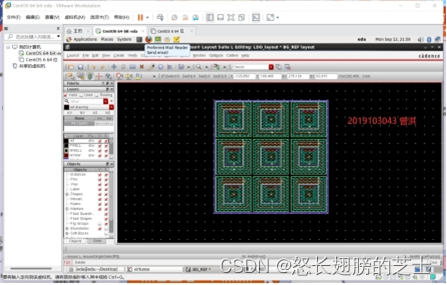

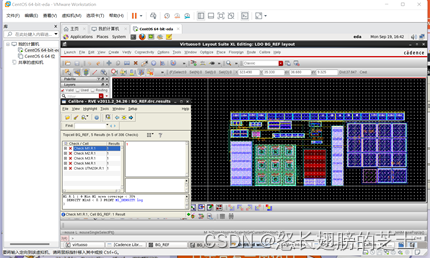

图10 版图连线布局 10)BG版图验证修改(1)DRC 在布局完成之后,对于整体电路进行了DRC仿真确保版图每个层级之间不会因为放置不当等原因出现版图规则错误。 一般错误的格式为【X.错误类型】。X为具体哪层,主要有金属层M1\M2\M3、POLY层、有源区OD2、P阱pwell、N阱Nwell等等。常见的错误有以S结尾的面积错误、以W结尾的宽度错误、以R结尾的密度错误(可忽略)、以A结尾的面积错误、LUP.6的闩锁效应等。

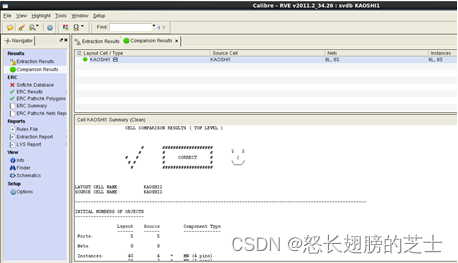

图11 DRC验证 (2)LVS 通过DRC验证后,进行LVS验证。打开LVS界面,设置好配置文件,点击Run LVS。出现笑脸,LVS通过。

图12 LVS验证 7、版图寄生参数提取、版图后仿、数据打包在讲解完所有实习内容后,老师也给我们讲述了寄生参数的提取、版图的后仿以及数据完成之后的打包等操作。 |

【本文地址】

今日新闻 |

推荐新闻 |

图3 BG原理图

图3 BG原理图 图4 电路和库导入图

图4 电路和库导入图