数字IC校招100问 附解答(完结撒花6666) |

您所在的位置:网站首页 › buffer和inverter优缺点 › 数字IC校招100问 附解答(完结撒花6666) |

数字IC校招100问 附解答(完结撒花6666)

|

数字IC校招100问 附解答(完结撒花6666)

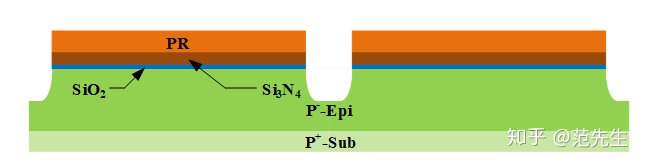

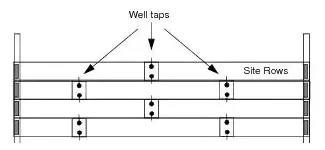

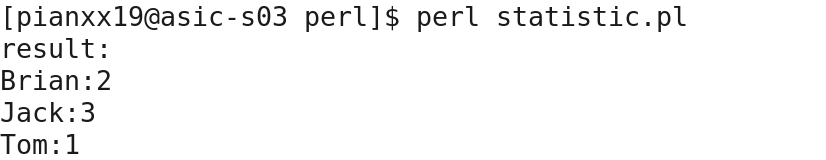

1.请说一下数字后端主要做了什么事情?(概述性,难度1) 1.FloorPlan 2.Place 3.CTS 4.routing 5.ECO 6.chip finish process 7.physical verfication netlist ——>GDSII ~ 5.手修,logic ECO 和 physical ECO。logic是指netlist变更了。physical是指fix timing和drc。 6:插入mental fill cell 7:主要完成timing,power signoff,LVS和DRC。 ~ 2. 请简单描述一下数字后端的基本流程?(概述性,难度1) ~ 如上 3. 请说一下CMOS集成电路工艺的大致步骤是什么?(工艺,难度2) https://zhuanlan.zhihu.com/p/339876176 第一步:有源区的形成。在p衬底上做p外延,再生长一层SiO2,使用光刻胶(PR),用致密SiO2分隔出左右两个有源区。 ~

4.请说一下memory的摆放规则?(floorplan,难度2) ~ a.memory,Ip,io,standard cell的orientation poly的方向一致。 b.通过data flow或者create_plan_group的逻辑关系摆放。 c.memory的output pin尽量靠近core logic区域,节约绕线资源和timing。 d.memory之间空间不能过大也不能过小,过大浪费资源,不能太小,如果有标准单元放置的话,要保证有power strap。 e.放置在芯片的boundary区域,原因之一hard macro的高度可能会阻碍到标准单元的power strip。meomory和Io macro其它的hard macro之间存在信号传输,考虑不同的信号传输关系。 5.welltap, endcap cell的作用,以及如何摆放?(place,难度2) ~ welltap:n-well就会连接到VDD, substrate就会连接到GND。我们对于一个NWELL(也就是说一行)我们仅需要一个连接到VDD,同理substrate也是,如果说我们把这些去掉的话,那么我们就会省下来巨大的面积。所以就会有 “tap-less” libraries,但是由于仅有一个tap会由于NWEL和substrate的阻值而导致latch-up的出现,故而我们会在一定距离内添加well tap单元来避免latch-up效应。 endcap cell:一般是摆放在Macro周围和每条row的首尾两端,主要目的是确保Macro周围的环境和core logic的环境是一样的。 ~ 6. Place之后有timing violation,应该怎么办?(place,难度3) 各个阶段如何fix setup 7.CTS的目的是什么?怎么样是一个合格的clock tree? (CTS,难度3) CTS的目的就是为了减小global skew。 时钟树不需要做到绝对的平衡,如useful skew,更关注于设计的时序 除了PPA(performance、power、area)之外,时钟树还应该robust。即所谓设计中的时钟树在任意设计需求的corner下都能满足时序。这点对提高良率的意义重大。 考虑OCV等因素后,对称使得时钟树更加强壮。到达每个Reg的时钟路径拓扑结构、级数和Inverter/Buf都一样是最理想的。(不考虑usefull skew的需求) 使用专用的、较少的Inverter/Buf也可以降低OCV对时钟树鲁棒性的影响 8.为什么时钟树需要平衡?不平衡的时钟树有什么缺点?(CTS,难度2) 对于快速设计,时钟树的skew和latency影响时序收敛、功耗和面积。 balance 可以使得timing收敛简单些 对于慢速设计,时钟树的skew和latency对时序收敛的影响重要性下降。但是对于skew大的时钟树,工具修复时序会增加更多的面积和功耗。创造一个skew小的时钟树,虽然看似在时钟树上多用了buffer,但是会减少在修复时序问题时需要的buffer 所以,一个balance对于时序收敛、面积和功耗都是有好处的。 9.什么是latch up效应? (工艺,难度2) 查看闩锁效应文章。 10.芯片功耗主要包含哪些内容?(power,难度4) ~ 总结ing等待整理。 11. 请写一段脚本,统计下图中人名出现的次数,并按从多到少次数排列,语言任意(脚本,难度3) 使用perl实现统计人名次数。 Tom Jack Brian Brian Jack Jack ~ -22. 请写一下setup, hold slack的计算公式 (时序,难度2) setup slack = Trequirement - Tarrive hold slcak = Tarrive - Trequirement 23.create_clock和create_generate_clock有什么区别?(时序,难度3) create_clock生成的是master clock,create_generate_clock是由master clock生成的,比如通过一个分频器,不会单独产生一个时钟,连接到master clock。 24.STA的基本概念,与仿真相比,它的优势是什么?(时序,难度1) 静态时序分析。 1.100%覆盖率 2.速度快 3.考虑串扰,工艺偏差的影响 25.STA在什么阶段做,各个阶段的STA都有什么区别? (时序,难度3) DC place routing都需要时序分析。 主要区别是CTS之前使用的都是虚拟时钟,SDC定义的时钟 各个阶段的时序分析model也不一样 比如DC使用的是线负载模型,routing之后就是实际的布线数据。 26.LEF文件的主要作用,它和GDSII有什么区别?(数据库,难度2) ~ LEF只描述单元的底层细节,比如端口位置,层定义和通孔定义。只用于布局布线。GDSII拥有单元的全部信息,但由于过大,不利于工具的布局布线。 -27. 了解Finfet工艺么,请简单画一下一个finfet晶体管结构示意图(工艺,难度2) 了解 MosFET/FinFET/GAFET ——鳍式晶体管还能走多远 28.列举你知道的几种修复setup timing violation的方法,该优先使用哪一种?(时序,难度4) 调整size,更换阈值电压,修复DRC(transition和load会影响延迟),流水线,useful skew 29.timing signoff报告主要有哪些内容?(时序,难度4) 1.setup hold violation 2.DRC检查,input transition,output load 3.corner是否全 4.sdc检查,后仿作为最后检查sdc的过程,比如false path 5.噪声 30.spef文件里面记录了什么内容?如何得到?(时序,难度2) 互连线寄生参数,使用starRC 31.时钟树走线和普通信号线有什么区别? (CTS,难度2) double width和double space,高层走线 32.为什么memory需要靠边摆放?(floorplan,难度3) ~ 因为和外界的数据交互比较密切 33. 静态功耗的概念,如何降低?请列举一些你知道的方法 (power,难度4) 主要是泄露功耗 1.提高阈值电压 2.电源门控 3.体偏置。进而改变阈值电压,如果正向体偏置就会提高性能。 34.芯片为什么需要采用纵横交错的走线方式? (route,难度2) ~ 减少crosstalk 列举一下你知道的修复hold timing violation的方法?(时序,难度3) ~ 1.单元面积 2.单元尺寸 3.流水线我们在修复hold violation时,buffer应该加在什么位置?(时序,难度3) 组合逻辑,DFF间路径 37.列举几个常见的drc种类?(route,难度2) 满足良率的同一金属层或者不同金属层的几何尺寸的最小值的集合,就是设计规则检查。 版图和lef文件进行比较(lef由单元lef和技术lef,这边技术lef定义设计规则,单元lef)38.CTS之前是如何计算clock path上的延迟的? (CTS,难度2) 根据sdc中clock的uncertainty(包含skew),CTS之后使用实际的CTS计算skew。 39.正则表达式的匹配1个以及1个以上的,该如何匹配? (脚本,难度1) ~ *:0个或者1个 +:1个及以上 ?:0个或者1个 40. 请说一下drv的概念,主要包含哪些内容?(时序,难度2) ~与37题一样? 41. 介绍一下CPPR的概念,为什么需要用到CPPR?(时序,难度3) 共同路径悲观消除。在OCV时需要乘以一个derate系数,共同路径的部分需要移除悲观量。 42.说一下Calibre检查drc的具体流程?(PV,难度4) 主要输入两个文件。一个是得到的版图GDSII文件和工艺厂商提供的设计规则文件。工具通过标出违反设计规则的位置,进而手工修改违规。 43.什么是天线效应(antenna effect)? 说几种你知道的修复方法?(route,难度4) 制造过程中一些游离电荷受到悬空导线的吸引。 插入二极管,跨层走线 44.动态功耗主要包含哪些部分,如何降低?请列举一些你知道的方法 (power,难度4) 包含短路功耗和开关功耗 1.降低电压 2.DVFS 3.多电压域 4.降低负载 5.降低时钟频率 45.你在学校里接触过哪种工艺?说一说这种工艺有什么特点?(工艺,难度3) ~ 45nmFreePDK TSMC28nm 46. 请简单自我介绍一下?(凑数,难度1) ~ 47. 请列举一下导入后端设计需要哪些文件?(数据库,难度1) ~ netlist 工艺库(逻辑库db lib 物理库lef) 工艺文件 TLU+ 48. 请列举几个你知道的sdc命令,并说出它的用途?(时序,难度2) create_clock create_generated_clock set_driving set_load set_input_delay set_output_delay set_case_analysis set_false_path set_multicycle_path set_max_fanout set_max_transition set_min_capacitance set_max_capacitance 49.修复timing violation时,首先应该关注什么,有哪些需要注意的点?(时序,难度5) ~ 1.逻辑 2.floorplan 3.时序路径的延迟,cell size,阈值电压,buffer 4.工具层次,group的weight 5.线延迟,插buffer CTS之前需要修复hold violation么,为什么?(CTS,难度2) 不需要。1.没有实际的CTS 2.很好修,插buffer51.在修复hold violation时,delay cell和buffer该优先使用哪一种,各有什么优缺点?(时序,难度3) ~ 特点:delay cell延迟比较大,buffer驱动能力强 较大的violation使用delay cell。 clock latency的概念,什么情况下需要设置? (时序,难度3) source latency和network latency。一般不需要设置。 1.不同clock source latency不同,考虑时序,需要设置。 2.不同时钟network latency (insert delay cell)不同时,需要考虑时序,也需要设置。53.low vt cell和high vt cell有什么区别,各有什么优缺点?(工艺,难度3) 低阈值电压开关速度快,功耗高 高阈值电压卡关速度慢,功耗低 54.如何判断floorplan摆放质量的好坏?(floorplan,难度5) 1.memory要放在边缘,和外界数据交互 2.SRAM地址线对齐 3.有关联的Macro放在一起 55.电源走线为什么需要使用高层线?(power,难度2) 1.高层金属更厚,有更强的EM能力 2.对低层信号线干扰更小 3.不会占用低层的信号线 56.请介绍几种修复drc的方法?(route,难度4) ~ 1.工具自动修,在DRC违规的地方添加routing guide,做iteration routing 2.工具抓取出DRC违例的地方,删除这些net,做routing eco。 什么是crosstalk? 为什么会产生crosstalk? 会带来什么后果?(时序,难度4) 串扰。信号线之间的干扰。产生glitch和transition time的变化。transition和delay有关系,同向transition变小,反向transition变大。glitch会产生逻辑错误。58.写过sdc么,sdc文件里,主要包含哪些内容,我们该如何约束一个设计?(时序,难度5) 基础知识如上。如何约束? 59.请说一下OCV的概念,为什么需要用到OCV,什么阶段需要OCV,如何实现?(时序,难度5) ~ 片上工艺偏差,derate Def文件的作用是什么?(数据库,难度1) ~ 器件的位置关系和时序限制 我们需要在什么阶段做formal验证?(形式验证,难度2) DC,floorplan,routing 62.综合的时候,我们是怎么计算net的delay?(综合,难度2) 根据线负载模型,由扇出计算出线长,再乘以单位线长上的电阻和电容,计算RC。利用Elmore 模型计算delay。 63.为什么选择我们公司?(凑数,难度1) ~ 64. timing signoff需要读入哪些文件?说一下具体的流程(时序,难度4) ~ netlist,STA库文件,sdc,spef core里面是如何给标准单元供电的?(power,难度2) 在floorplan阶段strap和ring,然后通过rail连接到标准单元上66.sdf文件里面记录了什么内容?如何得到?(时序,难度3) 把器件延时和线延时保存下来。 67.在生成clock tree时,我们应该使用invertor还是buffer, 为什么?(CTS,难度2) 1.选择inv,上升沿和下降沿对称 2.功耗低 3.面积小 68.你知道设置的利用率是如何计算的吗,你的设计利用率是多少?(floorplan,难度3) ~ 利用率utilization = (标准单元面积+macro面积)/ module的面积 在陈涛后端100题里有提及到相关的概念。 不同金属的utilization不一样,肯定和工艺以及芯片类型也有关系,整体来说utilization越大,对于芯片的congestion是更加不利的。 5层金属:50% 6层金属:60% 7层金属:70% 8层金属:80% 多媒体芯片利用率可以增加3%到5%,网络芯片减少3%到5% 碰到routing congestion该怎么办?(route,难度4) 1.floorplan的问题 2.调整ultilization(降低) 3.高层布线70.谈谈整个芯片设计的大概流程(概述性,难度1) 从架构定义——前端设计——后端设计——生产制造——封装——测试 71.从后端角度,对于芯片设计的要做哪些检查?(概述性,难度4) ~ LVS,DRC,timing signoff,功耗,功能,性能(频率),面积 clock时钟一般采用哪层金属走线?(CTS,难度2) 较高层的走线,一般是5,6,7;double space和double width73.温度对标准单元延迟的影响?(时序,难度1) 注意存在反偏效应,之前的博客有说。类似于耐克函数,主要是内部迁移率和阈值电压谁占主导地位。 74.下面,我们用英语对话一下(凑数,难度2) 75.rc corner有哪几种?各有什么特点? (时序,难度2) 1.Cworst 2.Cbest 3.RCworst 4.RCbest 特点:setup 考虑Cworst和RCworst;hold考虑四个角都要满足。 double pattern还有着双重的要求。 78.route之前的连线和后面最终的连线有什么区别? (route,难度3) ~ 时钟信和电源线 请说出几个你用到的后端工具,他们分别用来做什么?(概述性,难度1) ~ICC,PT 我们为什么要对net设置fanout限制? (时序,难度2) fanout太大驱动不了 库不准 81.为什么采用double width, double spacing的时钟树走线方式?(CTS,难度3) ~ EM,fanout较大,电流大。 setup和hold violation该优先修复哪种,为什么?(时序,难度3) ~ 优先修复setup。hold比较好修。并且setup决定我们的性能 DFF哪些pin需要做timing检查?(时序,难度3) 第二个锁存器的Q端口 84.clock uncertainty主要包含哪些内容?你设置了多少?(时序,难度3) ~ CTS之前 setup:clock uncertainty = jitter + skew + margin hold:clock uncertainty = skew + margin CTS之后 setup:clock uncertainty = jitter + skew + margin hold:clock uncertainty = skew + margin 主要原因是setup是在不同时间沿分析,hold是在同一时钟沿分析。 什么是IR drop? 有IR drop问题应该怎么办?(power, 难度4) 压降。分为静态和动态。静态是由于电阻分压,动态是由于门同时打开,局部电流过大。 静态主要考虑power plan增大strap密度。高层走线。 动态需要从逻辑角度进行优化,还有就是加入去耦电容。86.calibre里面检查drc和PR工具里面的drc有什么区别?(PV,难度3) ~pr阶段调用的是简化版的drc,至于为什么不用精确版的drc这个问题来说,就相当于为什么在pr阶段没有使用PT是一个道理。 什么是LVS?出现LVS violation时应该怎么办?(PV,难度4) ~ 版图原理图一致性检查,又称电气规则检查。 主要步骤将RTL抽取成spice网表,然后比对。 比对单元数量,单元个数,节点个数等。 latch和D触发器有什么区别?(工艺,难度1) ~ 两个latch组成触发器 你在学校做过后端设计项目么,有多少万门?(概述性,难度1) 90.blockage的作用,应该在什么地方添加?(floorplan,难度3) place。hard,soft,partial 91.为什么要使用物理综合,它的好处是什么?(综合,难度3) ·dc的好处?满足约束条件下,进行逻辑优化和单元库映射。 你做的这个后端项目里面时钟树是怎么生长的?(CTS,难度4) 时钟树类型93.请说一下clock gate cell的结构 (CTS,难度3) ~ 时钟前面和一个latch加一个与门,latch主要是消除毛刺 如何把clock skew减小?列举一些你知道的方法?(CTS,难度5) 插入inv95.LEC主要检查哪些内容,为什么要做? (形式验证,难度3) 以DC后的RTL和netlist为例。读入netlist,RTL和svf判断,根据逻辑锥和svf判断是否存在错误 96.为什么芯片需要在多个view下signoff? (时序,难度3) ~ 不同场景和不同的模式。 场景指比如PVT条件,比如手机芯片工作温度。 模式指手机不同工作模式,和DFT的模式(scan shifter等) 说一下检查LVS的具体流程?(PV,难度3) ~ 版图原理图一致性检查 将版图抽取出spice模型和初始netlist进行对比。 GBA和PBA分析timing有什么区别?(时序,难度3) 基于路径和基于图 99.什么是EM?有EM问题应该怎么办?(power,难度3) 电迁移。金属原子移动。 1.减小fanout 2.增加线的width 3.单元驱动能力过强 4.连线过长 100.综合的约束和后端的约束有什么区别?(综合,难度3) 综合时,模型粗略,过约SDC,时钟频率调高。 CTS之前没有真实的时钟树,uncertainty加大 PR工具和signoff工具一致性问题,margin也会有区别 |

【本文地址】

今日新闻 |

推荐新闻 |

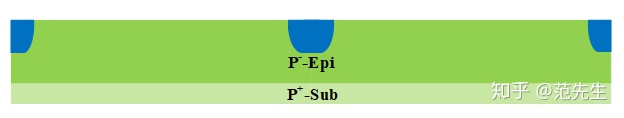

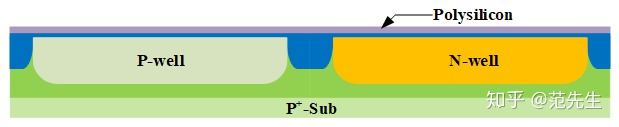

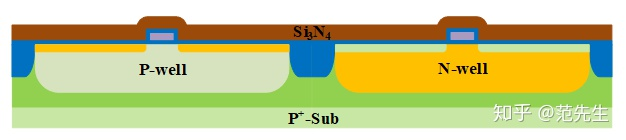

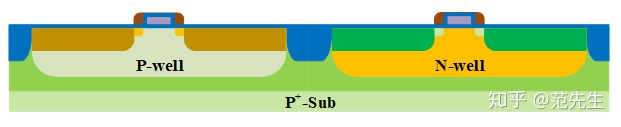

第二步:N阱和P阱的形成。N阱注入P,P阱注入B。都分3次注入,能量和剂量由低到高,称为倒置阱。

第二步:N阱和P阱的形成。N阱注入P,P阱注入B。都分3次注入,能量和剂量由低到高,称为倒置阱。

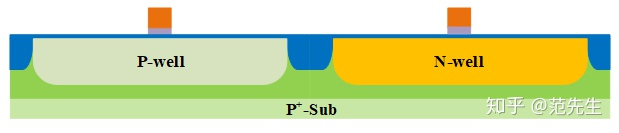

第三步:积淀一层多晶硅作为栅极材料,光刻形成栅极,最后在表面形成氧化薄层,用于隔离多晶硅和后续Si3N4形成。

第三步:积淀一层多晶硅作为栅极材料,光刻形成栅极,最后在表面形成氧化薄层,用于隔离多晶硅和后续Si3N4形成。

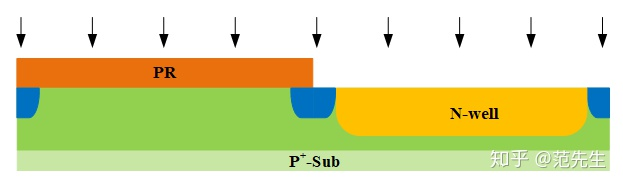

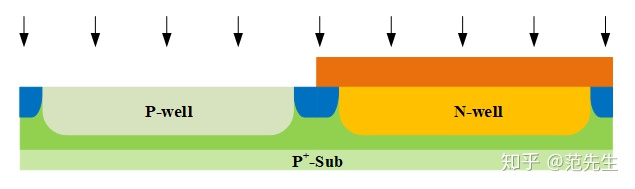

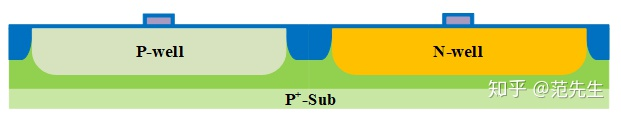

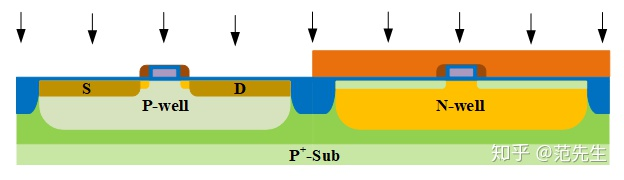

第四步:轻掺杂形成源和漏。通过光刻对P阱进行离子注入,注入AS元素;N阱注入B原子。

第四步:轻掺杂形成源和漏。通过光刻对P阱进行离子注入,注入AS元素;N阱注入B原子。

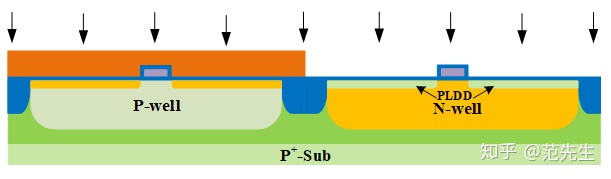

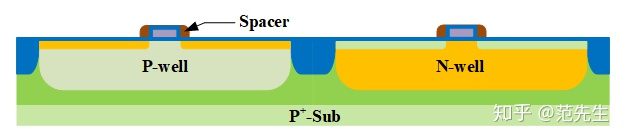

第五步:自对准工艺。通过化学气相沉积(CVD)沉积一层Si3N4.通过离子刻蚀,形成S、D区注入的阻挡墙(Spacer),对轻掺杂区域进行快速热退火(RTA )。 热退火目的:消除注入损伤,激活注入元素。

第五步:自对准工艺。通过化学气相沉积(CVD)沉积一层Si3N4.通过离子刻蚀,形成S、D区注入的阻挡墙(Spacer),对轻掺杂区域进行快速热退火(RTA )。 热退火目的:消除注入损伤,激活注入元素。

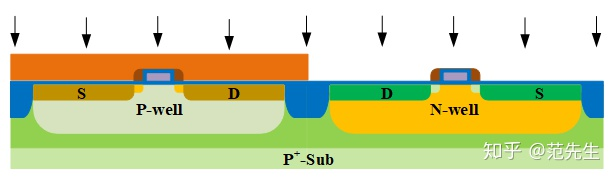

第六步:源漏制作。光刻在NMOS区域注入AS,形成源漏;在PMOS区域注入BF2+,形成Pmos区域的源漏。快速热退火,激活注入元素,消除注入损伤。刻蚀表面的SiO2,将cmos的源,漏,栅暴露出来。

第六步:源漏制作。光刻在NMOS区域注入AS,形成源漏;在PMOS区域注入BF2+,形成Pmos区域的源漏。快速热退火,激活注入元素,消除注入损伤。刻蚀表面的SiO2,将cmos的源,漏,栅暴露出来。

第七步:金属层的制造和金属层间通孔(VIA由金属钨制造)。

第七步:金属层的制造和金属层间通孔(VIA由金属钨制造)。

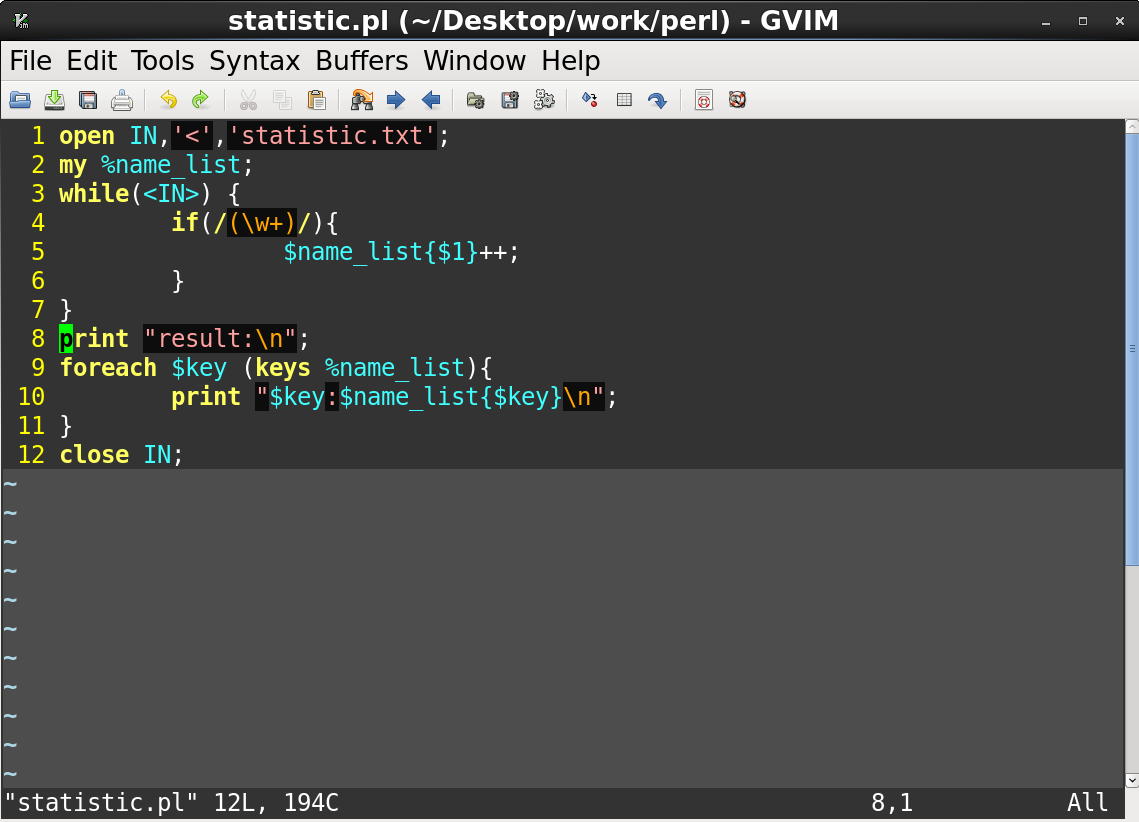

思路: 1.以句柄形式读入文件每一行 2.对每一行进行正则匹配 3.对匹配到名字,将它的value+1 4.遍历hash数组,输出结果

思路: 1.以句柄形式读入文件每一行 2.对每一行进行正则匹配 3.对匹配到名字,将它的value+1 4.遍历hash数组,输出结果

76.为什么我们需要优先修复transition和cap? (时序,难度2) ~ 因为这样单元库的数据才足够准。 提高芯片的良率

76.为什么我们需要优先修复transition和cap? (时序,难度2) ~ 因为这样单元库的数据才足够准。 提高芯片的良率