|

APB协议讲解

1. APB介绍1.1 APB的产生1.2 APB的功能1.3 APB协议的特点1.4 APB协议的英文文档很短,建议看原文

2. APB协议的信号列表如下图所示(取自APB4协议)3. APB时序介绍3.1 APB2时序图介绍3.1.1 下图为APB2的写操作时序图3.1.2下图为APB2的读操作时序图

3.2 APB3时序图介绍3.2.1 写操作,无等待3.2.3 写操作,有等待3.2.3 读操作,无等待时序图3.2.4 读操作,有等待时序图3.2.5 写操作 PSLVERR时序图3.2.6 读操作PSLVERR时序图

3.3 APB4时序说明3.3.1 PSTRB信号3.3.2 PRTOT

4. 对于APB的master和slave的设计

声明:本文参考了Miracle_ICdv和Mr.Marc的博客,如有侵权,请与我联系!

1. APB介绍

1.1 APB的产生

APB(advanced Peripheral Bus)协议是ARM公司中AMBA协议的一种。最早的APB协议现在叫做APB2,2003年ARM公司发布了APB3,2010年发布APB4。APB协议是向下兼容的,随着时间的推移,根据实际需求,APB3在APB2的基础上添加一些功能,APB4在APB3的基础上再添加了一些功能。现在我们所说的APB总线一般是指APB3,APB4增加的功能很少被使用到。

1.2 APB的功能

一个典型的APB总线架构如下图所示:APB使用的目的是实现与外围低功耗设备,低速设备进行数据传输。在APB总线中,唯一的M为APB bridge,其他的一些低速低功率的外围设备均为slave。

1.3 APB协议的特点

低成本。低功耗。低带宽。无流水线结构。所有信号的跳变仅与时钟上升沿相关。每次传输至少需要两个时钟周期。

1.4 APB协议的英文文档很短,建议看原文

2. APB协议的信号列表如下图所示(取自APB4协议)

中文版如下 中文版如下

signalDescripionPCLK时钟。APB协议里所有的数据传输都在PCLK上升沿进行PRESETn复位。低电平有效PADDRAPB地址总线。最大宽度为32位PSELx选通。APB master会将此信号生成给每个slave。它指示已选择的slave,并且需要进行数据传输。 每个slave都有一个PSELx信号。PENABLE使能。当它为高时,表示数据有效PWRITE读写控制。为高时表示写操作,为低时表示读操作PWDATA写数据。master通过PWDATA将数据写到slave,该总线最大宽度为32位PRDATA读数据。master通过PRDATA将数据从slave读取回来,该总线最大宽度为32位

3. APB时序介绍

3.1 APB2时序图介绍

3.1.1 下图为APB2的写操作时序图

T0-T1:初始状态 T1-T2:master把PADDR和PWRITE放在总线上,通过PSEL选择一个slave,slave得知mater将要进行一次写操作,并且master把需要写进slave的data也放到总线上。 T2:PENABLE为高,表示当前数据有效,并且master将data写入slave T3:数据传输结束,再次回到初始状态 T0-T1:初始状态 T1-T2:master把PADDR和PWRITE放在总线上,通过PSEL选择一个slave,slave得知mater将要进行一次写操作,并且master把需要写进slave的data也放到总线上。 T2:PENABLE为高,表示当前数据有效,并且master将data写入slave T3:数据传输结束,再次回到初始状态

3.1.2下图为APB2的读操作时序图

所有的数据都是在PCLK上升沿跳变的 T0-T1:初始状态,准备开始数据传输 T1时刻:master向总线上发送了地址,这个地址是slave的地址;并且把PWRITE拉低,说明这次数据传输是一次读数据。PSEL拉高,APB协议里可能是有一个master,多个slave,当PADDR将地址发到总线上后,PSEL选择哪一个slave也就定了。 T1-T2时刻:保持现状不变,这个时候slave收到了mater的地址,读写控制,salve得知自己要讲这个地址对应的数据发送到master,所以它会做好准备。 T3时刻:PENABLE也就是使能信号拉高,这个时候也就是master通知slave进行PRDATA的传输 总结一下:一开始我们就说到,APB数据传输至少需要两个周期,也就是T1-T3。其实很简单,第一个周期做准备工作(把PADDR,PWRITE,PSEL发送到总线),第二个周期进行传输读或写的data(PENABLE拉高,表面当前时刻,数据有效,是master想要的数据!) 所有的数据都是在PCLK上升沿跳变的 T0-T1:初始状态,准备开始数据传输 T1时刻:master向总线上发送了地址,这个地址是slave的地址;并且把PWRITE拉低,说明这次数据传输是一次读数据。PSEL拉高,APB协议里可能是有一个master,多个slave,当PADDR将地址发到总线上后,PSEL选择哪一个slave也就定了。 T1-T2时刻:保持现状不变,这个时候slave收到了mater的地址,读写控制,salve得知自己要讲这个地址对应的数据发送到master,所以它会做好准备。 T3时刻:PENABLE也就是使能信号拉高,这个时候也就是master通知slave进行PRDATA的传输 总结一下:一开始我们就说到,APB数据传输至少需要两个周期,也就是T1-T3。其实很简单,第一个周期做准备工作(把PADDR,PWRITE,PSEL发送到总线),第二个周期进行传输读或写的data(PENABLE拉高,表面当前时刻,数据有效,是master想要的数据!)

3.2 APB3时序图介绍

APB3在APB2的基础上增加了两个端口,PREADY和PSLVERR。PREADY用于扩展APB的传输。PSLVERR是一个错误反馈信号,表示当前传输发生了错误。

3.2.1 写操作,无等待

3.2.3 写操作,有等待

当PSEL和PENABLE都为高的时候,PREADY为低,说明slave没有准备好,再给他一点时间,在T4时刻这条虚线,发现PSEL和PENABLE为高,但是PREADY还是为低,继续等待。在T5时刻这条虚线,发现PSEL,PENABLE,PREADY都为高,说明这个时候采样的Data是我们想要读取的data。 当PSEL和PENABLE都为高的时候,PREADY为低,说明slave没有准备好,再给他一点时间,在T4时刻这条虚线,发现PSEL和PENABLE为高,但是PREADY还是为低,继续等待。在T5时刻这条虚线,发现PSEL,PENABLE,PREADY都为高,说明这个时候采样的Data是我们想要读取的data。

3.2.3 读操作,无等待时序图

3.2.4 读操作,有等待时序图

3.2.5 写操作 PSLVERR时序图

PSLVERR只在APB传输的最后一个周期有效, 也就是说当PSEL,PENABLE和PREADY均为1时是有效的,在其他时间是无效的。当一些APB模块不支持PSLVERR时,比如只支持APB3协议,可以将这个pad接0. PSLVERR只在APB传输的最后一个周期有效, 也就是说当PSEL,PENABLE和PREADY均为1时是有效的,在其他时间是无效的。当一些APB模块不支持PSLVERR时,比如只支持APB3协议,可以将这个pad接0.

3.2.6 读操作PSLVERR时序图

读操作的机理与写操作一样。 这里要说的是 PSLVERR在系统中的连接映射关系,PSLVERR需要连接到AXI的RRESP/BRESP或者AHB的HRESP信号。返回PSLVERR说明这次读写发生了问题。至于产生error信号如何处理协议并没有规定。 读操作的机理与写操作一样。 这里要说的是 PSLVERR在系统中的连接映射关系,PSLVERR需要连接到AXI的RRESP/BRESP或者AHB的HRESP信号。返回PSLVERR说明这次读写发生了问题。至于产生error信号如何处理协议并没有规定。

3.3 APB4时序说明

APB4在APB3的基础上添加了两个端口,一个是PPROT,一个是PSTRB.

3.3.1 PSTRB信号

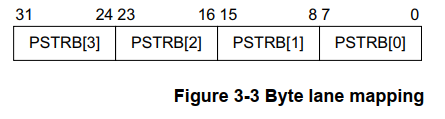

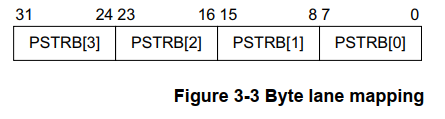

写选通信号是指当所传输数据的位宽小于设计中的数据位宽时,可以通过指定PSTRB信号有效的方式来指定哪些数据位是有效的。 下图显示了32位数据总线上的这种关系。

写选通信号PSTRB使写数据总线上的稀疏数据传输成为可能。 每个写选通信号对应于写数据总线的一个字节。 当置为高电平时,写选通脉冲指示写数据总线的相应字节通道包含有效信息。 写数据总线的每八位有一个写选通脉冲,因此PSTRB [n]对应于PWDATA [(8n + 7): ( 8n)]。

当进行读操作时,master需要驱动PSTRB为0。

3.3.2 PRTOT

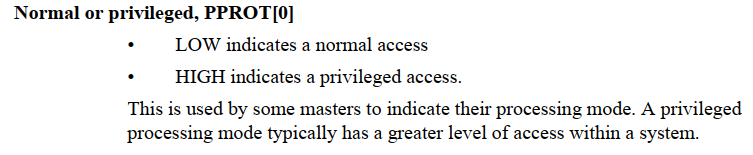

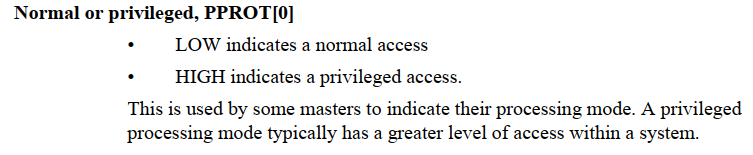

PROT的主要功能是对APB的读写操作进行保护,指示是secure-access还是no secure-access。直接上英文原文

4. 对于APB的master和slave的设计

个人认为最重要的是了解状态机的设计,根据状态机也比较容易进行设计。状态机图如下图所示:

IDLE: 状态是APB的默认状态。SETUP: 当发起一个传输时,master会选择一个PSEl进行拉高,PENABLE为0,这指示传输的第一个周期。ACCESS:当PSEL为1, PENABLE为1时,看PREADY的状态,PREADY是指slave是否准备好了传输数据,在时钟的上升沿检测到PREADY为1,则该次读写传输结束。如果还要继续传输数据,则转回到SETUP状态,如果不继续传输数据则转回到IDLE状态,这个是由master来控制的,个人感觉转移条件是master是否继续传输数据。

|

中文版如下

中文版如下 T0-T1:初始状态 T1-T2:master把PADDR和PWRITE放在总线上,通过PSEL选择一个slave,slave得知mater将要进行一次写操作,并且master把需要写进slave的data也放到总线上。 T2:PENABLE为高,表示当前数据有效,并且master将data写入slave T3:数据传输结束,再次回到初始状态

T0-T1:初始状态 T1-T2:master把PADDR和PWRITE放在总线上,通过PSEL选择一个slave,slave得知mater将要进行一次写操作,并且master把需要写进slave的data也放到总线上。 T2:PENABLE为高,表示当前数据有效,并且master将data写入slave T3:数据传输结束,再次回到初始状态 所有的数据都是在PCLK上升沿跳变的 T0-T1:初始状态,准备开始数据传输 T1时刻:master向总线上发送了地址,这个地址是slave的地址;并且把PWRITE拉低,说明这次数据传输是一次读数据。PSEL拉高,APB协议里可能是有一个master,多个slave,当PADDR将地址发到总线上后,PSEL选择哪一个slave也就定了。 T1-T2时刻:保持现状不变,这个时候slave收到了mater的地址,读写控制,salve得知自己要讲这个地址对应的数据发送到master,所以它会做好准备。 T3时刻:PENABLE也就是使能信号拉高,这个时候也就是master通知slave进行PRDATA的传输 总结一下:一开始我们就说到,APB数据传输至少需要两个周期,也就是T1-T3。其实很简单,第一个周期做准备工作(把PADDR,PWRITE,PSEL发送到总线),第二个周期进行传输读或写的data(PENABLE拉高,表面当前时刻,数据有效,是master想要的数据!)

所有的数据都是在PCLK上升沿跳变的 T0-T1:初始状态,准备开始数据传输 T1时刻:master向总线上发送了地址,这个地址是slave的地址;并且把PWRITE拉低,说明这次数据传输是一次读数据。PSEL拉高,APB协议里可能是有一个master,多个slave,当PADDR将地址发到总线上后,PSEL选择哪一个slave也就定了。 T1-T2时刻:保持现状不变,这个时候slave收到了mater的地址,读写控制,salve得知自己要讲这个地址对应的数据发送到master,所以它会做好准备。 T3时刻:PENABLE也就是使能信号拉高,这个时候也就是master通知slave进行PRDATA的传输 总结一下:一开始我们就说到,APB数据传输至少需要两个周期,也就是T1-T3。其实很简单,第一个周期做准备工作(把PADDR,PWRITE,PSEL发送到总线),第二个周期进行传输读或写的data(PENABLE拉高,表面当前时刻,数据有效,是master想要的数据!)

当PSEL和PENABLE都为高的时候,PREADY为低,说明slave没有准备好,再给他一点时间,在T4时刻这条虚线,发现PSEL和PENABLE为高,但是PREADY还是为低,继续等待。在T5时刻这条虚线,发现PSEL,PENABLE,PREADY都为高,说明这个时候采样的Data是我们想要读取的data。

当PSEL和PENABLE都为高的时候,PREADY为低,说明slave没有准备好,再给他一点时间,在T4时刻这条虚线,发现PSEL和PENABLE为高,但是PREADY还是为低,继续等待。在T5时刻这条虚线,发现PSEL,PENABLE,PREADY都为高,说明这个时候采样的Data是我们想要读取的data。

PSLVERR只在APB传输的最后一个周期有效, 也就是说当PSEL,PENABLE和PREADY均为1时是有效的,在其他时间是无效的。当一些APB模块不支持PSLVERR时,比如只支持APB3协议,可以将这个pad接0.

PSLVERR只在APB传输的最后一个周期有效, 也就是说当PSEL,PENABLE和PREADY均为1时是有效的,在其他时间是无效的。当一些APB模块不支持PSLVERR时,比如只支持APB3协议,可以将这个pad接0. 读操作的机理与写操作一样。 这里要说的是 PSLVERR在系统中的连接映射关系,PSLVERR需要连接到AXI的RRESP/BRESP或者AHB的HRESP信号。返回PSLVERR说明这次读写发生了问题。至于产生error信号如何处理协议并没有规定。

读操作的机理与写操作一样。 这里要说的是 PSLVERR在系统中的连接映射关系,PSLVERR需要连接到AXI的RRESP/BRESP或者AHB的HRESP信号。返回PSLVERR说明这次读写发生了问题。至于产生error信号如何处理协议并没有规定。