Cadence Allegro 17.4学习记录开始02 |

您所在的位置:网站首页 › allegro插件分析 › Cadence Allegro 17.4学习记录开始02 |

Cadence Allegro 17.4学习记录开始02

|

目录

Cadence Allegro 17.4学习记录开始02-原理图Capture CIS 17.4一、元件库的复用1、从已有原理图文件中复制元器件

二、绘制原理图1、绘制原理图之前,软件设置2、放置元器件3、编辑元器件4、原理图电气互连、 网络标号、 分页符连接、 总线的使用1、电气连接2、网络标号3、分页符连接4、总线

5、快速放置之重复操作F46、快速复制之Ctrl7、批量浏览8、find命令9、Design Cache操作(元件批量替换/更新)10、元件操作a、元件移动b、元件旋转c、元件镜像:d、元件属性浏览

11、添加/修改封装12、文本处理13、原理图注释操作(annotate):原理图编号(位号)14、原理图设计方式平铺式结构设计方式层叠式结构设计方式

15、原理图中添加差分属性

三、原理图DRC检查四、原理图生成网表1、第一方网表2、第三方网表AllegroADPADS

总结

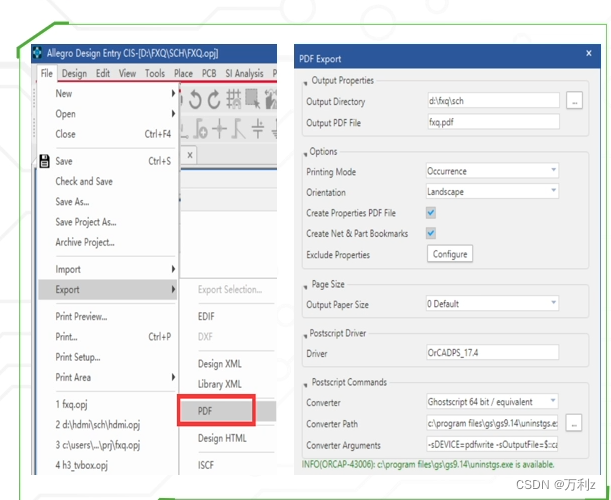

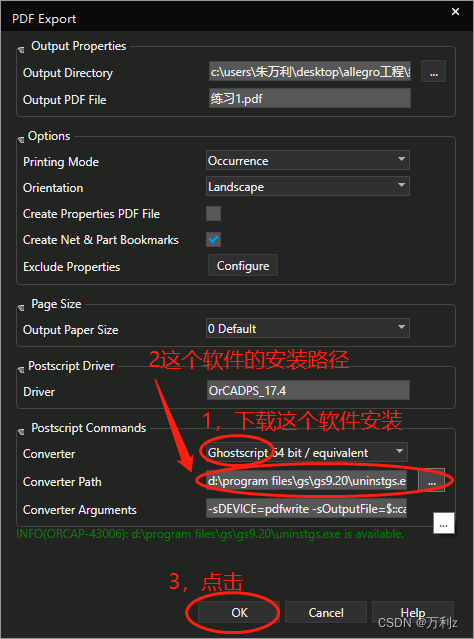

五、原理图导出BOM六、原理图导出PDF文档方法1:使用打印导出PDF方法2: 使用PDF工具导出,17.4版本才有的功能

七、总结

Cadence Allegro 17.4学习记录开始02-原理图Capture CIS 17.4

一、元件库的复用

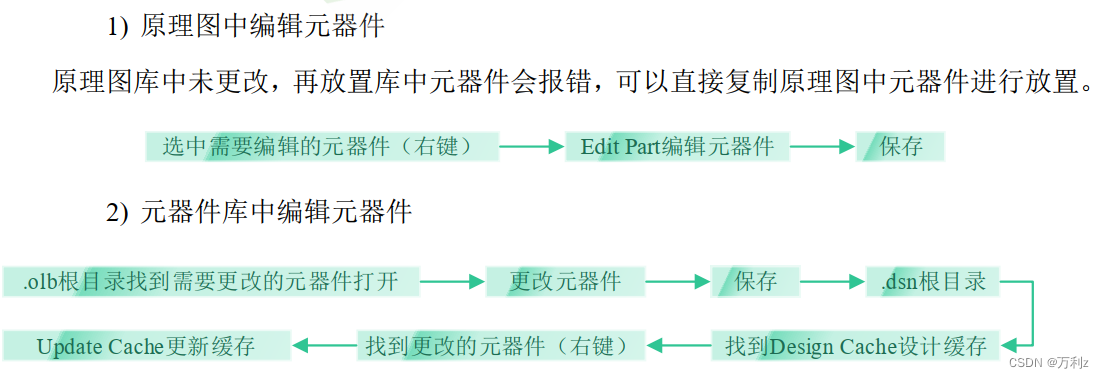

继续上一章的内容,先开始介绍元件库的复用。 原理图的后缀:DSN 原理图元件库的后缀:OLB 1、从已有原理图文件中复制元器件 从原理图缓存中复制元器件 从原理图中复制元器件 从原理图中复制元器件  二、绘制原理图

1、绘制原理图之前,软件设置

二、绘制原理图

1、绘制原理图之前,软件设置

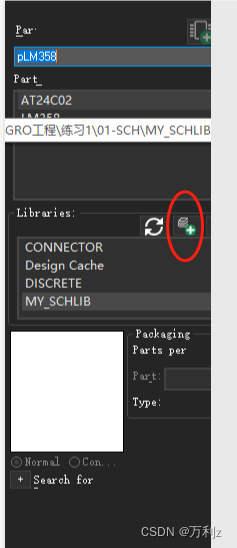

可以设计自己喜欢的主题,和颜色。 (快捷键: P) 在绘制原理图的界面下,工具栏->Place->Part,或直接使用快捷键P,即可打开元件库入口 如下图所示,选择红框选中的按钮,即可选择官方内置库或者第三方库,官方库的位置以及说明已经在前面提出。然后在part部分双击对应元件即可放置对应元件。

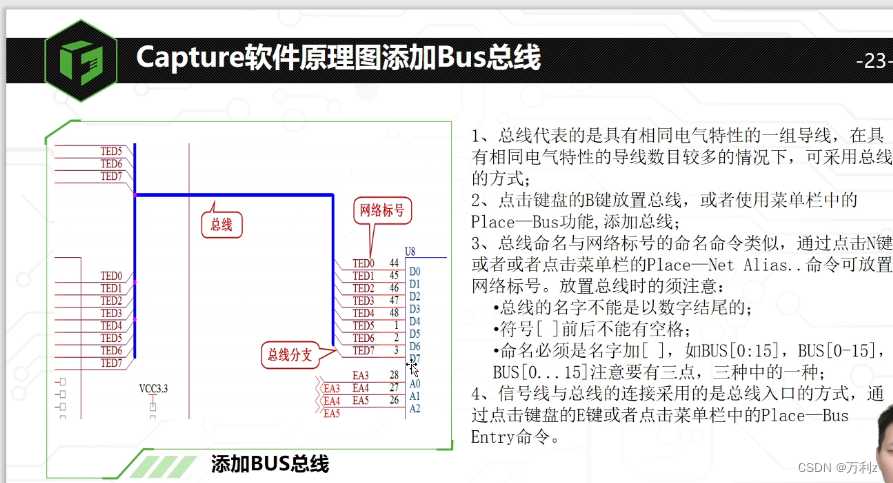

放置线条(Place wire) (快捷键: W)。 2、网络标号放置网络标号(Place net alias) (快捷键: N) 仅限于同一张原理图。 3、分页符连接放置分页符连接(Place off-page connector) 用于不同页元器件连接。 4、总线放置总线(Place bus) (快捷键: B)。 将一组数据线绘制出线并放置网络标号。靠近这组线出现绘制出总线。命名总线:放置网络标号(Place net alias) (快捷键: N) 给总线命名。 例: DATE[0:7]放置总线分支:放置总线分支(Place bus entry) (快捷键: E) 5、快速放置之重复操作F4

5、快速放置之重复操作F4

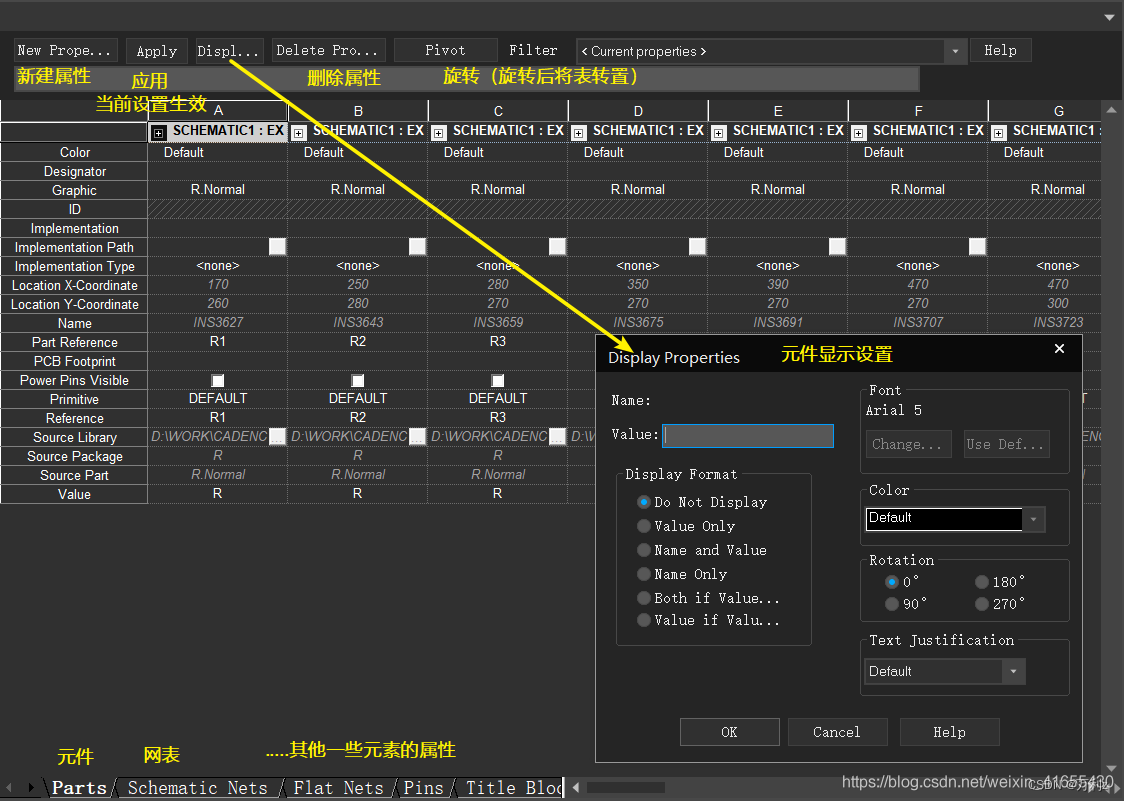

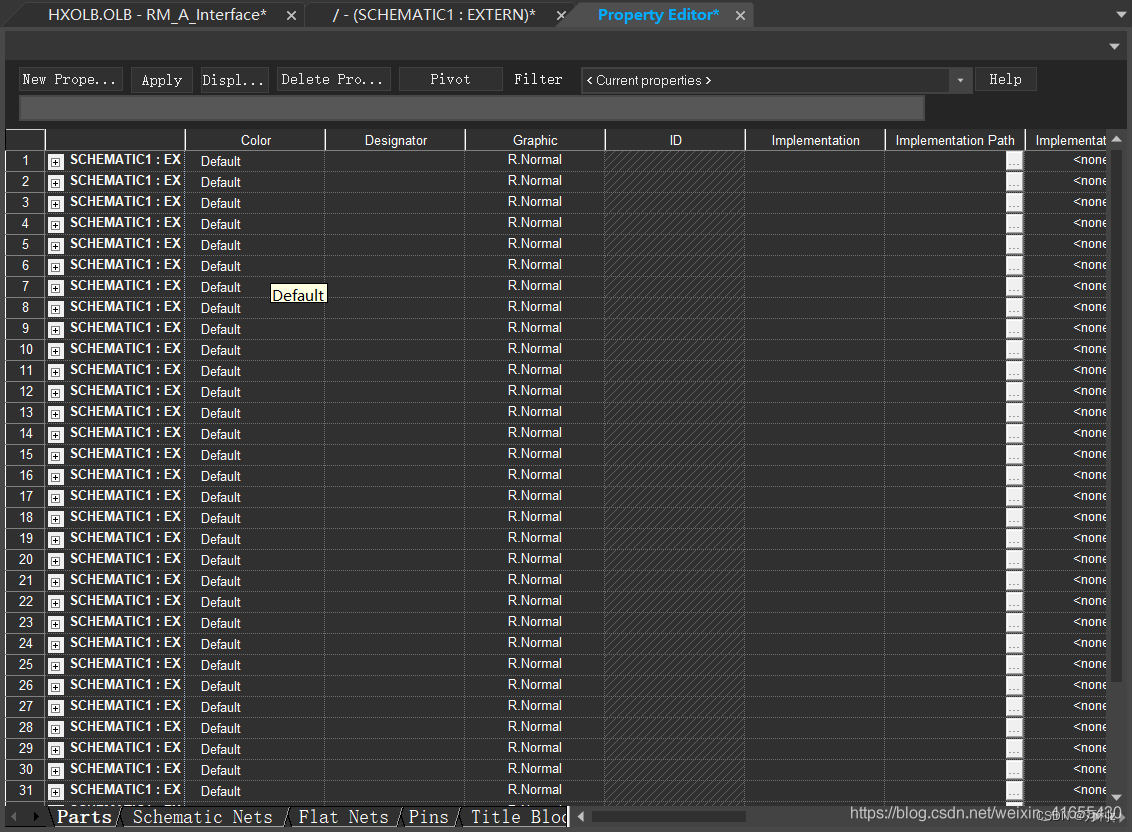

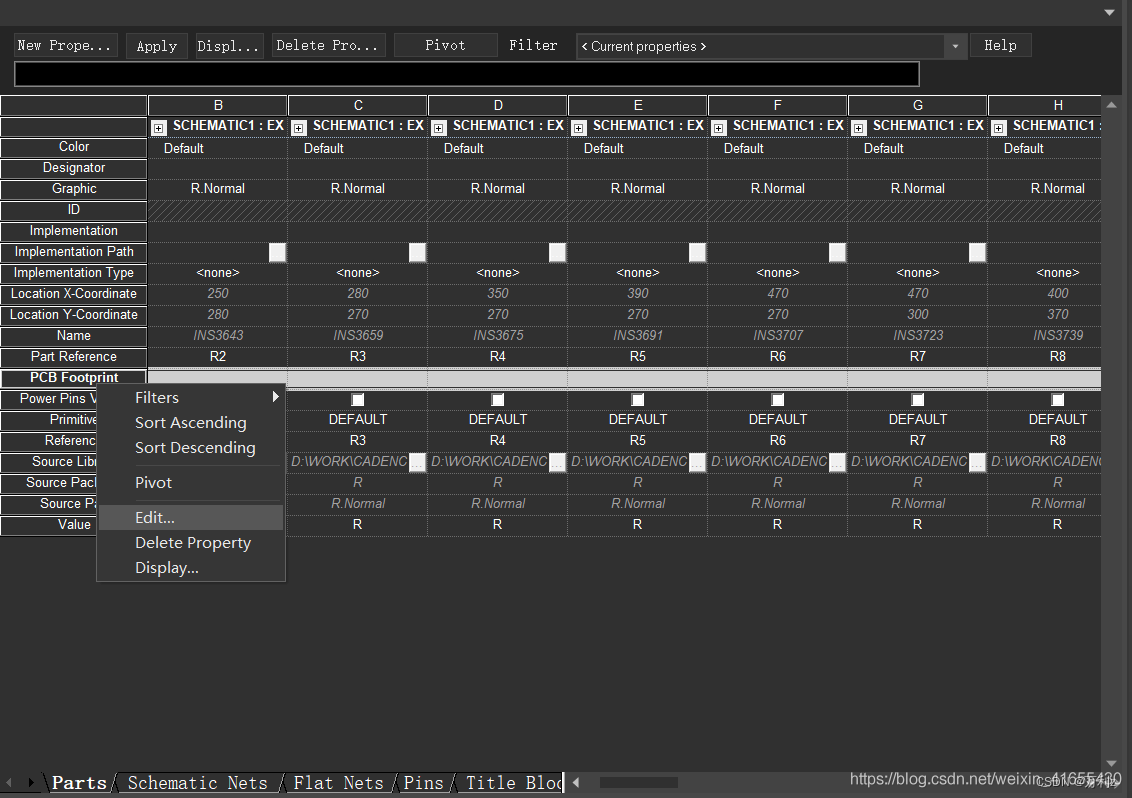

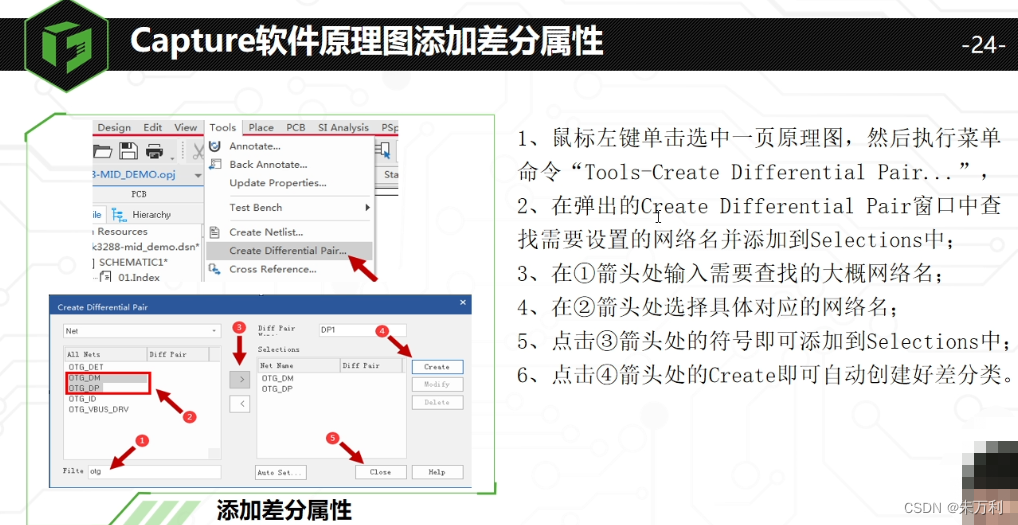

在结束某一操作之后,按F4便可重复之前的操作 6、快速复制之Ctrl在结束某一操作之后,按F4便可重复之前的操作 7、批量浏览点选工程文件 .dsn 工具栏 Edit -> Brower 在Brower中我们可以查看工程中的网络、元件、元件与元件的连接情况 用法: 使用Brower命令寻找未赋值元件 使用Brower命令查找未编号元件 使用Brower命令检查网络连接 使用Brower命令定位DRC标记 8、find命令使用Find快速查找元件 9、Design Cache操作(元件批量替换/更新) 步骤: 打开Cache 选中需要替换的元件 右键Replace cache即可选择替换对象使用场景 需要批量修改某些元件为其他元件 某一元件被重新修改过,增加或减少了一些其他的属性,可以利用Cache批量更新。 chearup cache:清空cache中已不存在于原理图的元件。特殊情况 对应元件对应的封装而言,如果重新修改过元件的封装,那么之后如果仅仅选择更新元件信息,是无法更新元件的封装的,必须使用替换元件才能实现更新引脚信息。 10、元件操作 a、元件移动不带导线的移动:按住ALT键,点按待移动元件然后将其移动,即可去除导线连接进行移动 带导线的移动:直接点按元件即可移动,此时元件所连接的导线也会一起移动。 b、元件旋转快捷键R c、元件镜像:水平镜像 快捷键 H (horizontal) 垂直镜像 快捷键 V (Vertical) d、元件属性浏览框选对应的元件然后右键,快捷菜单中选择Edit Property,即可浏览/修改元件属性 相关菜单注明如下: 框选需要修改的元件,然后会出现所框选所有元件的属性值表,在属性值表中选中 PCB footprint,然后右键Edit,即可修改 1. 添加文本: 放置文本(Place text) (快捷键: T) 2. 添加的文本换行:在输入窗口按 Ctrl+Enter 13、原理图注释操作(annotate):原理图编号(位号)操作请见下图 像平常一样的设计 层叠式结构设计方式cadence SPB17.4 - orcad - 层次原理图 链接: link 15、原理图中添加差分属性

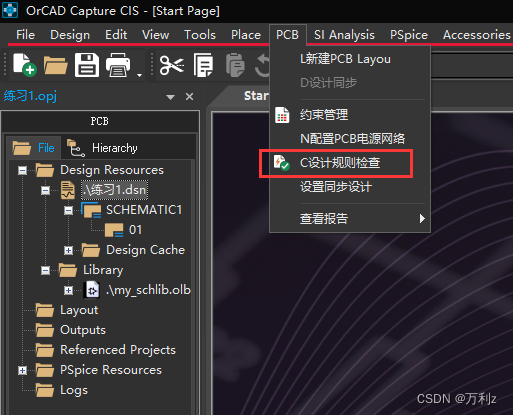

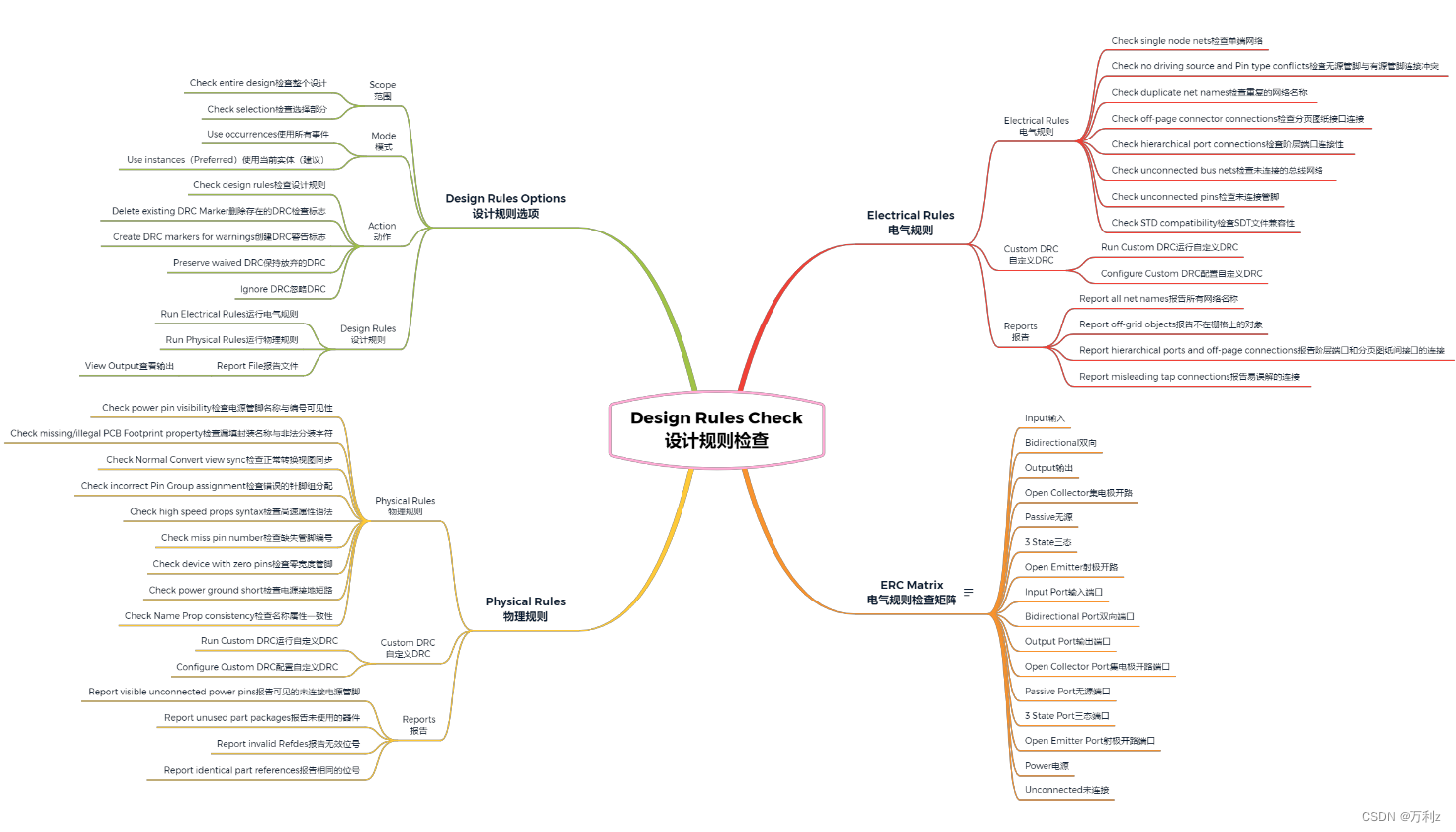

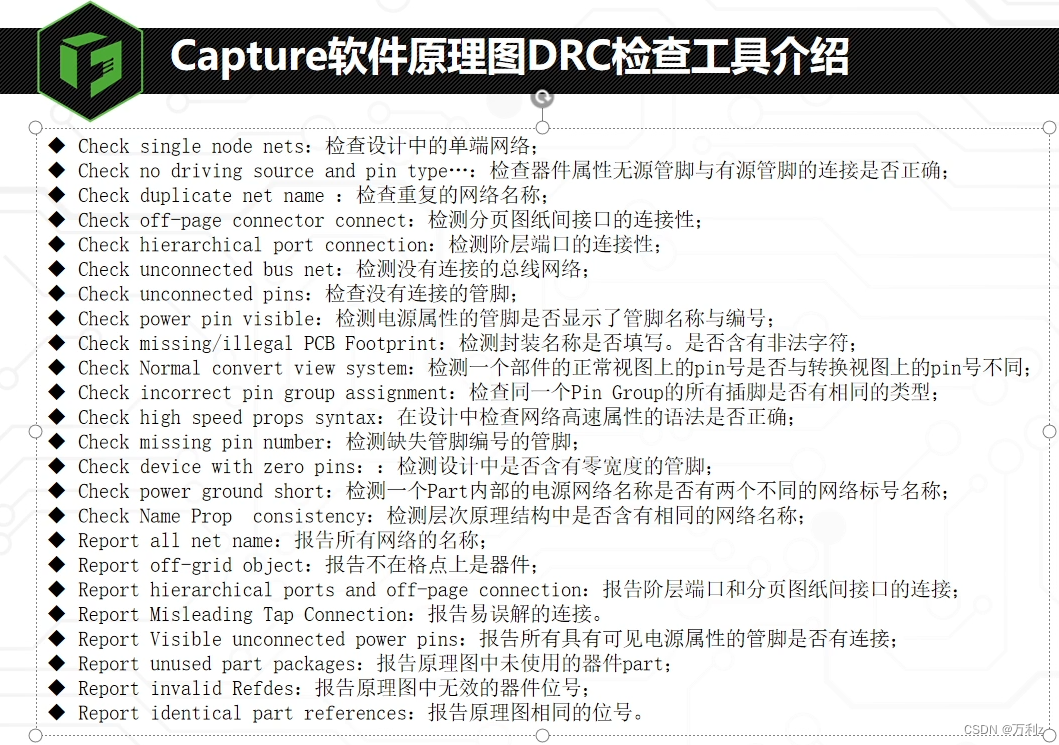

规则部分:一般而言按照图中设置即可 1. 电气规则 check single node nets——检查单节点网络; check unconnected bus net——检查未连接的总线网络; check no driving source and Pin type connect——检查驱动接收等Pin Type的特性,这些在高速仿真时用到; check unconnected pins——检查未连接的管脚; check duplicate net names——检查重复的网络名称; check SDT compatibility——检查SDT兼容性; check off-page connector connect——检查跨页连接的正确性; check hierarchical port connect——检查层次图的连接性; 2. 物理规则 check power pin visible——检查电源引脚可视性 check missing pin number——检查是否有丢失的Pin numbers check missing/illegal PCB footprint property——检查缺失或者不符合规则的PCB封装库定义。没有此项规则导入原理图导入PCB时可能会出项许多问题。 Check Normal Convert view sync ——检查不同视图下的Pin numbers的一致性。 Check power ground short——检查电源、地短接。 Check incorrect Pin_Group assignment——检查Pin_Group属性的正确性; Check Name Prop consisrency——检查名称属性的一致性;(猜的,Prop=Property) Check high speed props syntax——检查高速props语法有无错误; Custom DRC——自定义的DRC;

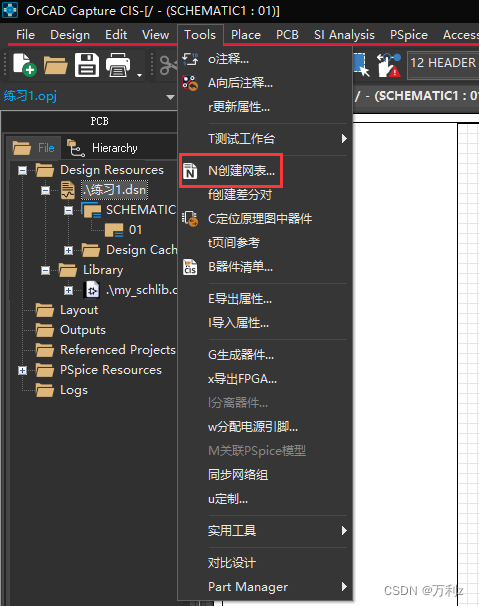

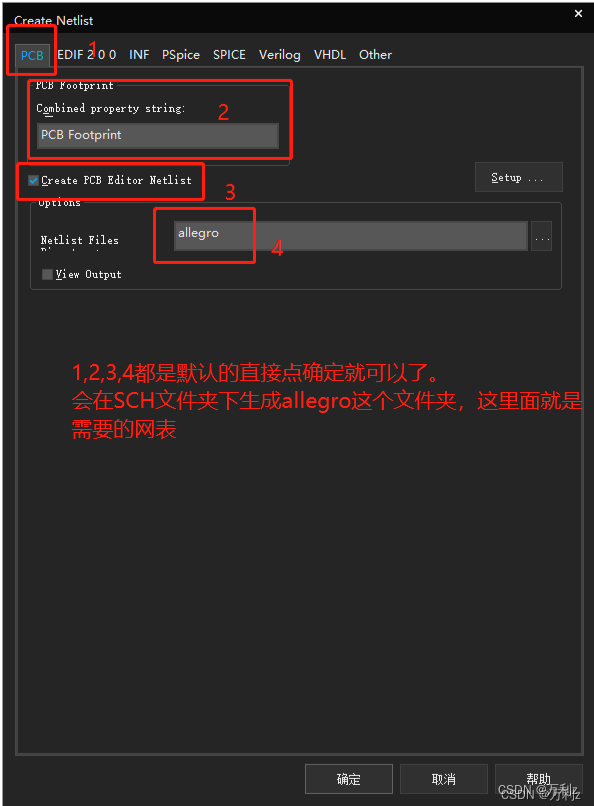

第一方网表是给Allegro使用的。 第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面 第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面

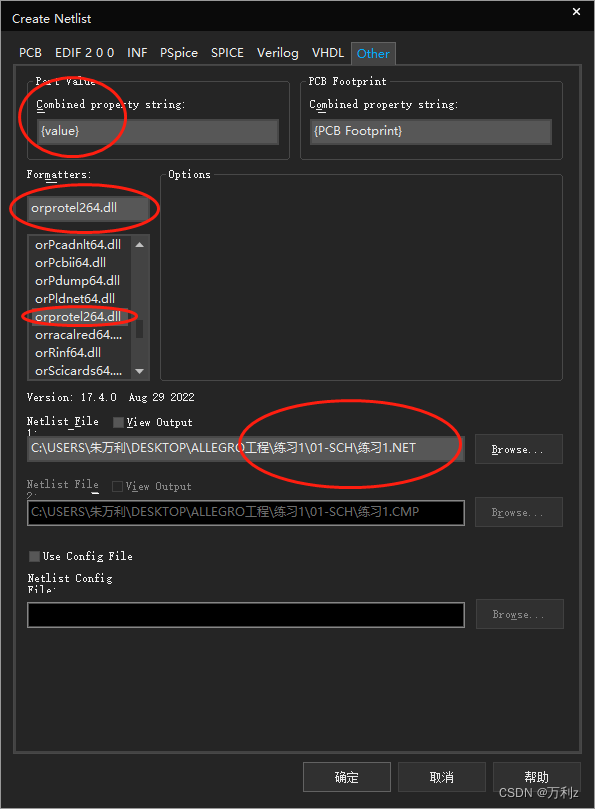

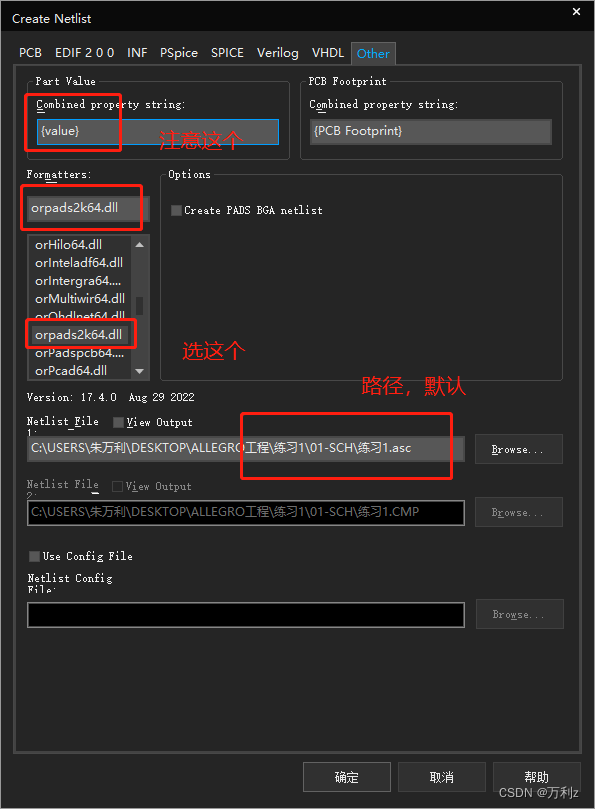

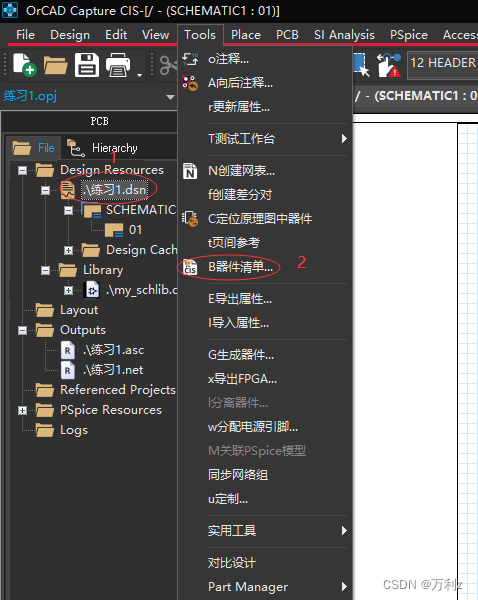

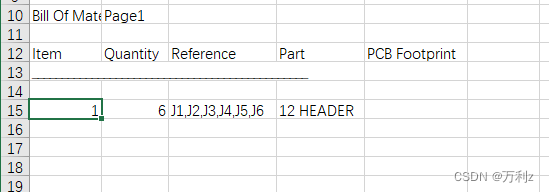

Allegro的第一方网表与第三方网表有以下几个区别点; Ø 与Allegro实现交互式操作的是第一方网表,第三方网表时不可以实现交互式操作; Ø 第三方网表不能将器件的Value属性导入到PCB中,输出时以封装属性来代替Value属性,第一方网表是可以的; Ø 网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生Device文件,才可以将网表导入到PCB中,第一方网表则可以直接导入。 五、原理图导出BOM选中工程文件 .dsn,然后工具栏Tools->CIS Bill of Materials

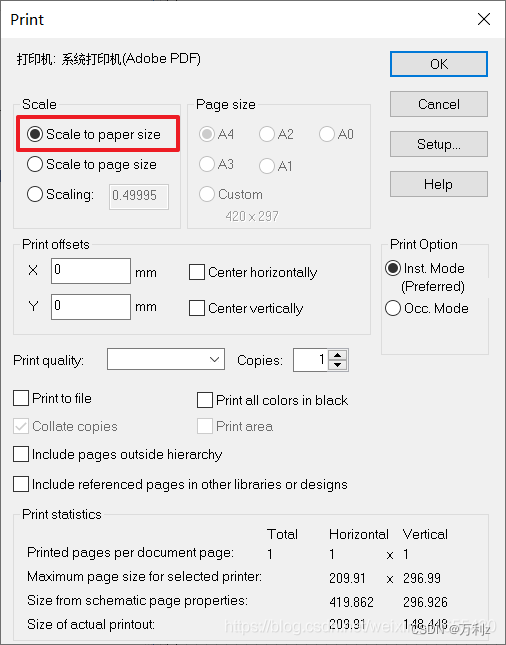

Ctrl +P 快捷键 参数默认即可

在原理图绘制的过程中,灵活使用各种快捷键是提高效率的关键,同时也要注意原理图注释的使用,注释往往能帮助解决一些电路上的小问题。 在使用过程中,发现需要的知识,在继续补充… 明天开始开PCB封装的制作,和焊盘的制作》》》》》 2023-02-09 |

【本文地址】

今日新闻 |

推荐新闻 |

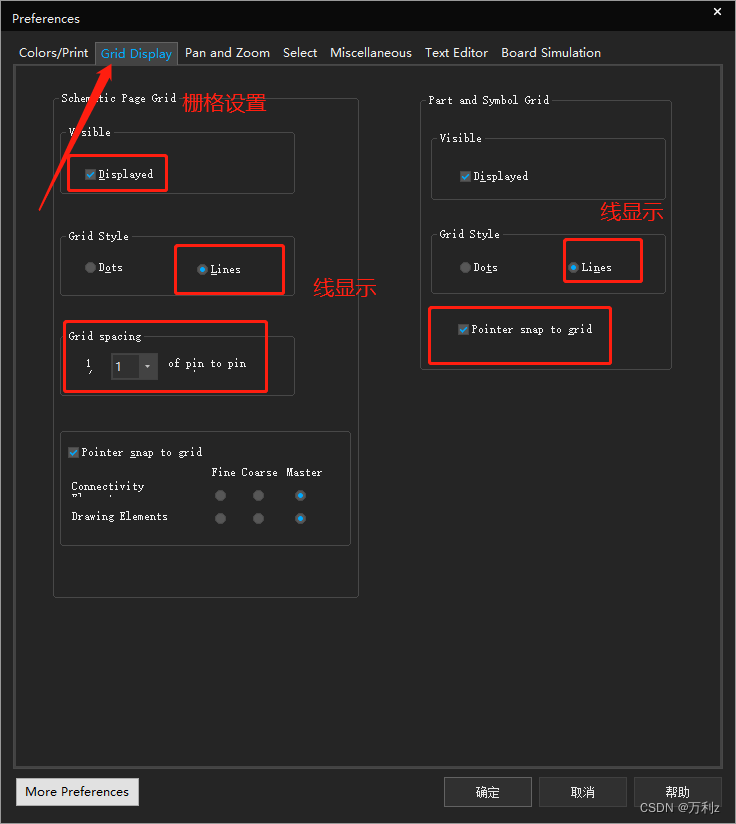

栅格设置,方便绘制原理图。

栅格设置,方便绘制原理图。

点击 pivot后 显示为

点击 pivot后 显示为

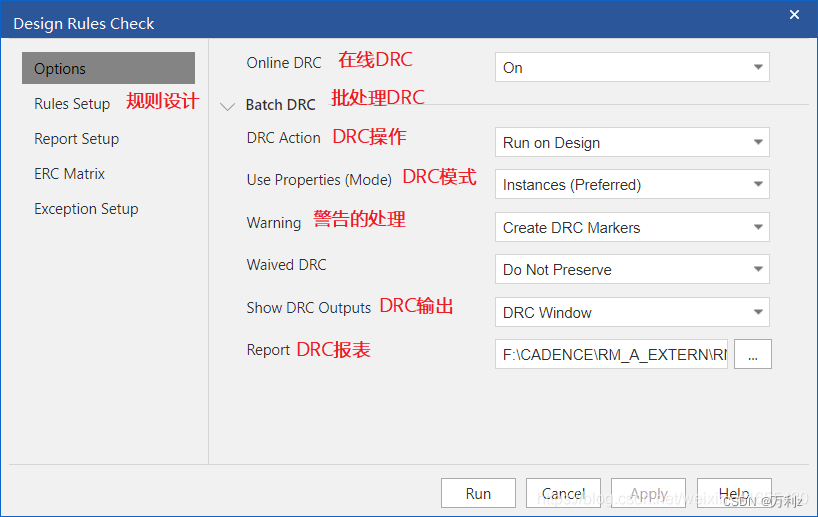

Online DRC :在线DRC DRC Action:DRC操作 定义在何处运行DRC,或者删除DRC标记 Use Properties(mode):DRC模式,事件或者实例,默认为实例 Waring:出现警告时如何处理 Waived DRC:已放弃的DRC如何处理 Show DRC Outputs:DRC的结果输出在何处 Report:DRC报表输出位置

Online DRC :在线DRC DRC Action:DRC操作 定义在何处运行DRC,或者删除DRC标记 Use Properties(mode):DRC模式,事件或者实例,默认为实例 Waring:出现警告时如何处理 Waived DRC:已放弃的DRC如何处理 Show DRC Outputs:DRC的结果输出在何处 Report:DRC报表输出位置

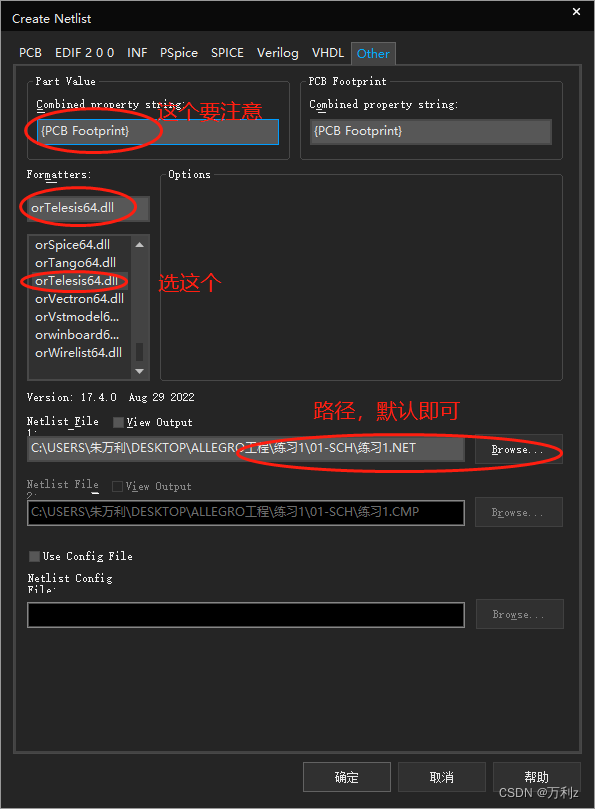

第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图所示, 在Formatters栏中选择orTelesis64.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图所示, 在Formatters栏中选择orTelesis64.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

打开BOM后,另存为即可

打开BOM后,另存为即可

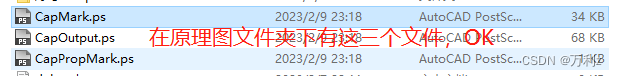

然后使用专业的工具打开,Output.ps这个文件夹就可以了

然后使用专业的工具打开,Output.ps这个文件夹就可以了