CD4042引脚功能 |

您所在的位置:网站首页 › ac208p芯片引脚图 › CD4042引脚功能 |

CD4042引脚功能

|

CD4042四路“D型锁存器”芯片由P和N沟道增强型晶体管组成,它由四个具有公共时钟输入的锁存器、四个缓冲输入和输出引脚组成。它基于CMOS逻辑,具有低功耗和宽电压供应范围的优点。 CD4042器件具有四个数据输入引脚,每个引脚具有两个输出反相和同相输出。根据时钟和极性输入,数据输入引脚上存在的信息将传输到Q和Q'输出。

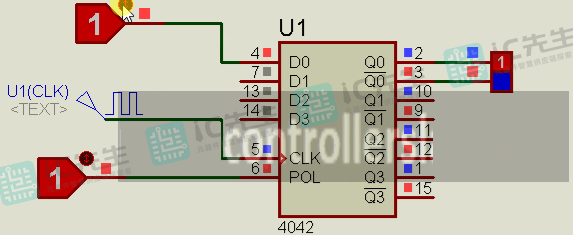

CD4042在单个芯片内有四个D锁存器。每个D锁存器都有一个输入和两个输出引脚,例如Dx、Qx、~Qx。这里的x表示锁存器的编号。然而,所有D锁存器都有共同的极性和时钟信号,其引脚配置图如下所示:

如上图所示,CD4042共有十四个管脚,下表列出了所有引脚及其名称和说明: PIN 引脚名称 功能描述 4, 7, 13, 14 D1、D2、D3、D4 四个数据输入 1, 2, 10, 11 Q1, Q2, Q3, Q4 四个锁存器的并行输出 3, 9, 12, 15 ~Q1, ~Q2, ~Q3, ~Q4 四个锁存器的反向并行输出 5 CLOCK 通过555定时器或任何其他数字逻辑IC提供的时钟脉冲信号 6 POLARITY 控制输出的上升和下降时间。当POLARITY为低电平时,数据传输到0 CLOCK电平输出,反之亦然。 8 Vss 电路的接地 16 Vdd 正电源 功能特点 由四个具有公共时钟输入、正常和反相输出的触发器组成。 低功耗TTL兼容。 时钟和极性输入都控制输出。 指定静态电流高达20V。 电源电压范围:3V至20V。 工作温度范围:-55°C至125°C。 建立时间:25至50ns(根据电压而变化)。 标准对称输出。等效和替代型号4508(双4位锁存器)、4099(8位可寻址锁存器)、CD4027(双JK触发器IC)、74LS279、74LS373。 工作原理CD4042内部的每个Latch由1个数据输入引脚和两个输出Q和~Q组成。两个输出值的变化取决于时钟电平。除了这些输入之外,它还有一个用于对时钟输入进行编程的极性输入。当极性输入为低电平时,数据输入端的信息被传输到Q和0时钟电平期间,当它为高电平时,传输发生在1时钟电平期间。

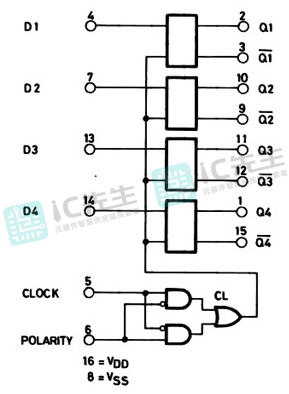

CD4042内部功能图指示并行数据输入、反相和非反相输出如下所示:

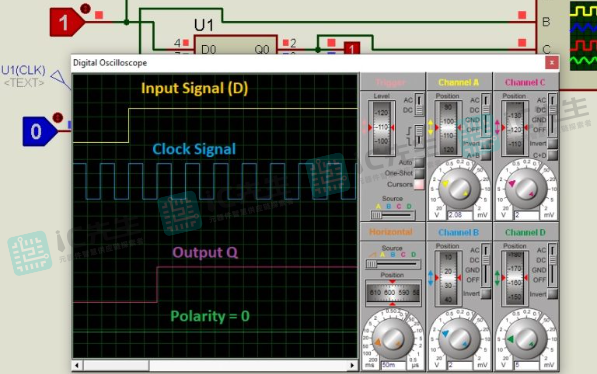

在取决于极性输入的每个时钟转换中,数据被传输到输出,但在相同的时钟电平期间,该值将被保留,直到时钟信号的值发生变化并与前一个相反。当然,这种行为可以通过下面给出的真值表来解释: CLOCK POLARITY NON-INVERTED OUTPUT L 0 D Positive edge 0 Latch H 1 D Negative Edge 1 Latch从上面的真值表可以看出,当极性引脚处于低电平状态时,输出将在时钟信号的正转换时上升。另一方面,当它处于高电平状态时。 另外,从上表也可以看出,CD4042的极性引脚决定了D Latch输出的转换。它决定输出转换将发生在时钟周期的上升沿还是下降沿。如果极性信号=0或逻辑低电平,则它在时钟的上升沿工作,否则在时钟周期的下降沿工作。 应用电路1 从该图中可以看出,当极性等于低电平有效时,输入信号在时钟的上升沿变高,输出出现在时钟周期的下一个上升沿的Q引脚上。

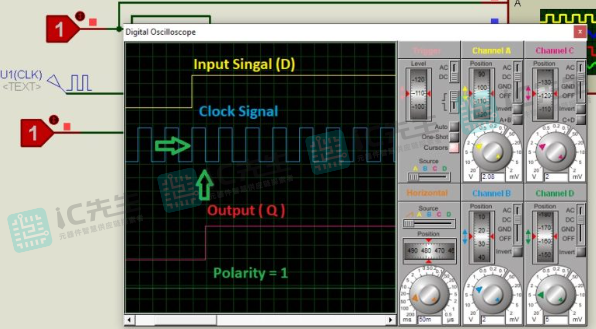

应用电路2 同样,如果极性为高电平有效(1),则输入信号出现在时钟下降沿的输出上。从仿真中可以看出,即使输入信号 (D) 在上升沿可用,但它会在时钟的下一个下降沿反映到输出引脚上。

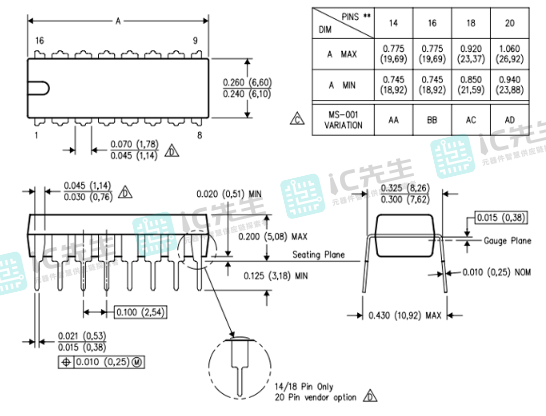

闩锁和触发器基本上是存储元件。CD4042包含四个锁存器,因此该IC可用作保持寄存器或电源开关电路的存储设备。它也可以用作异步系统中的输入或输出端口。一些比较常见的应用包括: 用于数据存储的数字电子产品 弹跳消除开关 计算机使用此芯片进行计算 缓冲存储、数据传输和保持寄存器 用作脉冲锁存器以快速脉冲时钟 通用数字逻辑 由于速度快,用于高电路设计 封装设计参数

CD4042是一种单片集成电路,采用DIP和SOP封装的金属氧化物半导体技术制造。CD4042包含四个锁存电路,每个锁存电路由一个公共时钟选通。每个电路都有互补的缓冲输出。N和P通道输出设备的阻抗是平衡的,所有输出在电气上都是相同的。 在POLARITY输入编程的CLOCK电平期间,数据输入处的信息被传输到输出Q和Q'。对于POLARITY=0,传输发生在0时钟电平期间,而对于POLARITY=1,传输发生于1时钟电平期间。输出跟随数据输入,提供上面定义的CLOCK和POLARITY电平。 当发生CLOCK转换时(POLARITY=0为正,POLARITY=1为负),在CLOCK转换期间出现在输入端的信息被保留在输出端,直到发生相反的CLOCK转换。 |

【本文地址】

今日新闻 |

推荐新闻 |