Microsemi Libero SoC使用教程(胎教级 免费)(创建工程、引脚分配、仿真、逻辑分析仪ILA) |

您所在的位置:网站首页 › a6061h引脚功能使用教程 › Microsemi Libero SoC使用教程(胎教级 免费)(创建工程、引脚分配、仿真、逻辑分析仪ILA) |

Microsemi Libero SoC使用教程(胎教级 免费)(创建工程、引脚分配、仿真、逻辑分析仪ILA)

|

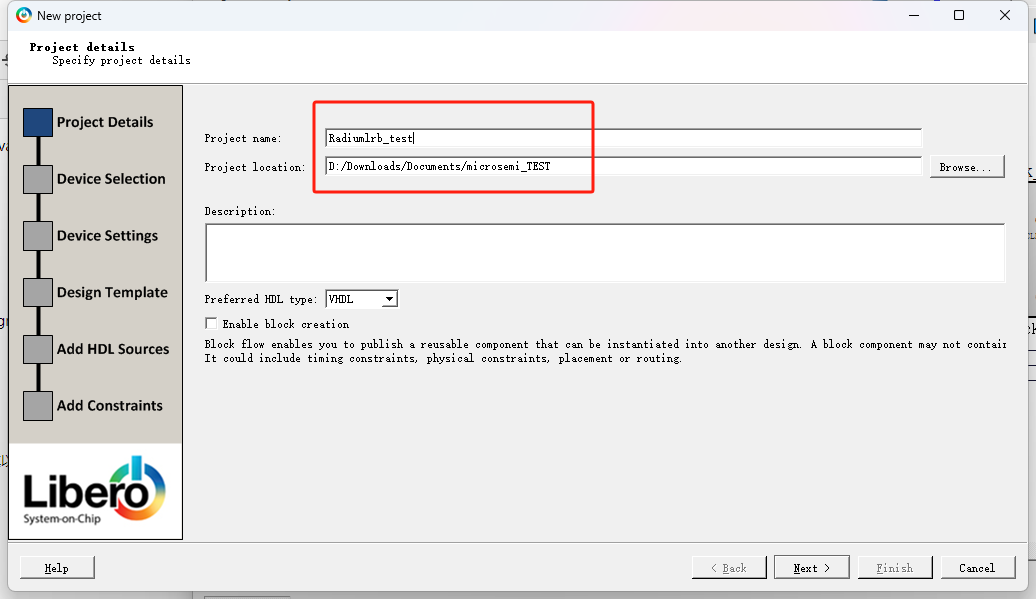

Libero SoC是一款集成了多种功能的FPGA开发软件,可以用来设计、仿真、综合、布局、布线、下载和调试FPGA项目。 1、新建工程首先,我们需要新建一个工程,点击File->New Project,然后给工程取一个名字,选择工程的存放路径,点击Next。

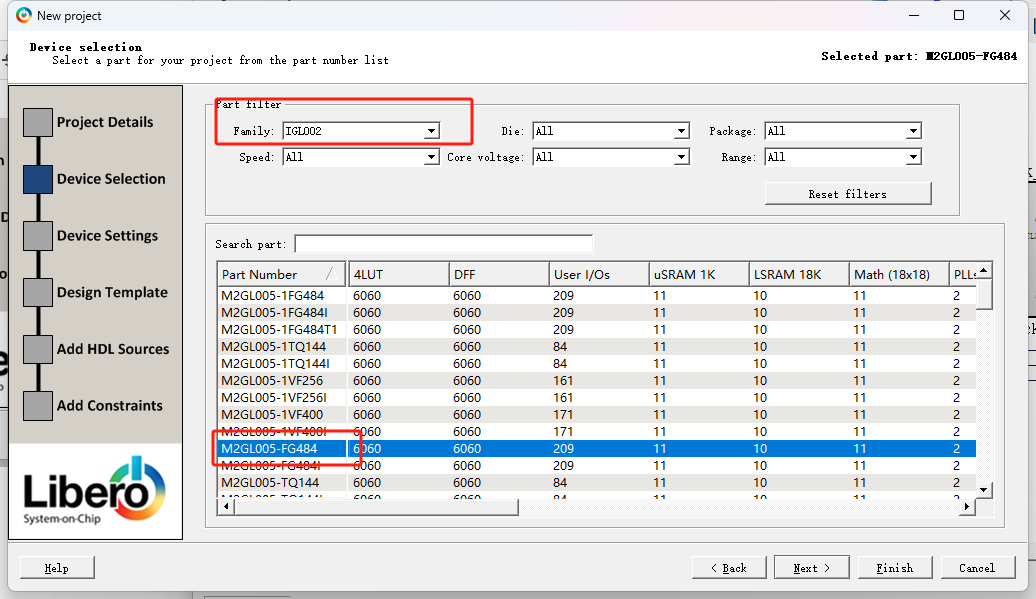

接下来,我们需要选择FPGA的family和芯片型号

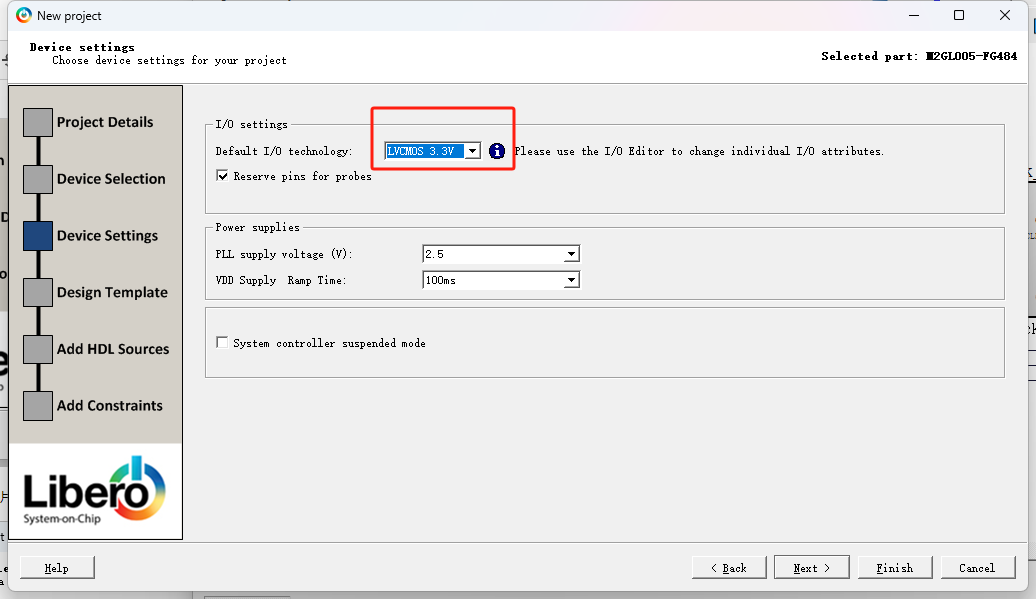

然后,我们需要更改电压,这里我选择了3.3V,点击Next。

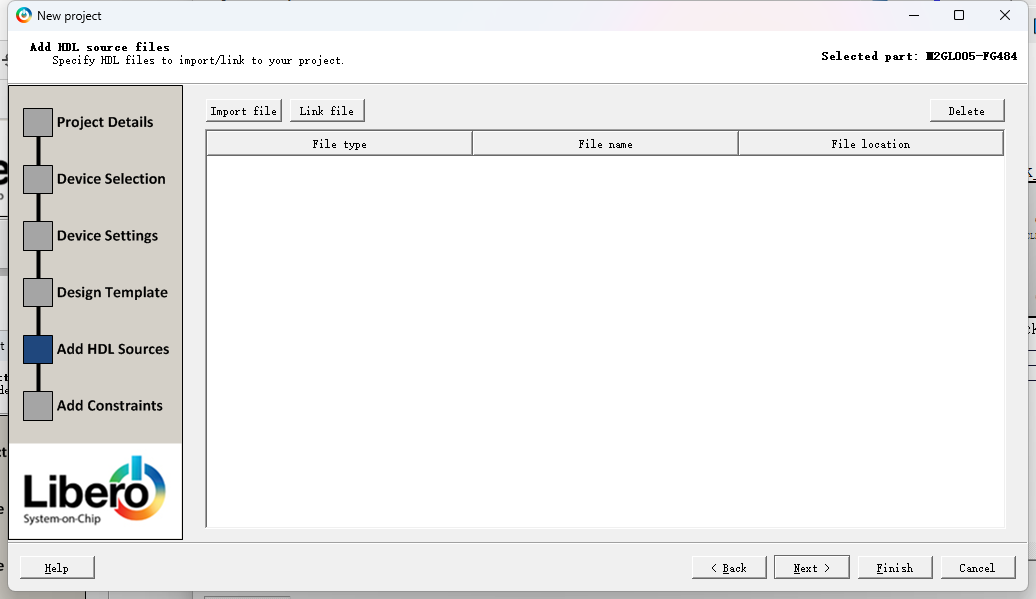

如果我们有已经编写好的HDL文件,可以在这里导入,点击Add Files,选择HDL文件,点击Next。如果没有,可以跳过这一步。

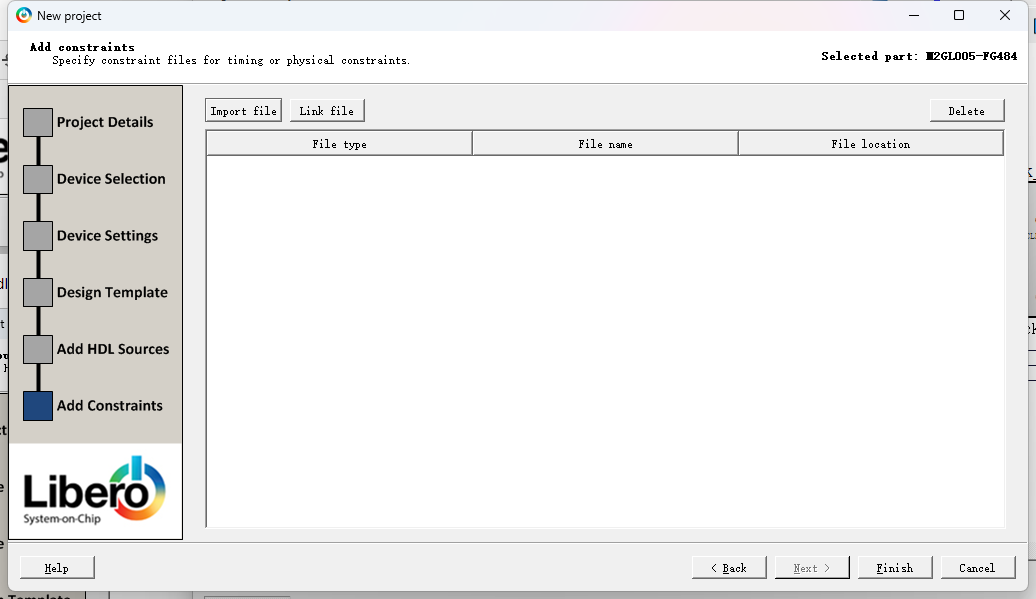

如果有编写好的PDC约束文件,可以在这里导入,点击Add Files,选择PDC文件,点击Next。如果没有,可以跳过这一步。最后,点击Finish,就完成了工程的新建

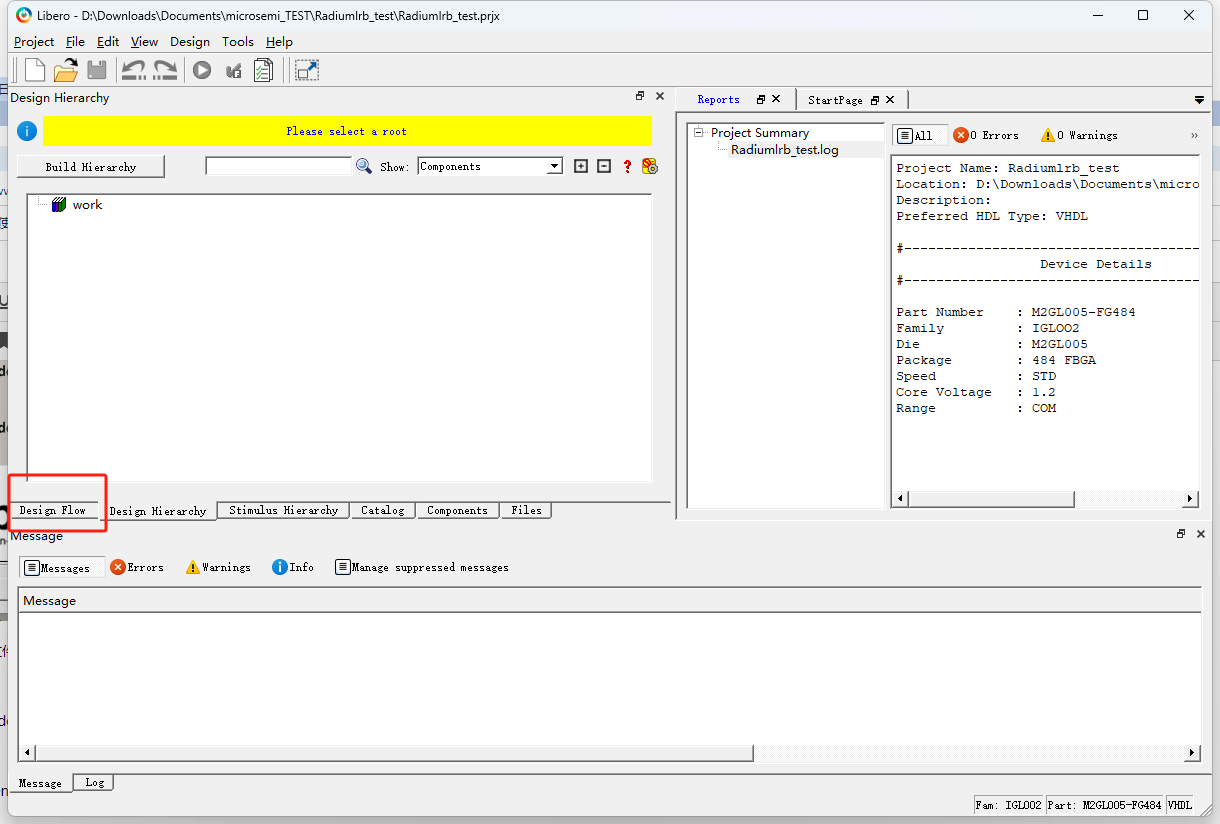

创建工程完成后,我们可以看到如下图的界面,这里我们可以看到Design Flow,这是Libero SoC的核心功能,它可以帮助我们完成从设计到下载的整个流程。

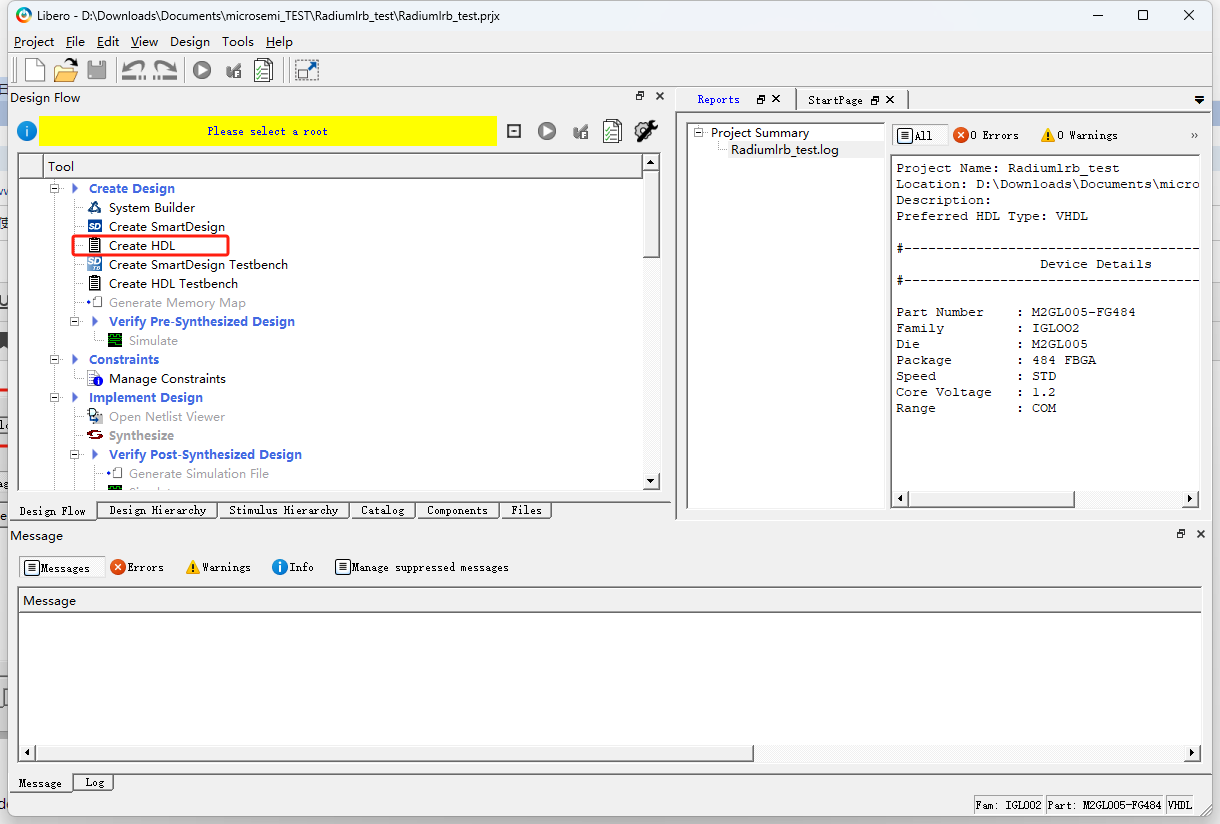

我们先来创建一个HDL文件,点击Design Flow中的Create HDL

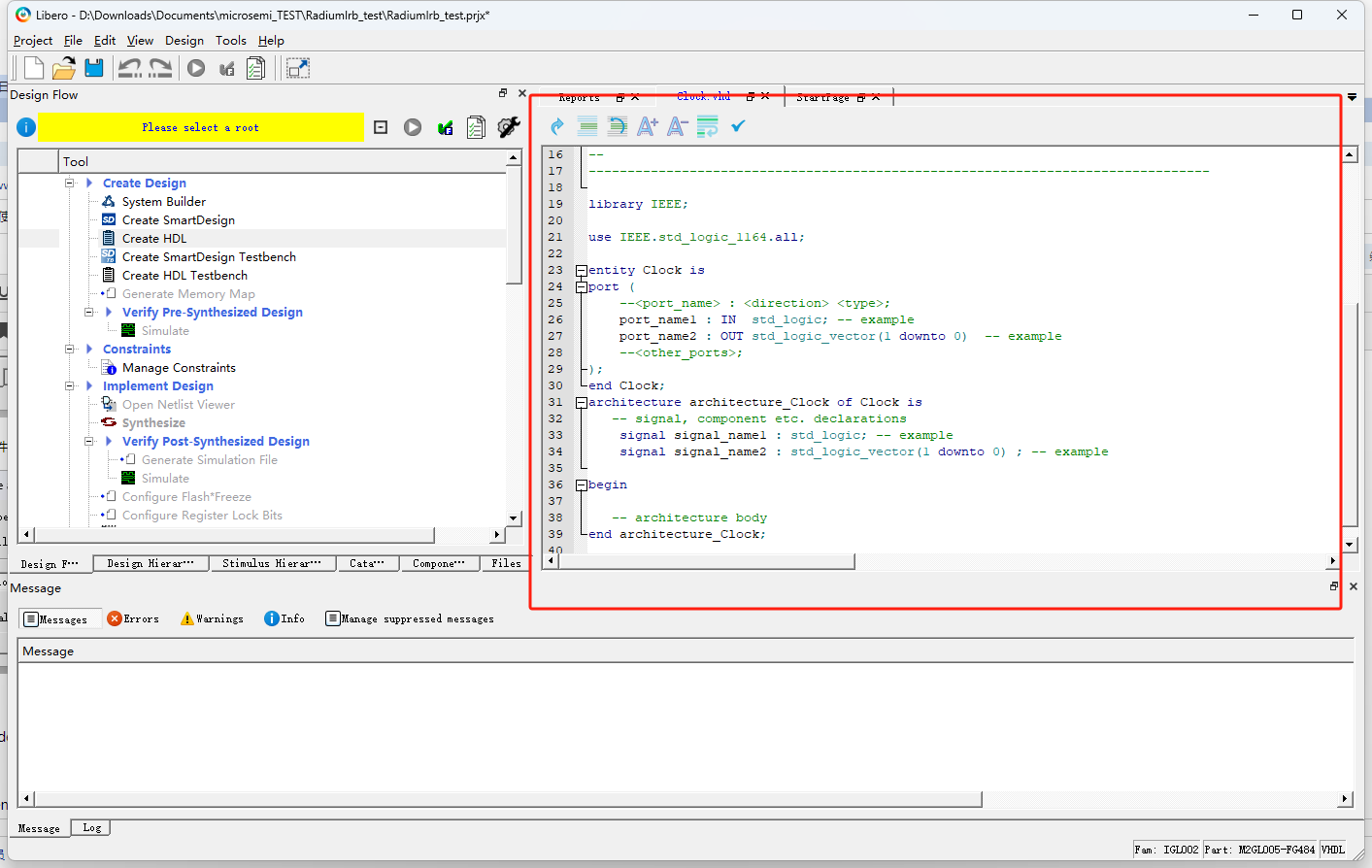

然后给HDL文件取一个名字,然后选择HDL的语言,这里我选择了VHDL,还可以选择是否使用模板创建,使用模板创建文件会给出最基础的代码结构,点击OK。

可以看到,Libero SoC自动为我们生成了一个VHD文件,最基础的代码结构已经给出,包括了模块名、端口定义、参数声明等,我们只需要在这个基础上编写我们的逻辑代码即可。

这里我编写了一个简单的时钟分频器的代码,输入50MHz的时钟,分配输出25MHz和5MHz两种时钟,代码如下: LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE ieee.numeric_std.ALL; ENTITY Clock IS PORT ( -- input CLK : IN STD_LOGIC; -- system clock 50MHz RESET_N : IN STD_LOGIC; -- output CLK_25M : OUT STD_LOGIC; CLK_5M : OUT STD_LOGIC ); END Clock; ARCHITECTURE architecture_Clock OF Clock IS SIGNAL counter_5M : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000"; -- 50MHz/5MHz/2-1 = 4 (in hexadecimal 0x0004) SIGNAL CLK_25Mdiv_s : STD_LOGIC := '0'; -- 25MHz clock signal SIGNAL CLK_5M_s : STD_LOGIC := '0'; -- 5MHz clock signal BEGIN ------------------25MHz clock divider--------------------------- clock_25Mdivider : PROCESS (RESET_N, CLK) BEGIN IF (RESET_N = '0') THEN CLK_25Mdiv_s |

【本文地址】

今日新闻 |

推荐新闻 |