逻辑电平(TTL/CMOS/LVDS/LVPECL/CML) |

您所在的位置:网站首页 › TTL信号电压幅值 › 逻辑电平(TTL/CMOS/LVDS/LVPECL/CML) |

逻辑电平(TTL/CMOS/LVDS/LVPECL/CML)

|

低速逻辑电平

TTL/CMOS/LVTTL/LVCMOS逻辑电平介绍

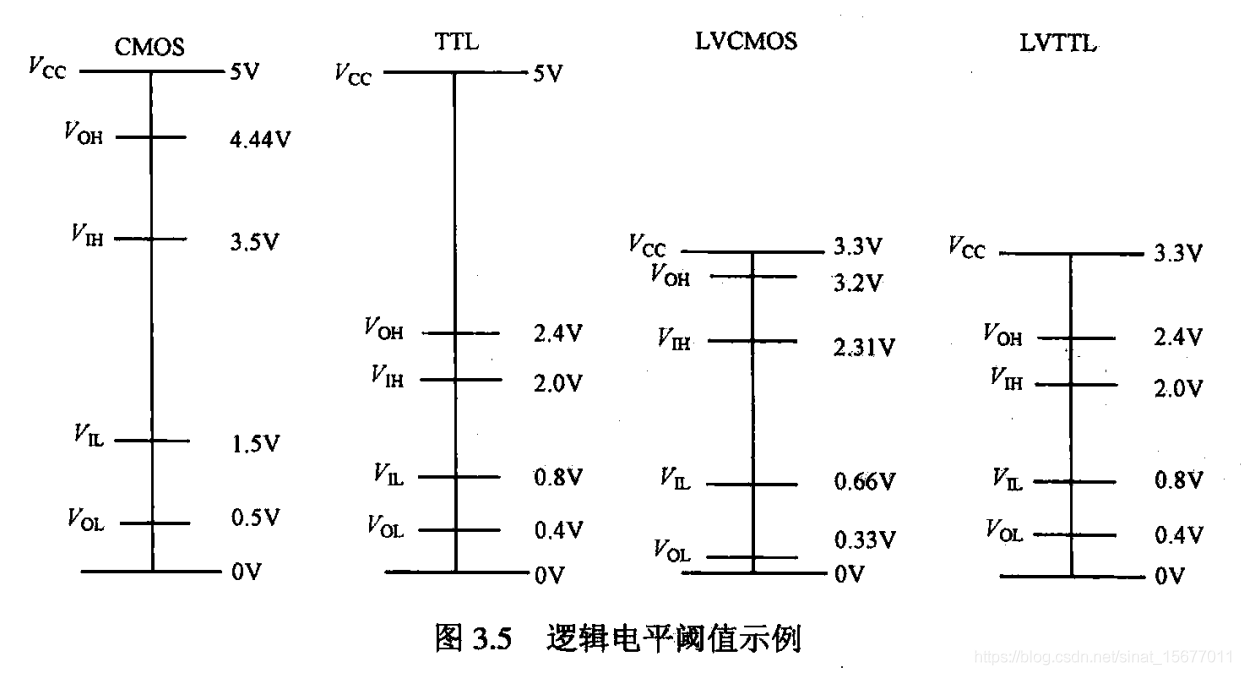

传统单板设计中,TTL和CMOS逻辑电平被广泛应用,是数字电路设计中最常见的两种逻辑电平,LVTTL和LVCMOS是它们的低电平版本。 TTL----------(Transistor-Transistor Logic gate),晶体管-晶体管逻辑门 由于晶体管是流控器件,且输入电阻较小,因此TTL电平速度快,但功耗较大; CMOS------(Complementary Metal Oxide Semiconductor),翻译过来是互补金属氧化物半导体 ,也就是MOS管逻辑。 由于MOS管是压控器件,且输入电阻极大,因此CMOS电平的器件速度较慢,但功耗较小,同时由于CMOS器件输入阻抗很大,外界微小的干扰就可能引起电平的翻转,因此CMOS器件上使用的输入引脚应做上下拉处理,不能浮空。 现实中的信号是连续的模拟信号,而数字信号只有“1”和“0”两种逻辑状态,需使用阈值来定义来定义信号的逻辑状态。 逻辑电平阈值如下图: |

【本文地址】

今日新闻 |

推荐新闻 |

(注意:上图只是一个示意图ÿ

(注意:上图只是一个示意图ÿ