FPGA纯verilog实现视频拼接,纯逻辑资源搭建,提供4套工程源码和技术支持 |

您所在的位置:网站首页 › 960x540分辨率 › FPGA纯verilog实现视频拼接,纯逻辑资源搭建,提供4套工程源码和技术支持 |

FPGA纯verilog实现视频拼接,纯逻辑资源搭建,提供4套工程源码和技术支持

|

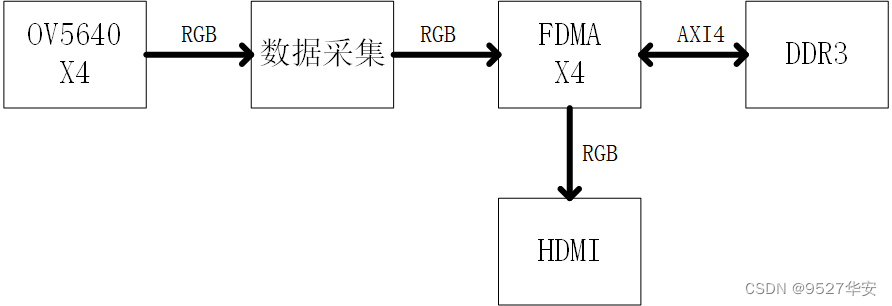

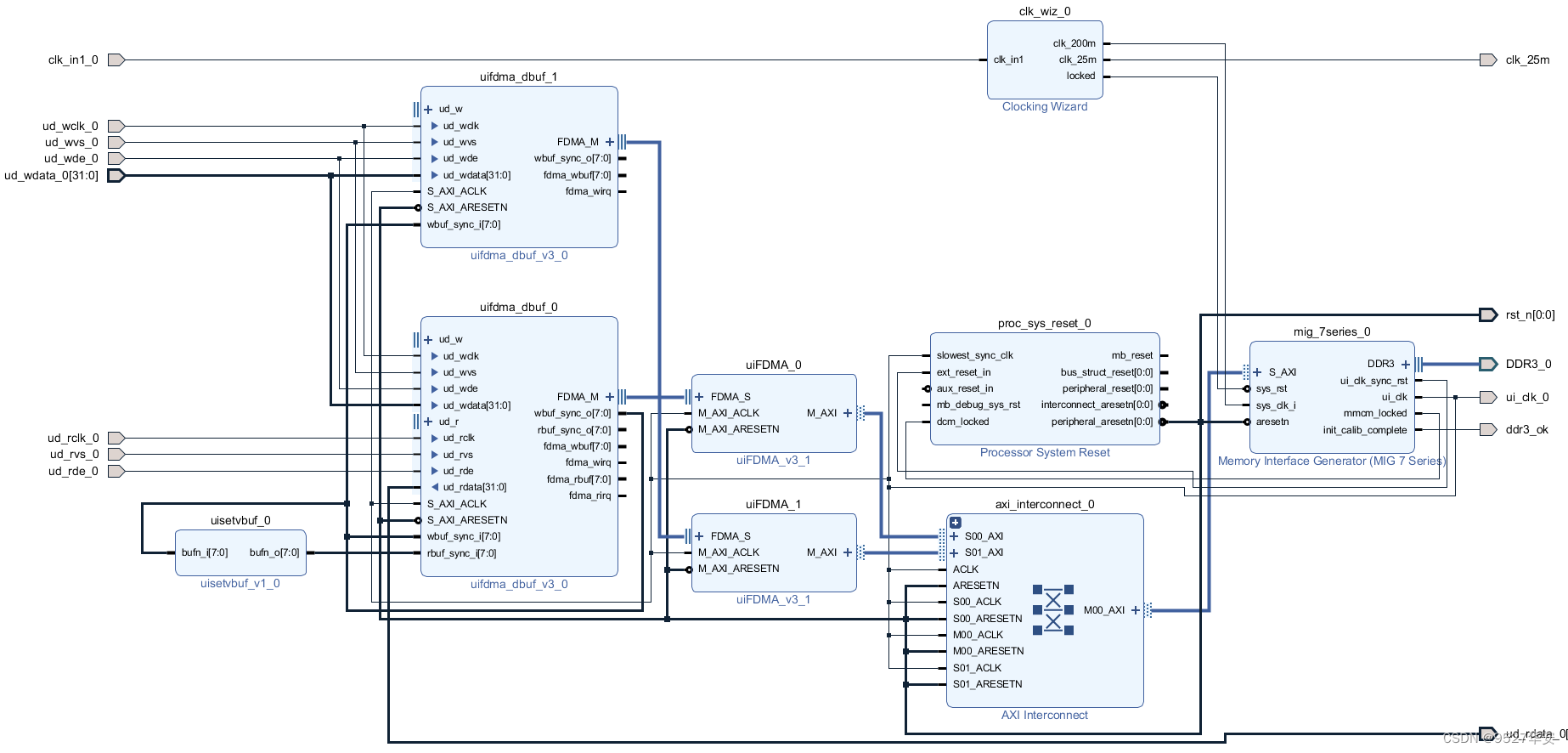

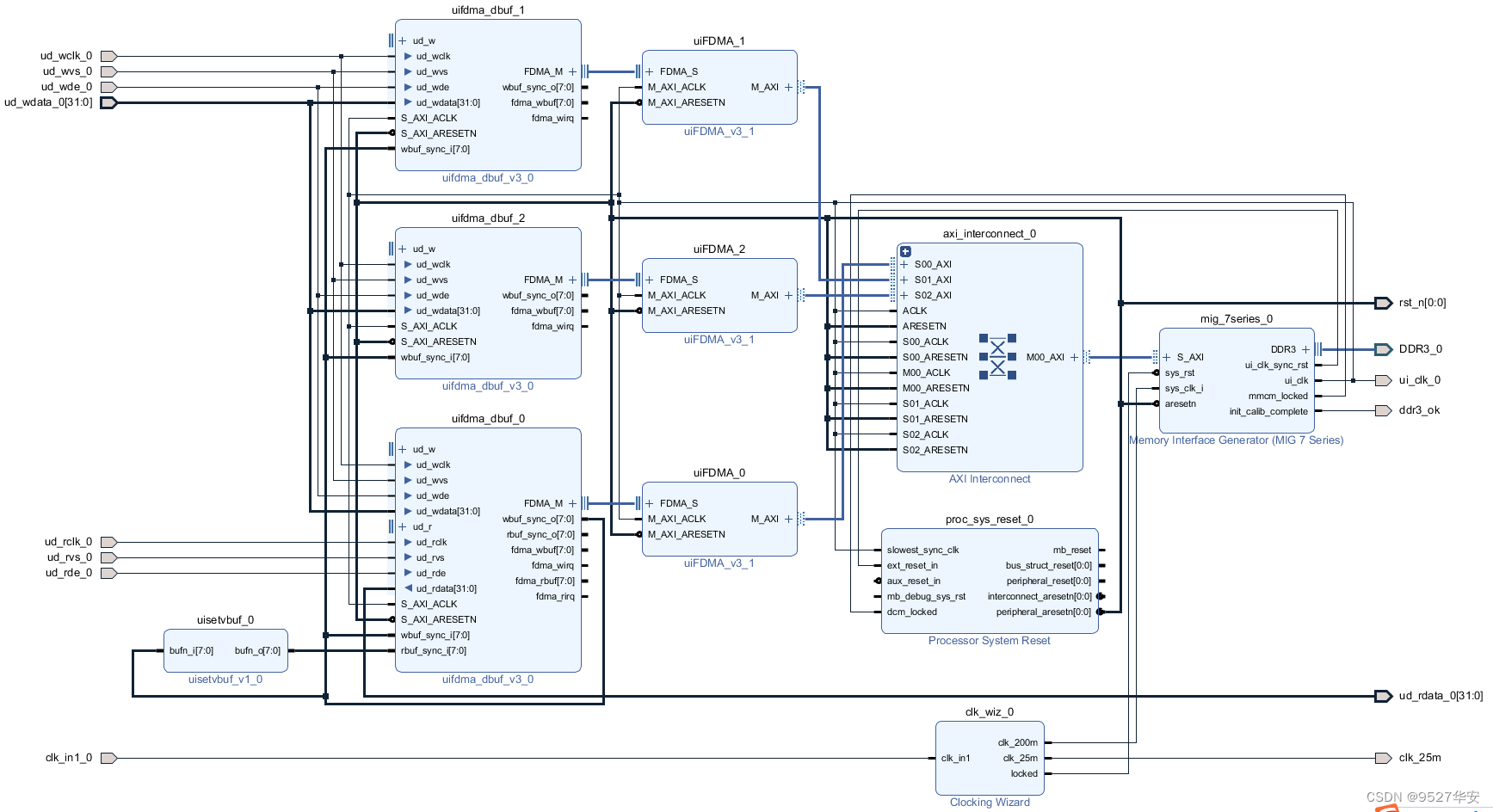

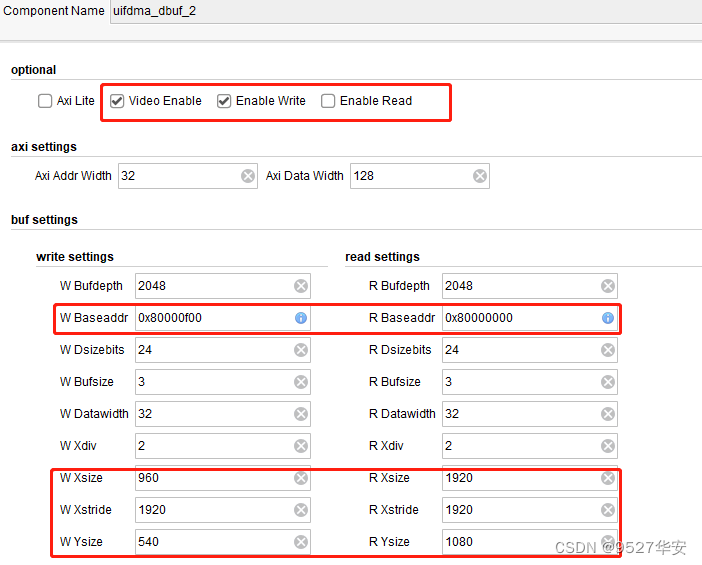

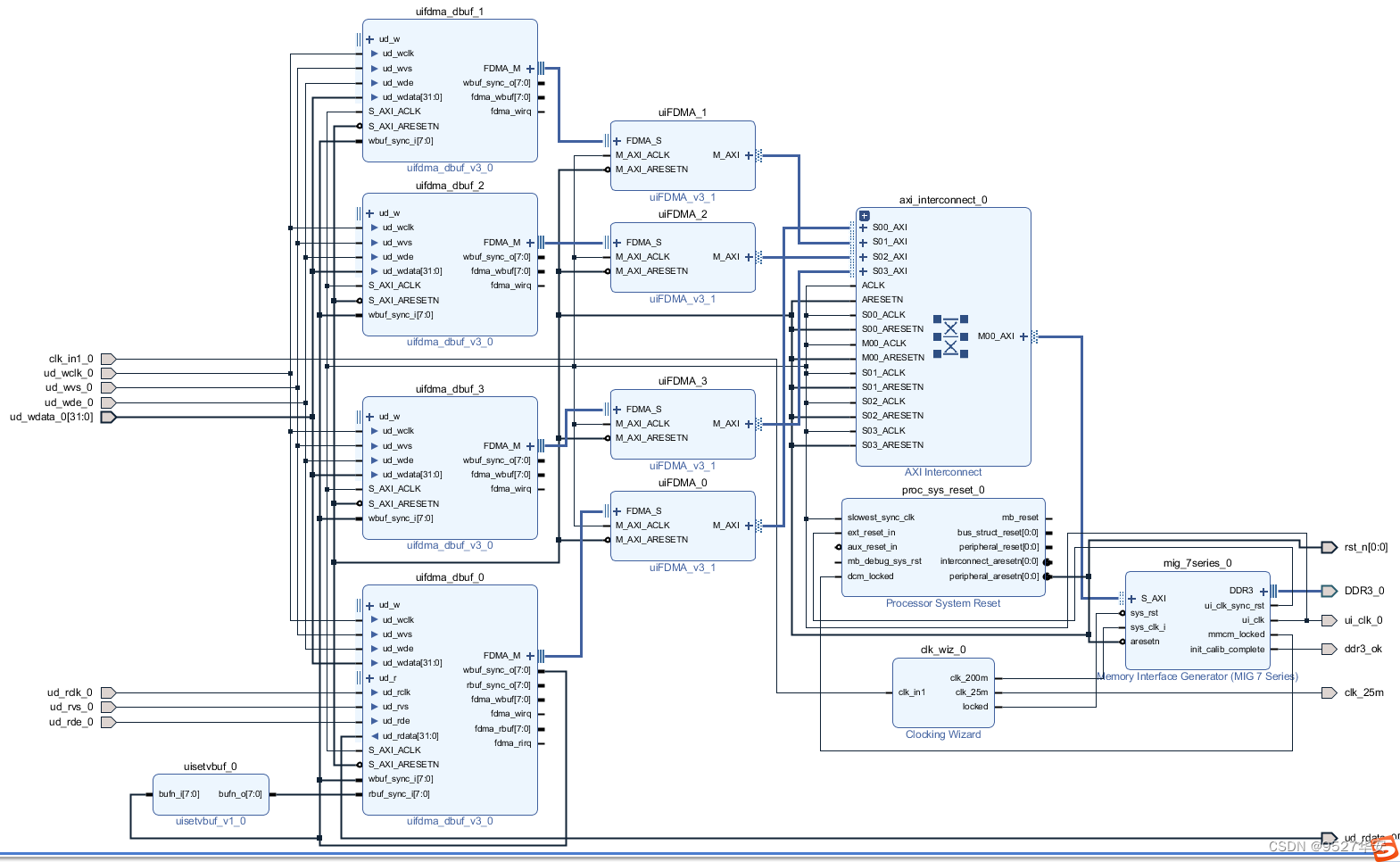

FPGA纯verilog实现视频拼接,纯逻辑资源搭建,提供4套工程源码和技术支持 1.本方案的实用价值FPGA实现视频拼接是FPGA在图像处理领域的基本应用,如果你的视频是AXIS流,且你的开发板是K7或者zynq之类的高端处理器,可以使用Xilinx官方的video mixer实现视频拼接,关于video mixer实现视频拼接,可以参考我之前写的文章点击查看:video mixer实现视频拼接但是,对于使用A7或者Spartan6之类的低端FPGA开发者来说,video mixer就不适用了,再者,video mixer必须是AXIS接口,对于vga时序或者摄像头rgb时序而言也不适用,必须用Xilinx的ip转为AXIS流,如此不仅麻烦且加大了逻辑资源消耗,这时,本文的视频拼接方案就有用了。 2.总体设计方案设计方案如下:以4路OV5640摄像头拼接为例; OV5640:4路摄像头输入,摄入分辨率设置为960X540;数据采集:将OV5640摄像头数据采集输出;FDMA:实现视频数据的三帧缓存,读写进出DDR3,关于FDMA,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存HDMI:输出显示,1080P分辨率; 3.视频拼接方案算法视频拼接方案如下:以4路OV5640摄像头拼接为例; 开发板:Kintex7开发板;开发环境:vivado2019.1;输入:1路OV5640摄像头;1280X720分辨率;输出:HDMI,1920X1080分辨率;工程BD部分如下: 开发板:Kintex7开发板;开发环境:vivado2019.1;输入:2路OV5640摄像头;960X540分辨率;输出:HDMI,1920X1080分辨率;工程BD部分如下: 开发板:Kintex7开发板;开发环境:vivado2019.1;输入:3路OV5640摄像头;960X540分辨率;输出:HDMI,1920X1080分辨率;工程BD部分如下: 开发板:Kintex7开发板;开发环境:vivado2019.1;输入:4路OV5640摄像头;960X540分辨率;输出:HDMI,1920X1080分辨率;工程BD部分如下: 开发板连接: 福利:工程代码的获取代码太大,无法邮箱发送,以百度网盘链接方式发送,通过微信获取资料: |

【本文地址】

今日新闻 |

推荐新闻 |

输出屏幕分辨率为1920X1080;输入摄像头分辨率为960X540;4路输入刚好可以占满整个屏幕;多路视频的拼接显示原理如下:

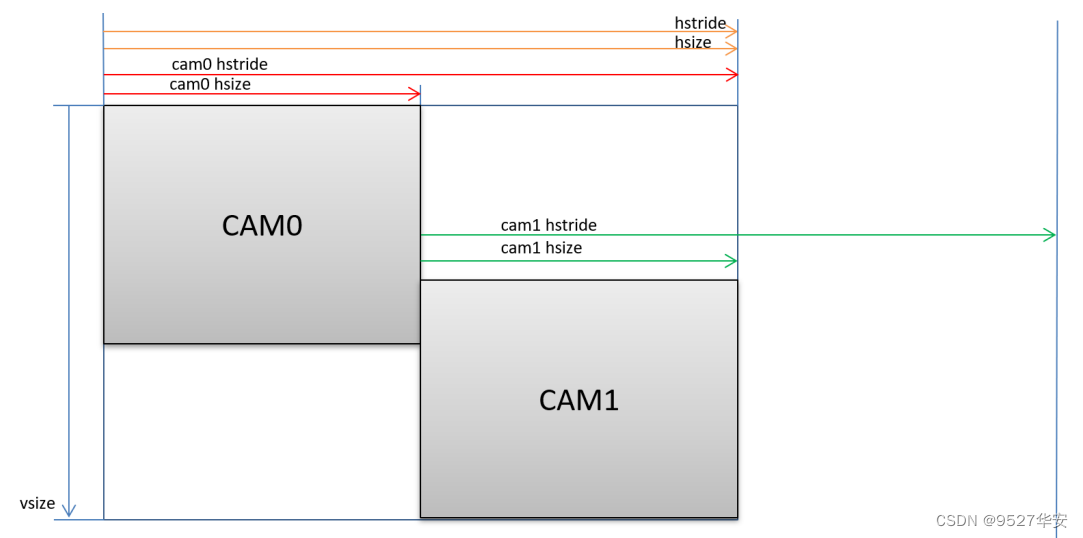

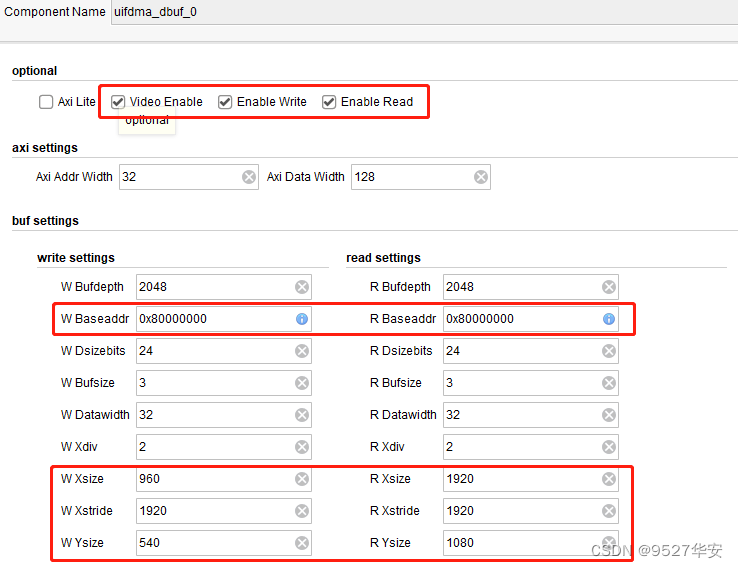

输出屏幕分辨率为1920X1080;输入摄像头分辨率为960X540;4路输入刚好可以占满整个屏幕;多路视频的拼接显示原理如下: 以把 2 个摄像头 CAM0 和 CAM1 输出到同一个显示器上为列,为了把 2 个图像显示到 1 个显示器,首先得搞清楚以下关系:hsize:每 1 行图像实际在内存中占用的有效空间,以 32bit 表示一个像素的时候占用内存大小为 hsize*4;hstride:用于设置每行图像第一个像素的地址,以 32bit 表示一个像素的时候 v_cnt hstride4;vsize:有效的行;因此很容易得出 cam0 的每行第一个像素的地址也是 v_cnt hstride4;同理如果我们需要把 cam1 在 hsize 和 vsize 空间的任何位置显示,我们只要关心 cam1 每一行图像第一个像素的地址,可以用以下公式 v_cnt hstride4+offset;uifdma_dbuf 支持 stride 参数设置,stride 参数可以设置输入数据 X(hsize)方向每一行数据的第一个像素到下一个起始像素的间隔地址,利用 stride 参数可以非常方便地摆放输入视频到内存中的排列方式。关于uifdma_dbuf,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存根据以上铺垫,每路摄像头缓存的基地址如下:CAM0:ADDR_BASE=0x80000000;CAM1:ADDR_BASE=0x80000000+(1920-960)X4;CAM2:ADDR_BASE=0x80000000+(1080-540)X1920X4;CAM3:ADDR_BASE=0x80000000+(1080-540)X1920X4+(1920-960)X4;地址设置完毕后基本就完事儿了;

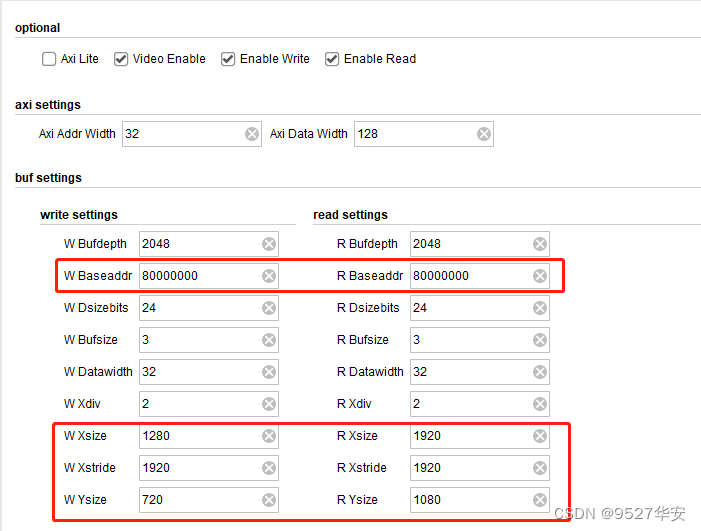

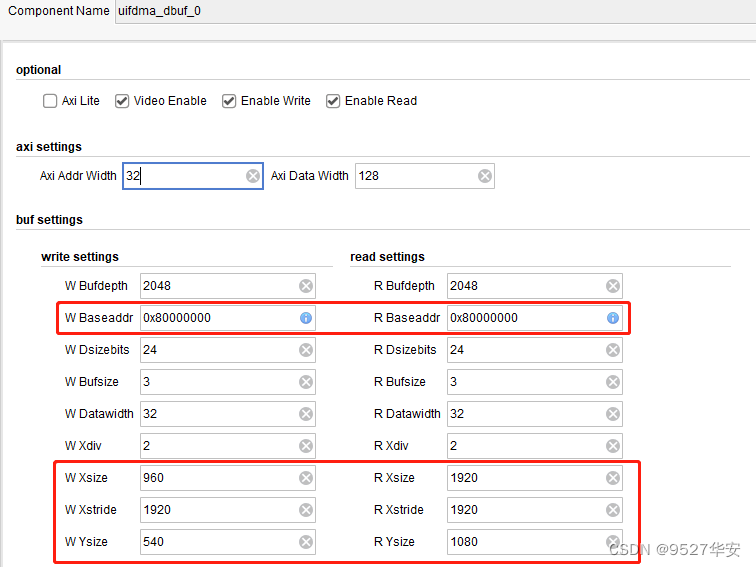

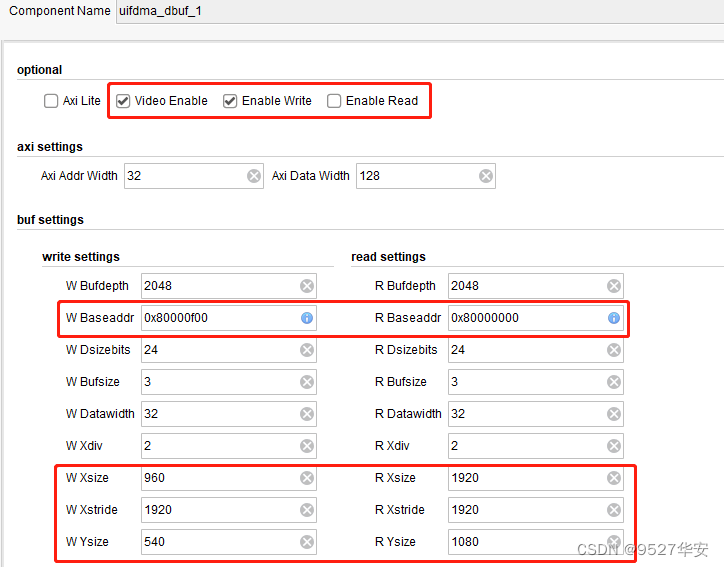

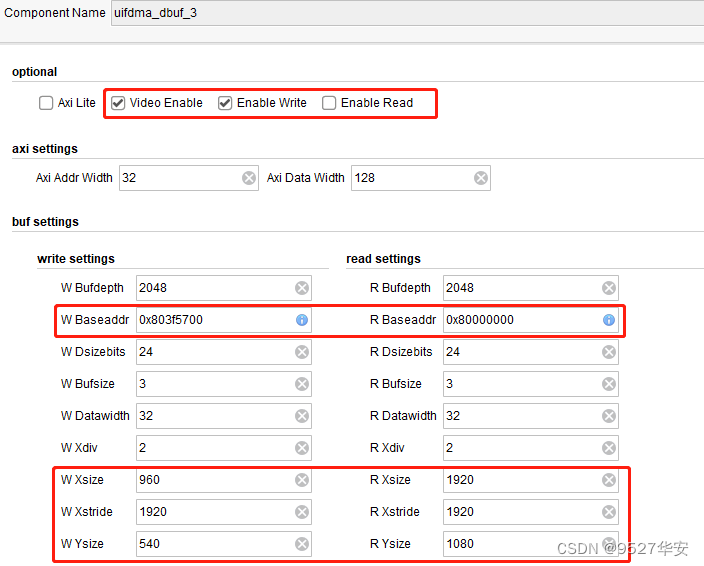

以把 2 个摄像头 CAM0 和 CAM1 输出到同一个显示器上为列,为了把 2 个图像显示到 1 个显示器,首先得搞清楚以下关系:hsize:每 1 行图像实际在内存中占用的有效空间,以 32bit 表示一个像素的时候占用内存大小为 hsize*4;hstride:用于设置每行图像第一个像素的地址,以 32bit 表示一个像素的时候 v_cnt hstride4;vsize:有效的行;因此很容易得出 cam0 的每行第一个像素的地址也是 v_cnt hstride4;同理如果我们需要把 cam1 在 hsize 和 vsize 空间的任何位置显示,我们只要关心 cam1 每一行图像第一个像素的地址,可以用以下公式 v_cnt hstride4+offset;uifdma_dbuf 支持 stride 参数设置,stride 参数可以设置输入数据 X(hsize)方向每一行数据的第一个像素到下一个起始像素的间隔地址,利用 stride 参数可以非常方便地摆放输入视频到内存中的排列方式。关于uifdma_dbuf,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存根据以上铺垫,每路摄像头缓存的基地址如下:CAM0:ADDR_BASE=0x80000000;CAM1:ADDR_BASE=0x80000000+(1920-960)X4;CAM2:ADDR_BASE=0x80000000+(1080-540)X1920X4;CAM3:ADDR_BASE=0x80000000+(1080-540)X1920X4+(1920-960)X4;地址设置完毕后基本就完事儿了; uifdma_dbuf配置如下:

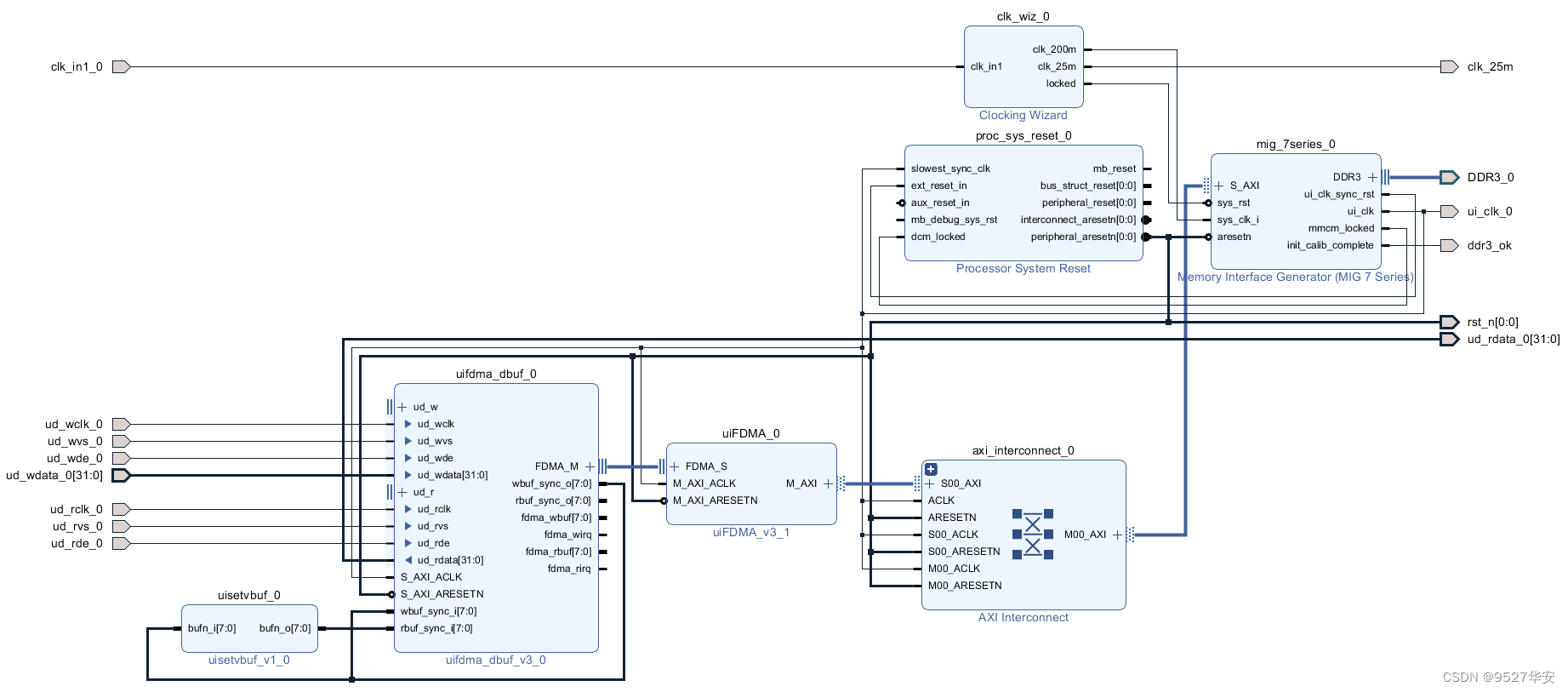

uifdma_dbuf配置如下: 工程代码架构如下:

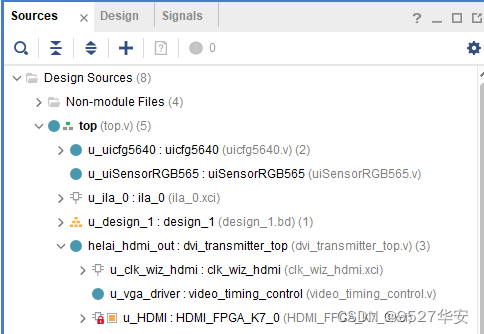

工程代码架构如下:

这是使用单路OV5640摄像头采集数据复制2路,以模拟2路输入;2个uifdma_dbuf配置如下:

这是使用单路OV5640摄像头采集数据复制2路,以模拟2路输入;2个uifdma_dbuf配置如下:

工程代码架构如下:

工程代码架构如下: 3个uifdma_dbuf配置如下:

3个uifdma_dbuf配置如下:

工程代码架构如下:

工程代码架构如下: 4个uifdma_dbuf配置如下:

4个uifdma_dbuf配置如下: 工程代码架构如下:

工程代码架构如下: 工程1:单路OV5640输出如下:

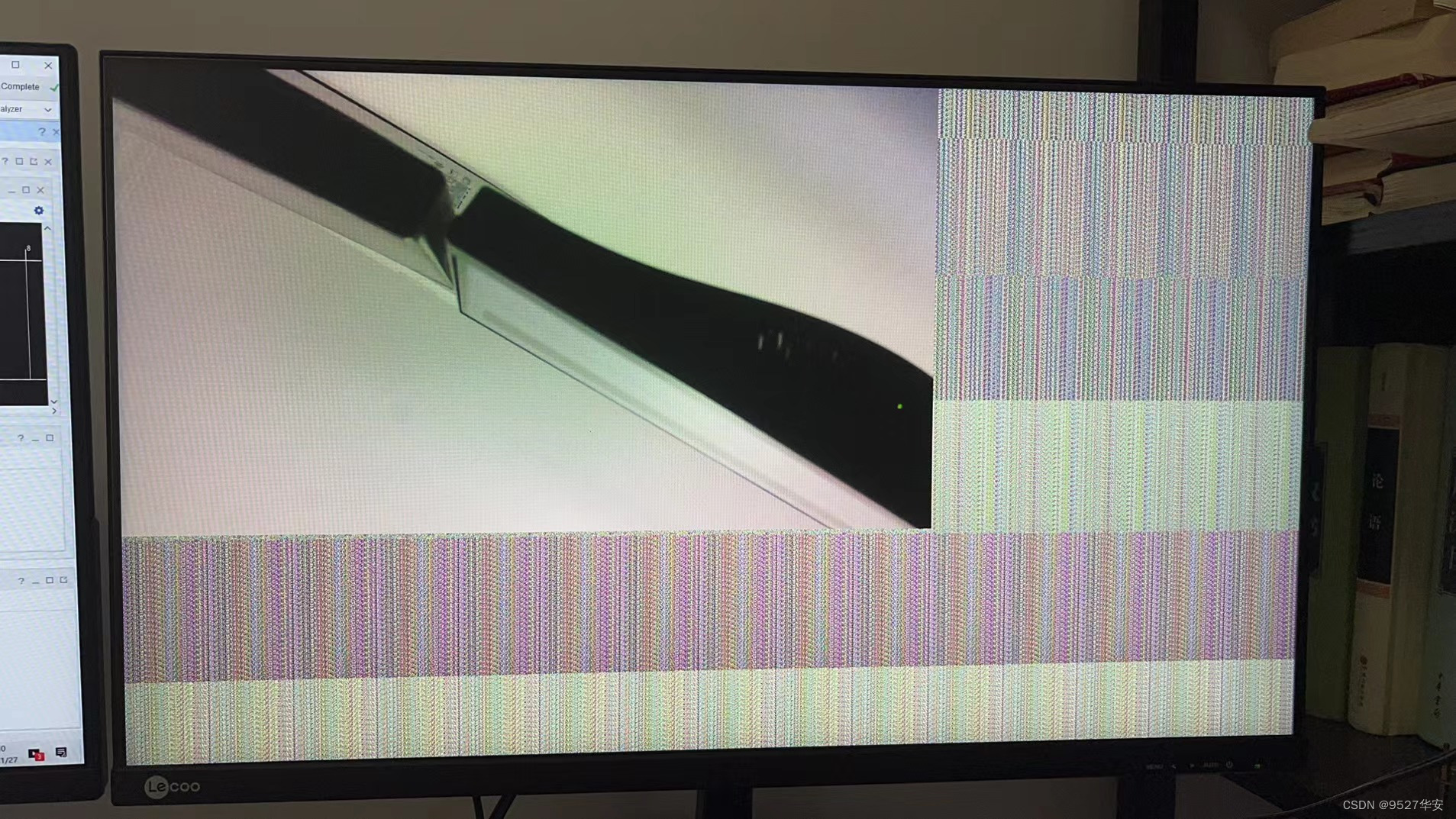

工程1:单路OV5640输出如下: 工程2:2路OV5640输出如下:

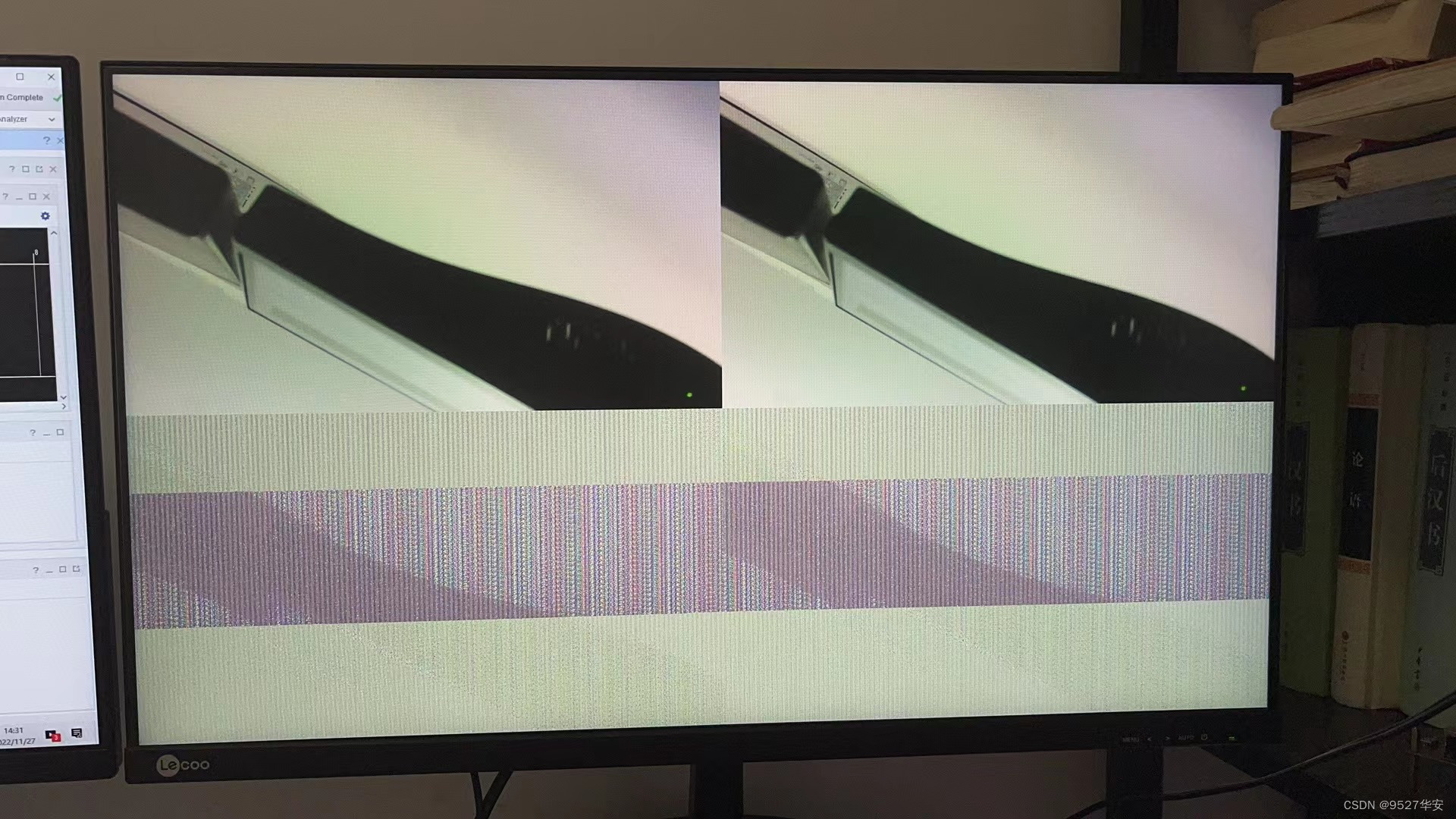

工程2:2路OV5640输出如下: 工程3:3路OV5640输出如下:

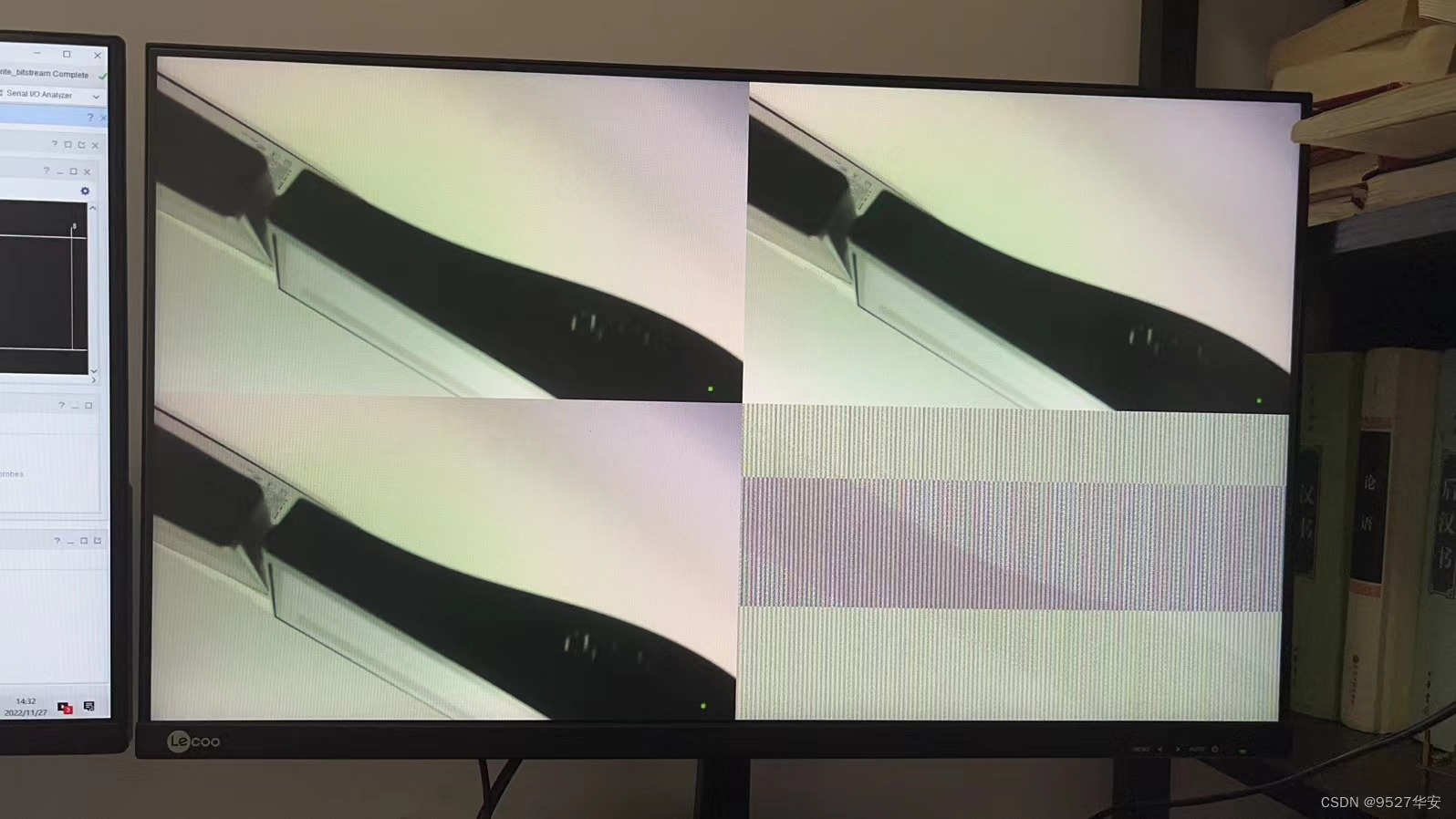

工程3:3路OV5640输出如下: 工程4:4路OV5640输出如下:

工程4:4路OV5640输出如下:

资料如下:

资料如下: