编译码器设计 |

您所在的位置:网站首页 › 8线—3线优先编码器的输入为 › 编译码器设计 |

编译码器设计

|

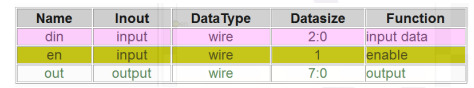

通过设计简单的编译码器实现对数据的转换。常见的编码方式有格雷码,BCD 码和 8-3线编码器,16-4 线编码器等。本次设计以 8-3 线优先编码和 3-8 线译码器作为例子,进行数据的编译码设计。 先来理理设计原理 优先编码器是将多个二进制输入压缩成更少数目输出的电路算法。优先编码器常用于处理最高优先级请求时控制中断请求。8-3 线编码器是将输入为 8 比特的数据以 3 比特的方式描述出来。8 根输入线路中每次只有一个线路为高电平,其余为低电平。相反,3-8 译码器 是用 8 根线对输入的 3 根线数据进行电平转换。 (3)保存。点击工具栏或者点击菜单“File”中的下拉菜单“Saveas”,将模型另存到一个文件夹中。 (4)编译。在工具栏点击 或者点击菜单“Build”的下拉菜“Compile”,执行代码检查。如果有错误,会在输出窗口中显示。 第二步: 译码器模型设计 (1)新建一个模型命名为 decoder,类型为 module,同时引脚设置为 2 输入 1 输出。每个引脚的属性和名称进行对应的修改。 |

【本文地址】

今日新闻 |

推荐新闻 |

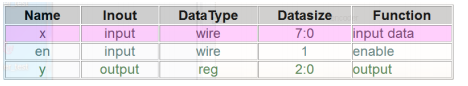

用Robei软件的基本设计流程: 第一步:编码器模型设计 (1)新建一个模型命名为 encoder,类型为 module,同时引脚设置为 2 输入 1 输出。每个引脚的属性和名称参照

用Robei软件的基本设计流程: 第一步:编码器模型设计 (1)新建一个模型命名为 encoder,类型为 module,同时引脚设置为 2 输入 1 输出。每个引脚的属性和名称参照  Robei界面图:

Robei界面图:  (2)添加代码。点击模型下方的 Code添加代码。

(2)添加代码。点击模型下方的 Code添加代码。  在代码设计区内输入以下 Verilog 代码:

在代码设计区内输入以下 Verilog 代码:

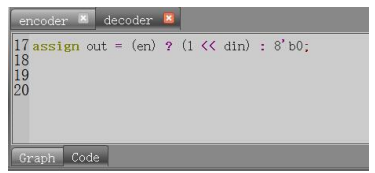

3)添加代码。点击模型下方的 Code添加代码

3)添加代码。点击模型下方的 Code添加代码  在代码设计区内输入以下 Verilog 代码:

在代码设计区内输入以下 Verilog 代码: